(54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| Устройство для защиты от ошибок | 1972 |

|

SU503276A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ СОСТОЯНИЯ И УПРАВЛЕНИЯ КАНАЛАМИ И ТЕХНИЧЕСКИМИ СРЕДСТВАМИ В СИМПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1991 |

|

RU2007878C1 |

| Устройство синхронизации по циклам | 1975 |

|

SU544160A1 |

| Устройство для декодирования циклических кодов | 1975 |

|

SU554626A2 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

| Устройство защиты от ошибок | 1987 |

|

SU1478362A2 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство групповой тактовой синхронизации | 1982 |

|

SU1022325A2 |

I

Изобретение относится к радиотехнике.

Известно устройство для передачи дискретной информации, содержащее последовательно соединенные блок защиты от ошибок и канальный приемо-передатчик,к соответствую-щему входу которого подключен первый выход блока коммутации, второй выходкоторюго соединен со входом анализатора уровня сигналов, а выход канального приемо-передатчика подключен ко входу блока защиты от

О1Ш1бОК 1 .

Однако в известном устройстве недостаточна пропускная способность.

Цель изобретения - повьпиение пропускной способности.

Для достижения поставленной цели в,устройство Ш1Я передачи дискретной информации, содержащее последовательно соединенные блок защиты от oum6oj и канальный приемо-передагчик, к соо1 етствующему входу KOTOfHSro подключен первый выход блока коммутации, второй ьыход ко1О}юго соединен со входом анализатора урювня сигналов, а выход канального приеме-передат чйка подключен ко вхойу

блока защиты от оцгибок, введены делитель и последовательно соединенные реверсивный счетчик и элемент И, второй вход и вь1ход которого соединены соответственно с выходом анализатора уровня сигналов и входом блока коммутации, при этом дополнительные выходы блока защиты от ошибок подключены ко входам реверсивного счетчика и делителя, выход которого соединен д соответствующим входом реверсивного счетчика.

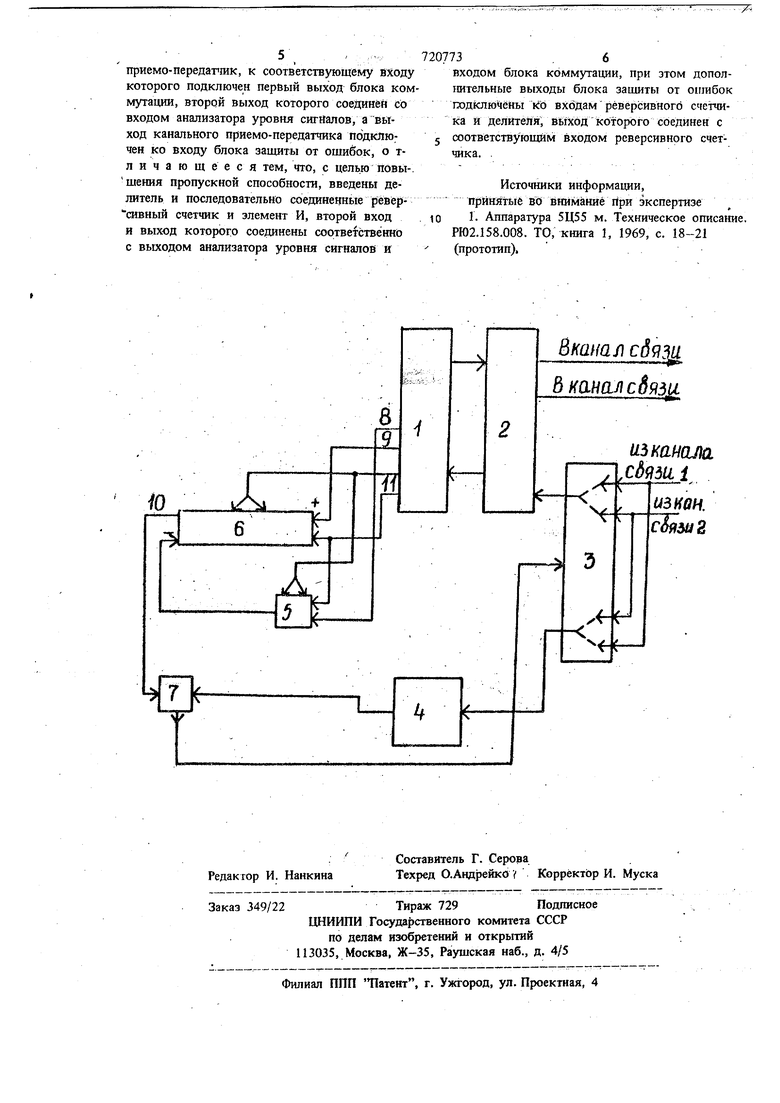

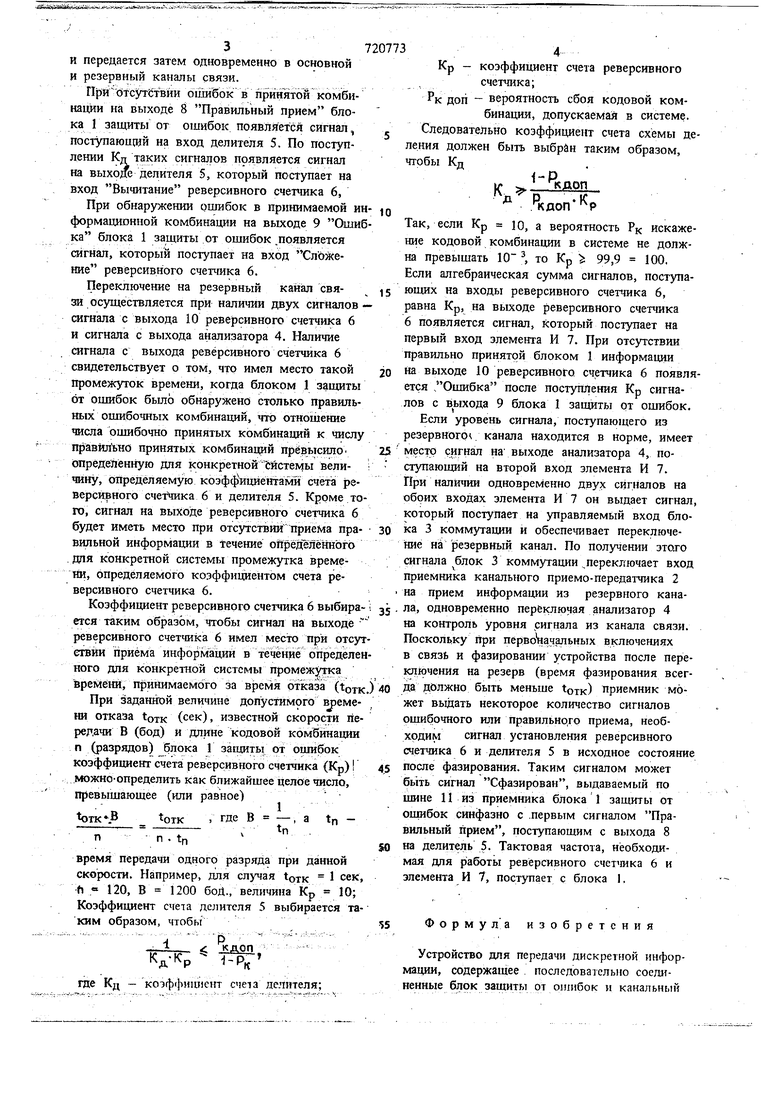

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство содержит блрк 1 защиты от ошибок, канальный приемо-передатчик 2, блок 3 коммутации, ангШизатрр 4 уровня сигналов, делитель 5, реверсивный счетчик 6, элемент И 7.. .

Устройство работает следующим образом.

Информаш1я, поступившая от источника, кодируется в передающей части блока 1 заOщиты от ошибок и поступает в передающую часть канального приемо-передагчика 2, где преобразуется в вн,ч, удобный для перелячи по телефонному каналу связи (модулируется 3. и передается затем одновременно в основной и резервный каналы связи. При отсутствии ошибок в принятой комбинации на выходе 8 Правильный прием блока 1 защиты от ошибок появляется сигнал, поступающий на вход делителя 5. По поступлении Кп таких сигналов прявляется сигнал на выходе делителя 5, который поступает на вход Вычитание реверсивного счетчика 6, При обнаружении ошибок в принимаемой и формаципнной комбинации на выходе 9 Оши ка блока 1 защиты от ощибок .появляется сигнал, который поступает на вход Сложение реверсивного счетчика 6. Переключение на резервный канал связи осуществляется при наличии двух сигналов - сигнала с выхода 10 реверсивного счетчика 6 и сигнала с выхода анализатора 4. Наличие сигнала с выхода реверсивного счетчика 6 свидетельствует о том, что имел место такой промежуток времени, когда блоком 1 защиты от ощибок было обнаружено столько правильных ошибочных комбинаций, что отношение числа ошибочно принятых комбинаций к числу правйльно принятых комбинащй прёвь1силО определённую для к:онкретной Системы величину, определяемую коэф4)Ицйентамй счёта реверсивного счетчика 6 и делителя 5. Кроме того, сигнал на выходе реверсивного счетчика 6 будет иметь место при отсутствии приема правильной информации в течение определенного .для конкретной системы промежутка времеЮ1, определяемого коэффидаентом счета реверсивного счетчика 6. Коэффициент реверсивного счетчика 6 выбирается таким образом, чтобы сигнал на выходе реверсивного счетчика 6 имел место при отсутствйи приёма информации в течение определенного для конкретной системы промежутка BpeMesHH, принимаемого за время отказа (toxK. При заданной величине допустимого времени отказа tojK (сек), известной скорости lieредачи В (бод) и длине кодовой комбинации п (разрядов) блока 1 защиты от ошибок коэффициент счета реверсивного счетчика (Кр) можно-определить как ближайшее целое число, превышающее (или равное) где В -, а . tn . время передачи одного разряда при данной скорости. Например, для случая IOTK 1 сек, h 120, В 1200 бод., величина Кр 10; Коэффициент счета делителя 5 выбирается таким образом, чтобы Р. где Кд - КОЭФФИШ1СНТ счета делителя;

равна Кр, на выходе реверсивного счетчика 6 появляется сигнал, который поступает на первый вход элемента И 7. При отсутствии правильно принятой блоком 1 информации

на выходе 10 реверсивного счетчика 6 появляется .Ошибка после поступления Кр сигналов с выхода 9 блока 1 защиты от ошибок.

Если уровень сигнала, поступающего из резервного. канала находится в норме, имеет

место сигнал на выходе анализатора 4, поступающий на второй вход элемента И 7. При наличии одновременно двух сигналов на обоих входах элемента И 7 он выдает сигнал, который поступает на управляемый вход блоКр - коэффициент счета реверсивного счетчика; РК доп - вероятность сбоя кодовой комбинации, допускаемая в системе. Следовательно коэффициент счета схемы деления должен быть выбрйн таким образом, чтобы Кп )-р, д кдоп р Так, если Кр Ю, а вероятность РК искажение кодовой комбинации в системе не должна превышать 10 , то Кр ; 99,9 100, Если алгебраическая сумма сигналов, поступающих на входы реверсивного счетчика 6, ка 3 коммутации и обеспечивает переключение на резервный канал. По получении этого сигнала блок 3 коммутации .переключает вход приемника канального приемо-передатчика 2 на прием информации из резервного кана з одновременно переключая анализатор 4 на контроль уровня сигнала из канала связи, Поскольку при первоначальных включениях в связь и фазировании устройства после перекл1рчения на резерв (время фазирования всегда должно быть меньше IOTK) приемник м6жет выдать некоторое количество сигналов ошибочного или правильного приема, необходим сигнал установления реверсивного счетчика 6 и делителя 5 в исходное состояние после фазирования. Таким сигналом может «.:. „. /-д,. .-. - бьгть сигнал Сфазирован, выдаваемый по шине 11 из приемника блока 1 защиты от ощибок синфазно с .первым сигналом Правильный прием, поступающим с выхода 8 на делитель 5. Тактовая частота, необходимая для работы реверсивного счетчика 6 и элемента И Т, поступает с блока 1. Формула изобретения Устройство для передачи дискретной информации, содержащее . последовательно соединенные блок защиты от ошибок и канальный

приемо-передагшк, к соответствующему входу которого подключен первый выход блока ком мутации, второй выход которого соединен со входом анализатора уровня сигйалов, а выход канального приемо-передатчика подклю; чен ко входу блока защиты от ошибок, о тличающееся тем, что, с целью повы-.

щения пропускной способности, введены делитель и последовательно соединенные рёвер-сивный счетчик и элемент И, второй вход и выход которого соединены соответственно с выходом анализатора уровня сигналов и

20773,6

входом блока коммутации, при этом дополнительные выходы блока зашиты от ошибок гх)д1слючены ко входам реверсивного счетчика И делителя, вЫход которого соединен с 5 соответствующим входом реверсивного счетчика. .

Источники информации, прйнйтые во внимание йри экспертизе 10 J- Аппаратура 5Ц55 м. Техническое описание. РЮ2.158.008. ТО, книга 1, 1969, с. 18-21 (прототип).

вканал сдящ b наналс8я5

и. канала сдяди

изнвн.

Авторы

Даты

1980-03-05—Публикация

1976-10-04—Подача