w

26

N)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1983 |

|

SU1095183A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Запоминающее устройство с исправлением ошибок | 1986 |

|

SU1363303A1 |

| Запоминающее устройство с исправлением ошибок | 1987 |

|

SU1585835A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах переработки и передачи дискретной информации. Цель изобретения - расширение функ- .j гг 1 Л циональных возможностей за счет коррекции t-кратных ошибок. Устройство содержит регистр 1 приемных элементов, группу 2 сумматоров по модулю два, дешифратор 3, группу 4 элементов ИЛИ, элементы ИЛИ 5,6 и 18, элементы ИЛИ-НЕ 7 и 8, элементы И 9,10, 16 и 17, группу 11 элементов И, регистр 12 сдвига, элемент НЕ 13, (t-2) блоков 14 коррекции, блок 15 фиксации кратности ошибок, элементы 19 и 20 задержки, информационные входы 21 и выходы 22, управляющий вход 23, выход 24 Готовность, выход 25 однократной ошибки, выходы 26 с двукратной по t-кратную ошибки. 2 з,п. ф-лы, 2 ил. (О ел ш 4 IN9 СП 00 4 СО

cpvsi

Изобретение относится к вычислительной технике, может быть использовано в устройствах переработку и передачи дискретной информации и является усовершенствованием устройства по авт.ев, № 1095183.

Цель изобретения - расширение функциональных возможностей устройства за счет коррекции t-кратных ошибок.

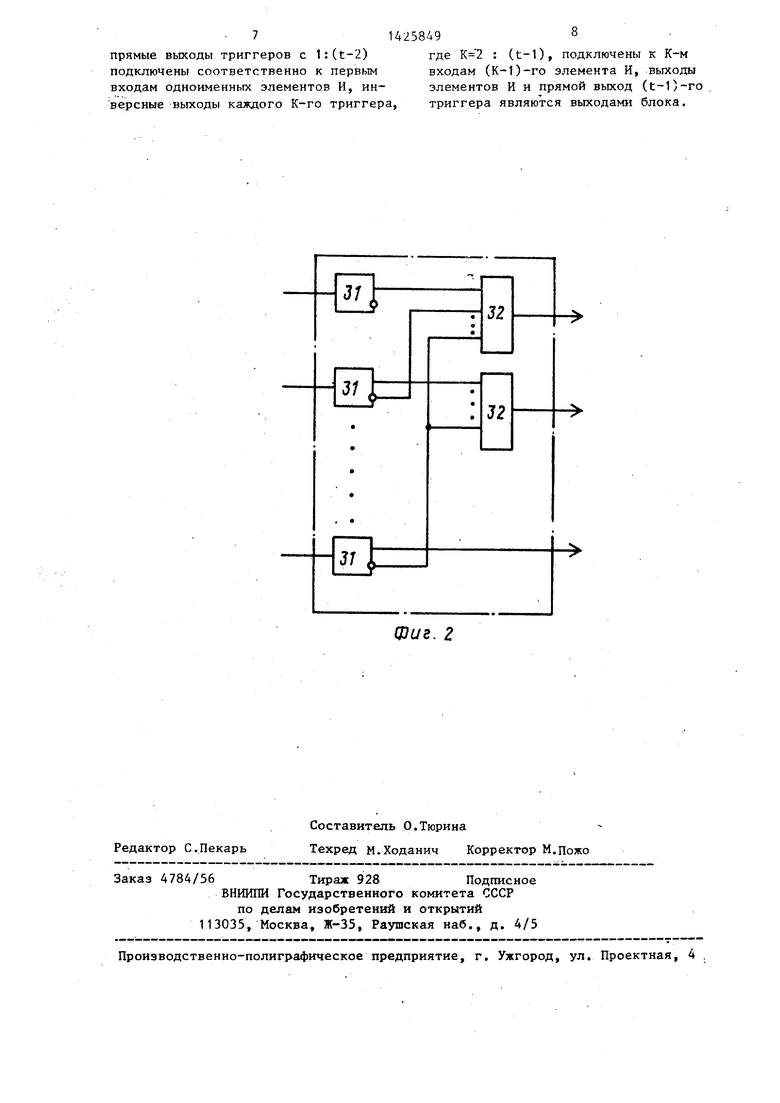

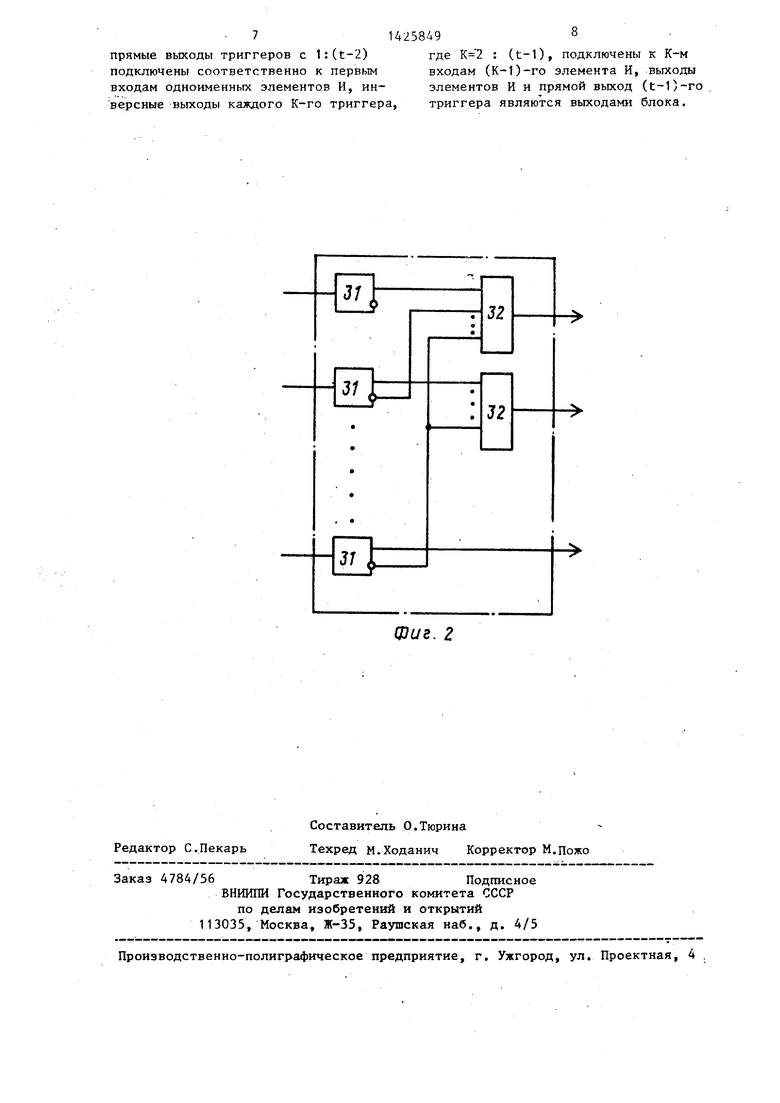

На фиг. 1 приведена структурная схема устройства; на фиг.2 - блок фиксации кратности ошибок.

Устройство содержит регистр 1 приемных элементов, группу 2 сумматоров по модулю два, дешифратор 3, группу 4 элементов ИЛИ, первый 5 и второй 6 элементы ИЛИ, первый 7 и второй 8 элементы ИЛИ-НЕ, первый 9 и второй 10 элементы И, группу 11 элементов И, регистр 12 сдвига, элемент НЕ 13, (t-2) блоков 14 коррекции, блок 15 фиксации кратности ошибок, третий

16 и четвертый 17 элементы И, третий 25 и элемент 19 задержки выдается на

элемент ИЛИ 18, первый 19 -и второй 20 элементы задержки, информационные входы 21, информационные выходы 22, управляющий вход 23, выход 24 Готовность, выход 25 однократной ошиб- ЗО гистре 1 производится исправление

ки, выходы 26 с двукратной по t-крат ную ошибки.

Каждьй блок 14 коррекции содержит дешифратор 27, элемент И 28, счетчик 29 импульсов, элемент ИЛИ 30. Блок 15 фиксации кратности ошибок содержит () триггеров 31 и (t-2) элементов И 32.

Устройство работает следующим образом.

В исходном состоянии регистр 1 приемных элементов и счетчики 29 обнулены. На входы 21 поступает де- кодируемое слово и записывается в регистр 1. Далее предполагается, что поступившее слово закодировано с помощью избыточного кода, поз1воляющего исправлять t-кратные ошибки. После приема слова в регистр 1 на управляющий вход 23 устройства подается единичный импульс, свидетельствующий о начале декодирования слова. По этому сигналу производится обнуление регистра 12 сдвига.

Рассмотрим процесс функционирования устройства при различных ситуа- циях, которые могут возникнуть при декодировании слова.

Пусть в принятом слове нет ошибок. При этом записанное в регистр 1 слово без изменений через группу

2 сумматоров по модулю два поступает на входы дешифратора 3. На одном из выходов дешифратора 3, которые соединены с входами элемента ИЛИ 5, имеется единичный уровень. Этот единичный сигнал поступает на вход 24 и свидетельствует о том, что с информационных выходов 22 устройства можно считьшать декодированное слово. Одновременно этот сигнал поступает.на вход элемента НЕ 13. За счет этого элементы И 16 и 17 закрыты. На выходах 25 и 26 в этой ситуации код О.

Если в принятом слове одна ошибка, единичный сигнал с входа 23 устройства поступает на элемент И 16 и открывает его, так как с выхода элемента НЕ 13 поступает код 1. Единичный сигнал через элемент ИЛИ 18

вход группы 11 элементов И. По этому сигналу открывается один из элементов И 11, соответствующий разряду, принятому с искажением, и в ре

искаженного разряда путем инвертирования . На одном из выходов дешифратора 3, соединенном с входами элемента ИЛИ 5, появляется единичный уровень, который выдается на выход 24, свидетельствуя об окончании декодирования слова. Одновременно на выходе элемента НЕ 13 появляется код О, который запрещает работу элемента и 16. Декодированное слово выдается на выходы 22 устройства.

Пусть в принятом слове две ошибки. В этом случае ни на одном выхо- де дешифратора 3 не будет единичного сигнала. На выходах элементов ИЛИ 4- 6 код О. На вьпсоде элемента ИЛИ- НЕ 7 и, следовательно, на первом входе блока 15 фиксации кратности ошибок код 1, который преобразуется в сигнал, свидетельствующий о наличии двойной ошибки. Регистр 12 сдвига предварительно обнулен сигналом с входа 23. Поэтому на выходе элемента ИЛИ-НЕ 8 код 1 и единич- ньй уровень с выхода элемента ИЛИ- НЕ 7 открьшает элемент И 9, и производится запись единицы в младший разряд регистра 12 сдвига.

Далее рассмотрим два случая; одна из ошибок возникла в младшем разряде принятого слова; в младшем разряде принятого слова нет ошибок. Младшие разряды принятого слова располагаются в разрядах регистра 1, показанных справа. В первом случае появление 1 на выходе младшего разряда регистра 12 сдвига приводит к тому, что младший искаженный разряд принятого слова с помощью группы сумматоров по модулю два инвертируется. При этом на выходе группы 2 сумматоров по модулю два появляется слово, содержащее всего лишь одну ошибку. Поэтому на соответствующем выходе дешифратора 3 появляется код 1, который поступает на выход одного из элементов 4 ИЛИ. С появлением кода 1 на выходе элемента 19 открывается один из элементов И 11, и вторая ошибка исправляется. На одном выходе дешифратора 3, средилю два появляется слово, содержащее одиночную ошибку. Коррекция одиночной ошибки производится, как и в предыдущем случае. Отличие заключае ся лишь в том, что единичный сигнал 15 на первом выходе элемента 19 задерж ки появляется за счет цепи обратной связи через открытый элемент И 17. Если ошибки содержатся не,в первом и втором разрядах а в старших, то за счет подачи на выход элемента 20 соответствующего количества единичных сигналов производится сдвиг 1 в регистре 12 на требуемое число ра рядов.. Исправленное слово поступает

. ненном с входами элемента ИЛИ 5, по- 25 на выход 22 устройства, при этом на является единичный сигнал, который проходит на выход элемента ИЛИ 5 и свидетельствует об окончании декодирования принятого слова. Одновревыходе 24-код 1, св1 цетельствующий об окончании декодирования слова.

Пусть в принятом слове ошибка кратности больше двух. В этом случа сдвиг 1 в регистре 12 сдвига производится до конца. После чего 1 с выхода регистра 12 сдвига поступает вместе с сигналом с выхода эле мента 20 на элемент И 28 первого блока 14 коррекции и с его выхода на счетчик 29, устанавливая его в положение два. На выходе дешифратора 27 первого блока 14 коррекции, подключенного к счетчику 29, появляется единичный сигнал. Тот же сигнал со счетчика 29 поступает и на элемент ИЛИ 30 и с него на блок 15 фиксации кратности ошибки, свидетельствуя о наличии трехкратной ошибки.

менно код О с выхода элемента НЕ 13 Поступает на вход элементов И 16 и 12 и запрещает их работу. Кроме того, код О с выхода элемента ИЛИ-НЕ 7 поступает на вход элемента И 10 и запрещает прохождение единичного сигнала с выхода элемента 20 в шину синхроимпульсов сдвига регистра 12. Исправленное слово выдается на выходы 22 устройства. При этом младший разряд слова корректируется за счет наличия 1 в младшем разряде регистра 12, а другой искаженный, разряд проинвертирован за счет подачи кода 1 на соответствующий триггер регистра 1.

Рассмотрим теперь случай, когда при двойной ошибке в младшем разряде принятого слова нет ошибок. В этом случае появление 1 в младшем разряде регистра 12 не приводит к появлению ее на выходе группы 2 сумматоров по модулю два. Следовательно, на всех выходах дешифратора 3 код О. Единичный сигнал с выхода элемента ИЛИ-НЕ 7 разрешает прохождение кода 1 с выхода элемента 20. По этому сигналу производится сдвиг на один разряд влево содержимого регист ра 12. Так как на выходе элемента

5849

ИЛИ-НЕ 8 код О

то элемент И 9 закрыт. Следовательно, в регистре 12 код 1 будет только во втором разряде. Если одна из ошибок в принятом слове возникла во втором разряде, то с появлением 1 в соответствующем разряде регистра 12 на выходе группы 2 сумматоров по моду

лю два появляется слово, содержащее одиночную ошибку. Коррекция одиночной ошибки производится, как и в предыдущем случае. Отличие заключается лишь в том, что единичный сигнал на первом выходе элемента 19 задержки появляется за счет цепи обратной связи через открытый элемент И 17. Если ошибки содержатся не,в первом и втором разрядах а в старших, то за счет подачи на выход элемента 20 соответствующего количества единичных сигналов производится сдвиг 1 в регистре 12 на требуемое число разрядов.. Исправленное слово поступает

на выход 22 устройства, при этом на

5 на выход 22 устройства, при этом на

0

5

0

5

0

5

выходе 24-код 1, св1 цетельствующий об окончании декодирования слова.

Пусть в принятом слове ошибка кратности больше двух. В этом случае сдвиг 1 в регистре 12 сдвига производится до конца. После чего 1 с выхода регистра 12 сдвига поступает вместе с сигналом с выхода элемента 20 на элемент И 28 первого блока 14 коррекции и с его выхода на счетчик 29, устанавливая его в положение два. На выходе дешифратора 27 первого блока 14 коррекции, подключенного к счетчику 29, появляется единичный сигнал. Тот же сигнал со счетчика 29 поступает и на элемент ИЛИ 30 и с него на блок 15 фиксации кратности ошибки, свидетельствуя о наличии трехкратной ошибки.

Выходы дешифратора 27 первого блока 14 коррекции соединены с входами сумматоров 2 по модулю два-. Далее происходит запись 1 в лшад- ший разряд регистра 12 сдвига. Если две ошибки из трех находятся в первом и втором разрядах принятого слова, то на выходе группы 2 сумматоров по модулю два получается слово, содержащее всего оДну ошибку. Такая J ошибка исправляется, как бьшо рассмотрено ранее.

Если же ошибки не в первом и втором разрядах, то производится переш

мещение 1 в регистре 12 сдвига до - тех пор, пока не будет исправлена трехкратная ошибка. Если же она не будет исправлена, то появление 1 на выходе регистра 12 сдвига приводит к увеличению содержимого счетчика 29 первого блока 14 на единицу, т.е. на третьем выходе дешифратора 27 появляется единичный сигнал, и поиск ошибочной комбинации продолжается.

При наличии опшбки кратности больше трех 1 пробегает по всем выходам дешифратора 27 первого блока 14 {коррекции, поступая вместе t 1 с выхода элемента 20 задержки на Элемент И 28 второго блока 14 коррекции, и открывает его. При этом содержи- :мое счетчика 29 второго блока 14 коррекции увеличивается на единицу, 1 с выхода дешифратора 27 второй сту- :пени устанавливает счетчик 29 той же ступени в единицу.

Далее производится последовательное перемещение 1 в регистре 12 сдвига. Затем производится смещение на один разряд 1 в дешифраторе 27 первой ступени. После прохождения ее до конца в дешифраторе 27 добавляется 1 в счетчик 29 второй ступени, т.е. происходит перемещение в дешифраторе 27 второй ступени на один разряд. Этот процесс продолжается до тех пор, пока на входах группы 2 сумматоров по модулю два не появится комбинация, соответствующая трехкратной ошибке. Исправление ошибки в последнем четвертом из разрядов производится, как исправление одно-кратной ошибки.

Исправление ошибок большей кратности производится аналогично с помощью последующих ступеней счетчика и дешифраторов. Количество этих ступеней равно t-2. Таким образом, предлагаемое устройство позволяет исправлять ошибки в случае, когда используется корректирующий код определенной мощности.

Сигналы с каждой ступени дешифраторов 27 поступают на входы блока 15 фиксации кратности ошибок и свидетельствуют о кратности ошибки. Выдачу сигнала об ошибке меньшей кратности блокируется. При появлении однократной ошибки после исправления фиксируется именно она.

Таким образом, устройство позволяет корректировать ошибки кратности не более t и выдавать сигналы о крат- ности ошибок.

Формула изобретения

первьм выход каждого блока коррекции, кроме (t -2)-ro, соединен с первым входом последующего блока коррекции, вторые входы блоков коррекции объединены и подключены к выходу второго элемента задержки, вторые выходы каждого j-ro блока коррекции.

где

j 1, (t-2), , п коли

чество символов входного кода, под- ключены к (j+2)-M входам сумматоров по модулю два с (j+1) - (n-j) группы, выход первого элемента ИЛИ-НЕ и третьи выходы блоков коррекции подключены к входам блока фиксации кратности ошибок, соответственно с первого по (t-1)-й, выходы узла фиксации кратности ошибок являются выходами

кратности ошибок устройства. I.

блока, а выход подключен к первому входу счетчика, выходы которого подключены к соответствующим входам элемента ИЛИ и дешифратора, выход которого подключен к второму входу

счетчика импульсов и является первьм выходом блока, группа выходов дещифратора и выход элемента 11ПИ являются соответственно вторыми и третьим в ыходами блока.

71425849«

прямые выходы триггеров с 1:(t-2) где : (t-1), подключены к К-м подключены соответственно к первым входам (К-1)-го элемента И, выходы входам одноименньгх элементов И, ин- элементов И и прямой выход (t-l)-ro версные выходы каждого К-го триггера, триггера являются выходами блока.

Фиг. 2

| Устройство для исправления ошибок | 1983 |

|

SU1095183A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

Авторы

Даты

1988-09-23—Публикация

1985-11-10—Подача