Изобретение относится к автоматике и вычислительной технике, в частности к устройствам одно- и двукратного дифференцирования по времени частотно-импульсных сигналов.

Известно устройство для дифференцирования частотно-импульсных сигналов, содержащее блок управления, счетчик, делитель частоты, генератор опорной частоты, три регистра памяти, три управляемых делителя частоты, переключательный блок и блок вычитания импульсов 1.

Известно также частотно-импульсное дифференцирующее устройство, содержащее блок управления, генератор опорной частоты, счетчики, регистры памяти, распределитель импульсов, блок вычитания, группы элементов И и ИЛИ и блоки сложения-вьрштания 2.

Недостатками известных устройств являются ограниченные функциональные возможности, т. е. невозможность формировать одновременно с первой производной еще и вторую производную, по времени от частотно-импульсных сигналов.

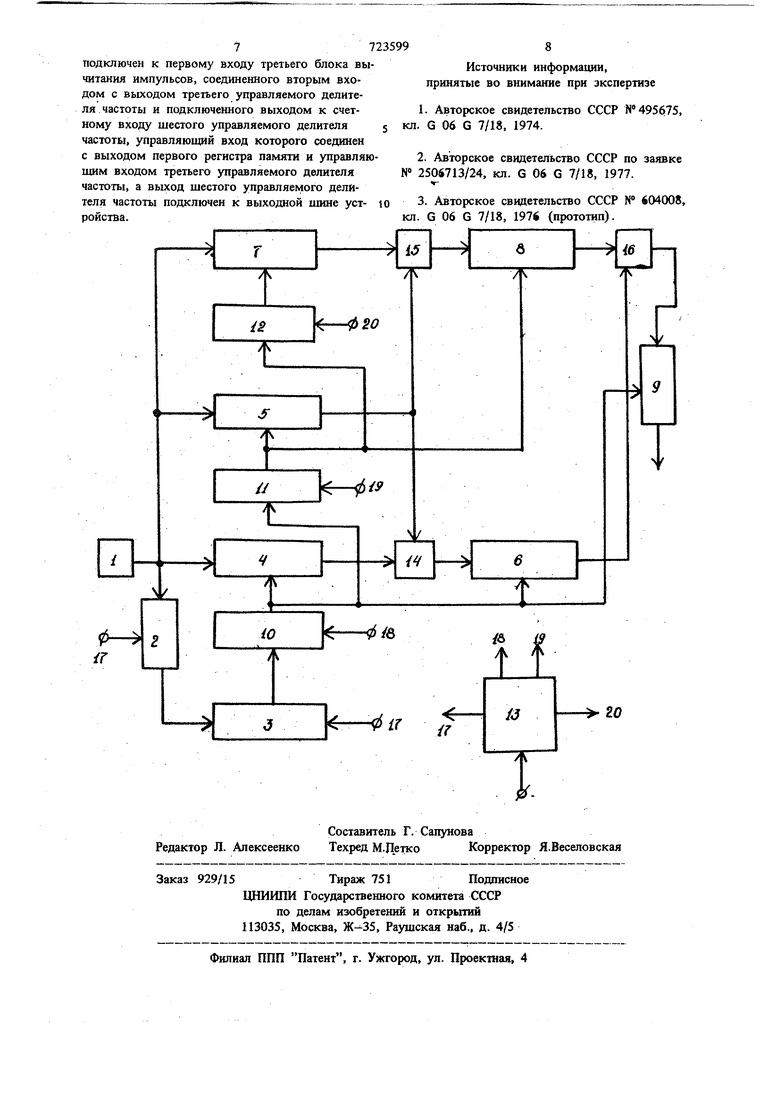

Наиболее близким к предлагаемому является устройство для дифференцирования частотноимпульсных сигналов, ,/х)держащее три регистра памяти, информационный вход первого из которых соединен с выходом счетчика, подключенного счетным входом через делитель частоты к выходу генератора опорной частоты и к счетным входам первого и второго j управляемых делителей частоты, а выход первого регистра памяти соединен с управляющим входом первого управляемого делителя частоты к информационным входом второго регистра памяти, выход которого подключен к управляющему входу второго управляемого делителя частоты, соединенного выходом с первым входом первого блока вычитания 1{мпульсов,выход которого подключен к счетному входу третьего управляемого делителя частоты, а второй вход соединен с выходом первого управляемого делителя частоты, причем входы управления записью регистров памяти и обнуляюиие входы счетчика и делителя частоты подключены к соответствующим выходам блока управления, соединенного входом с входной шиной устройства, тфичем выход счетчика подключен к информационному входу третьего регистра памяти, соединенного выходом с управляющим входом третьего управляемого делителя частоты, выход которого подключен к выходной шине устройства 3. Это устройство также не обеспечивает определения второй производной по времени. Цель изобретения - расширение функциональных возможностей устройства. С этой целью в устройство для дифферен(цирования частотно-импульсных сигналов, содержащее три регистра памяти, информационный вход первого из которых соединен с выходом счетчика, подключенного счетным входом через делитель частоты к выходу генератора опорной, частоты и к счетным входам первого и второго управляемых делителей частоты, а выход первого регистра памяти соединен с управляющим входом первого управляемого делителя частоты и информационным входом второго регистра 20 и 7. памяти, выход которого подключен к управляю щему входу второго управляемого делителя частоты, соединенного выходом с первым входом первого блока вычитания импульсов, выход которого подключен к счетному входу третьего управляемого делителя частоты, а второй вход соединен с выходом первого управляе мого делителя частоты, причем входы управления записью регистров памяти и обнуляющие входы счетчика и делителя частоты подключены к соответствующим выходам блока управления, соединенного входом с входной шиной устройства, дополнительно введены четвертый пятый, шестой управляемые делители частоть и второй и третий блоки вычитания импульсов, причем выход четвертого управляемого делителя частоты, подключенного счетным входом к выходу генератора опорной частоты и соединенного управляющим входом с выходом третьего регистра памяти, подключен к первому входу второго блока вычитания импульсов, соединенного вторым входом с выходом второго уп равляемого делителя частоты и подключенного выходом к счетному входу пятого управляемого делителя частоты, управляющий вход которо го соединен с выходом второго регистра памяти и информационным входом третьего регистра памяти, а выход пятого управляемого делитieля частоты подключен к первому входу треть его блока вькитания импульсов, соединенного вторым входом с выходом третьего управляемого делителя частоты и подключенного выходом к счетному входу шестого управляемого делителя частоты, управляющий вход которого соединен с выходом первого регистра памяти И с управляющим входом третьего управляемого делителя частоты, а выход шестого управляе мого делителя частоты подключен к выходной ашне устройства. 7 94 На чертеже изображена блок-схема устройства для дифференцирования частотно-импульсных сигналов. Устройство содержит генератор 1 опорной частоты, делитель 2 частоты, счетчи: 3, первый второй, третий, четвертый, пятый и щестой управляемые делители 4-9 частоты, первый, второй и третий регистры 10-12 памяти, блок 13 управления, первый, второй и третий блоки 14-16 вычитания импульсов. Вход блока 13 управления соединен с входной шиной устрюйства. Вы|ХОды 17-20 блока 13 управления подключены соответственно к входам обнуления делителя 2 и счетчика 3 и входам управления записью регистров 10-12 памяти. Выход генератора 1 подключен через делитель 2 частоты к счетному входу счетчика 3, а также соединен со счетными входами управляемых делителей 4, 5 Вьрсод регистра 10, подключенного информационным входом к выходу счетчика 3, соединен с управляющими входами делителей 4, 6, 9 и с информационным входом регистра 11, выход которого подключен к управляющим входам делителей 5, 8 и к информационному входу регистра 12, соединенного выходом с управляющим входом делителя 7. Входы блока 14 вычитания., подключенного выходом к счетному входу делителя 6, соединены с выходами делителей 4 и 5. Входы блока 15 вычитания соединены с выходами делителей 5 и 7, а выход его подключен к счетному входу делителя 8. Счетный вход делителя 9, соединенного выходом с выходной щиной устройства, подключен к выходу блока 16 вычитания, входы которого соединены с выходами делителей 6 и 8. Устройство работает следующим образом. В блоке 13 управления из последовательности импульсов входного сигнала fj формируются управляющие сигналы, определяющие последовательность работы блоков устройства. С выхода генератора 1 импульсы высокой опорной частоты fo поступают на счетные входы управляемых делителей 4, 5 и 7 частоты и вход делителя 2 частоты. В делителе 2 опорная частота делится на постоянный коэффициент К пересчета. В делителях 4, 5 и 7 опорная частота делится на переменные коэффициенты, записываемые в виде параллельного кода в соответствующие 10, И, 12 регистры памяти. Импульсы с выхода делителя 2 поступают на счетный вход счетчика 3, где они суммируются в промежутке времени, равном текущему периоду гд входного сигнала, формируемому путем подачи на вход 17 обнуления счетчика 3 импульсов -входного сигнала f j. На выходе четчика 3 в момент опроса образуется код. пропорциональный закончившемуся i-му периоду входного сигнала Т, Этот код перед обнулением счетчика 3, по сигналу с выхода 18 блока управления записы вается регистр 10 памяти. Перед записью это го кода в регистр 10 памяти, содержащийся в регистре 10 код , пропорциональный предыдущему периоду , переписывается по сигналу с выхода 19 блока управления в регистр 11 памяти. Соответственно, перед записью этого кода, содержащийся в регистре 11 код , пропорциональный периоду по сигналу с выходу 20 блока управления перепи сывается в регистр 12 памяти. Таким образом после окончания i-ro периода входной частоты в регистре 10 - код N-j. , в регистре 11 - код NJ.. j., а в регистре 12 - код . На выходах управляемых делителей 4, 5 и 7 частоты формируются соответственно частоты, пропорциоиальные мгновенным значениям частот fj, fI н входного сигнала для се редин его периодов Tj, Tj , i-2- выходе блока 14 вычитания образуется разность частот с выхода делителя 4 и выхода делителя 5. Эта .разностная частота в делителе 6 делится на код , записанный в регистре 10 памяти. На выходе делителя 6 образуется частотас -J f lilliztL- о пропорциональная первой производной по времени входного сигнала в i-ом периоде. Знак этой производной определяется знаком разности частот формируемым в блоке 14 вычита ния. В блоке 15 вычитания формируется разность частот с выходов делителей 5 и 7 частоты. Вы ходная частота блока 15 делится в делителе 8 на код N.|-i регистра 11 памяти. На выходе делителя 8 образуется частота , а. /- .- л ., 2. .4i;-i-f -a V Пропорциональная первой производной по.времени входного сигнала в (i-l)-OM периоде. Знак з(той производной определяется знаком р ности частот, формируемым в блоке 15. Частоты с выходов делителей 6 и 8 поступа ют на входы блока 16 вычитания, выходная разностная частота которого делится в делителе 9 частоты на код N.J.J регистра 10 памяти. Частота на выходе делителя S K(i;-fU к ,. пропорциональна второй производной f| по времени входного сигнала в i-ом периоде. Знак этой производной определяется знаком разности частот, формируемым в блоке 16 вычитания. Таким образом, устройство после окончания каждого периода входной частоты, без ухудшения быстродействия, позволяет определять кроме знака и величины первой прюизводной также знак и величину второй производной по времени входного сигнала, т. е. обладает более широкими функциональными возможностями. Формула изобретения Устройство для дифференцирования частотноимпульсных сигналов, содержащее три регистра памяти, информационный вход первого из которых соединен с выходом счетчика, подключенного счетным входом через делитель частоты к выходу генератора опорной частоты и к счетным входам первого и второго управляемых делителей частоты, а выход первого регистра памяти соединен с управляющим входом первого управляемого делителя частоты и информационным входом второго регистра памяти, выход которого подключен к управляющему входу второго управляемого делителя частоты, соединенного выходом с первым входом первого блока вычитания импульсов, выход которого подключен к счетному входу третьего управляемого делителя частоты, а второй вход соединен с выходом первого управляемого делителя частоты.причем входы управления записью регистров памяти и обнуляющие входы счетчика и делителя частоты подключены к соответствующим выходам блока управления, соединенного входом с входной шиной устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него дополнительно введены четвертый, пятый, шестой управляемые делители частоты и второй и третий блоки вычитания импульсов, причем выход четвертого управляемого делителя частоты, подключенного счетным входом к выходу генератора опорной частоты и соединенного управляющим входом с выходом третьего регистра памяти, подключен к первому входу второго, блока вычитания импульсов, соединенного вторым входом с выходом второго управляемого делителя частоты и подключенного выходом к счетному входу пятого управляемого делителя частоты, управляющий вход которого соединен с выходом второго регистра памяти и информационным входом третьего регистра памяти, а выход пятого управляемого делителя частоты

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифференцирования частотно-импульсных сигналов | 1978 |

|

SU742967A1 |

| Устройство для дифференцированиячАСТОТНО-иМпульСНыХ СигНАлОВ | 1979 |

|

SU811281A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1980 |

|

SU894729A1 |

| Устройство для вычисления производной частотно-импульсных сигналов | 1976 |

|

SU734729A1 |

| Устройство для преобразования частоты в код | 1977 |

|

SU696604A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1976 |

|

SU604008A1 |

| Устройство для дифферинцирования частотно-импульсных сигналов | 1975 |

|

SU526916A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Цифровой частотомер | 1975 |

|

SU783701A1 |

| Умножитель частоты импульсов | 1978 |

|

SU780175A1 |

Авторы

Даты

1980-03-25—Публикация

1978-03-01—Подача