I

Изобретение относится к запоминающим устройствам.

Известно устройство, содержащее блок памяти, регистр на триггерах со счетными входами J. . Однако с его помощью невозможно обнаружить отказы типа постоянная единица .

Наиболее близким к изобретению по технической сущности является устройство для контроля постоянной памяти, содержащее блок свертки по модулю два, элемент И-НЕ и триггер, первый вход элемента И-НЕ подключен к одной из управляющих шин, второй - к выходу блока свертки по модулю два. Входы последнего соединены .с входами устройства, первый вход триггера подключен к выходу элемента И-НЕ, бторой - к шине начальной установки, а выходы - к выходам устройства 2 .

Однако в прсжессе работы этого устройства отсутствует возможность контроля правильности считывания программы с выходов блока постоянной памяти. Крометого, для контроля аппаратурной части блока постоянной памяти используются дополнительные комавды.

Целью изобретения является повышение надежности устройства.

.Достигается это тем, что устройство содержит счетный триггер и дополнительный элемент И-НЕ, причем счетный вход счетного триггера подключен к выходу блока свертки по модулю два, управляющий вход - к шине начальной установки, а выход - к первому входу дополнительногч элемента И-НЕ, второй вход которого соединен с другой управляквдей шинсй, а выход дополнительного Элемента И-НЕ подключен к третьему входу триггера.

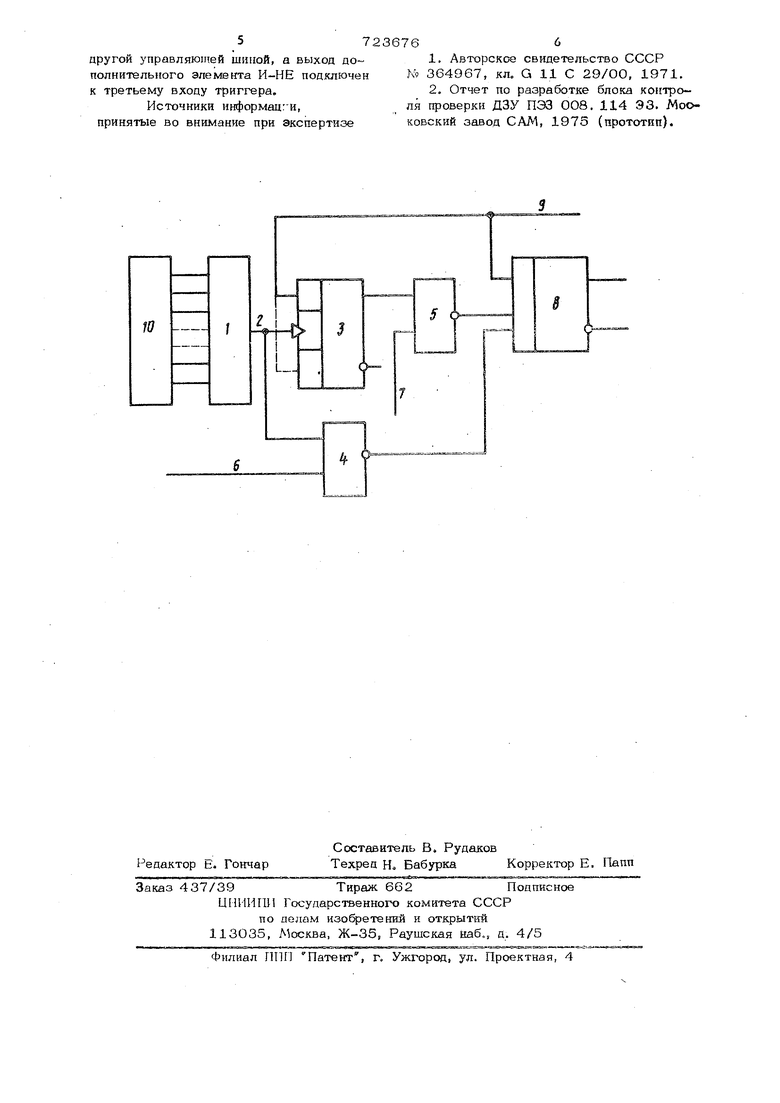

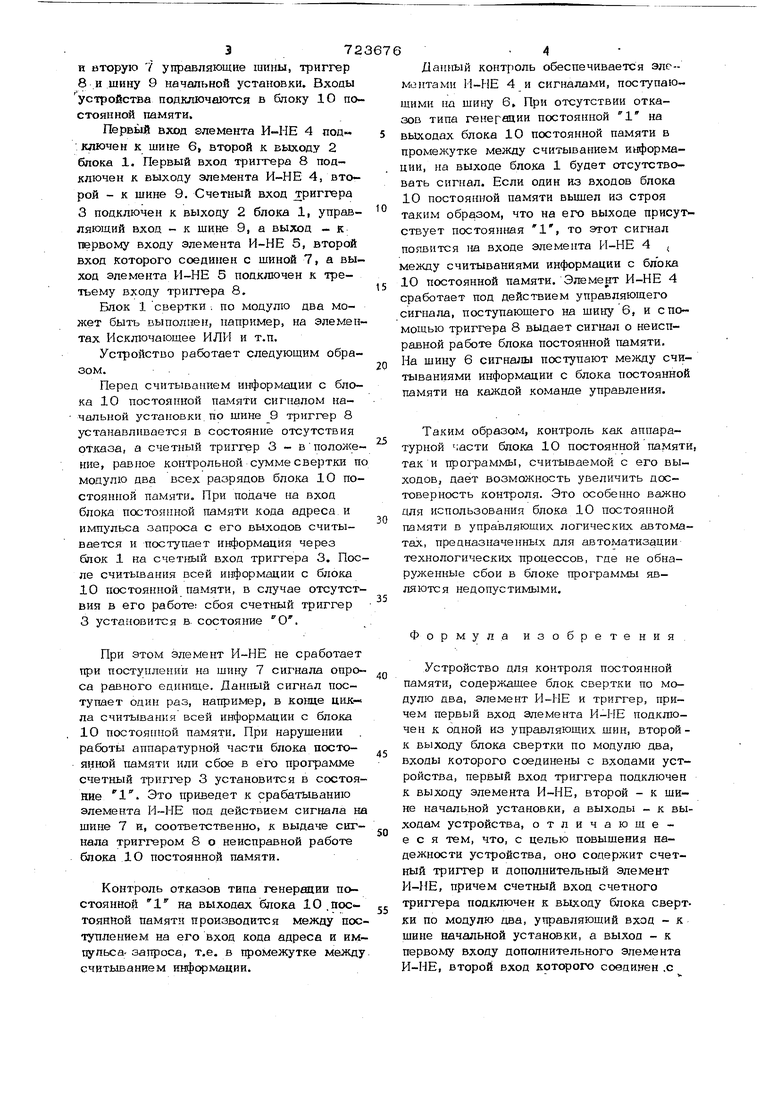

На приведена блок-схема устройства.

Устройство содержит блок 1 свертки по модулю два, выполненный по пирамидальной схеме и имеющий выход 2, счетный триггер 3, элемент И-НЕ 4, дополнительный элемент И-МЕ 5, первую 6 и вторую 7 управляющие шины, триггер 8 и шину 9 начальной установки. Входы устройства подключаются в блоку Ю по стоянной памяти. Первый вход элемента 4 под-. ключен к шине 6, второй к выходу 2 блока 1. Первый вход триггера 8 подключен к выходу элемента И-НЕ 4, второй - к шине 9. Счетный вход триггера 3 подключен к выходу 2 блока 1, управляющий вход - к шине 9, а выход - к первому входу элемента И-НЕ 5, второй вход которого соединен с шиной 7, а вы ход элемента И-НЕ 5 подключен к третьему входу триггера 8. 13ЛОК 1 свертки . по модулю два может быть выполнен, например, на элемен тах Исключающее ИЛИ и т.п. Устройство работает следующим образом.. Перед считыванием информации с блока 10 постоянной памяти сигналом начальной установки по шине 9 триггер 8 устанавливаеах;я в состояние отсутствия отказа, а счетный триггер 3 - в пололш ние, равное контрольной сумме свертки п модулю два всех разрядов блока 10 постоянной памяти. При подаче на вход блока постоянной памяти кода адреса.и импульса запроса с его выходов считывается и поступает информация через блок 1 на счетный вход триггера 3. Пос ле считывания всей информации с блока 10 постоянной памяти, в случае отсутст вия в его работе: сбоя счетный триггер 3 установится в состояние О. При этом Элемент И-НЕ не сработает при поступлении на шину 7 сигнала опроса равного единице. Данный сигнал поступает один раз, например, в конце цикла считывания всей информации с блока 10 постоянной памяти. При нарушении работы аппаратурной части блока постоян1юй памяти или сбое в его программе счетный триггер 3 установится в состояние 1. Это приведет к срабатыванию элемента И-НЕ под действием сигнала на шине 7 и, соответственно, к выдаче сигнала триггером 8 о неисправной работе блока 1О постоянной памяти. Контроль отказов типа генерации постоянной на выходах блока 10 .постоянной памяти производится между поступлением на его вход кода адреса и имщгльса- запроса, т.е. в промежутке между считыванием информации. Данный контроль обеспечивается элементами И-НЕ 4 и сигналами, поступающими на шину 6. При отсутствии отказов типа генерации ПОСТОЯНЕЮЙ 1 на выходах блока 10 постоянной памяти в промежутке между считыванием информации, на выходе блока 1 будет отсутствовать сигнал. Если один из входов блока 10 постоянной памяти вьш1ел из строя таким образом, что на его выходе присутствует постоянная 1, то этот сигнал появится на входе элемента И-НЕ 4 , между считываниями информации с блока 10 постоянной памяти. Элемент И-НЕ 4 сработает под действием управляющего сигнала, поступающего на шину 6, и с помощью триггера 8 выдает сигнал о неисправной работе блока постоянной памяти. На шину 6 сигналы поступают между считываниями информации с блока постоянной памяти на каждой команде управления. Таким образом, контроль как аппаратурной части блока Ю постоянной памяти, так и программы, считываемой с его выходов, дает возможность увеличить достоверность контроля. Это особенно важно для использования блока 10 постоянной памяти в управляющих логических автоматах, предназначенны.х для автоматизации технологических процессов, где не обнаруженные сбои в блоке программы являются недопустимыми. Формул.а изобретения. Устройство для контроля постоянной памяти, содержащее блок свертки по модулю два, элемент И-НЕ и триггер, причем первый вход Элемента И-НЕ подключен к одной из управляющих щин, второйк выходу блока свертки по модулю два, входы которого соединены с входами устройства, первый вход триггера подключен к выходу элемента И-НЕ, второй - к шине начальной установки, а выходы - к выходам устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит счетный триггер и дополнительный элемент И-НЕ, причем счетный вход счетного триггера подключен к выходу блока сверт. ки по модулю два, управляющий вход - к шине начальной установки, а выход - к первому входу дополнительного элемента И-НЕ, второй вход которого соединен .с

другой управляющей шиной, а выход дополнительного элемента И-НЕ подключен к третьему входу триггера.

Источники информацги, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

364967, кл, G 11 С 29/ОО, 1971.

2.Отчет по разработке блока контроля проверки ДЗУ ПЭЗ 008. 114 93. Московский завод САМ, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Микропрограммное устройство управления с исправлением ошибок | 1981 |

|

SU985789A1 |

| Постоянное запоминающее устройство с самоконтролем | 1982 |

|

SU1084902A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для диагностирования периферийных устройств | 1990 |

|

SU1716518A1 |

| Многопроцессорная система | 1989 |

|

SU1686455A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1986 |

|

SU1505257A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1267415A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

г I .

ю

-гК

5 6

Авторы

Даты

1980-03-25—Публикация

1978-05-16—Подача