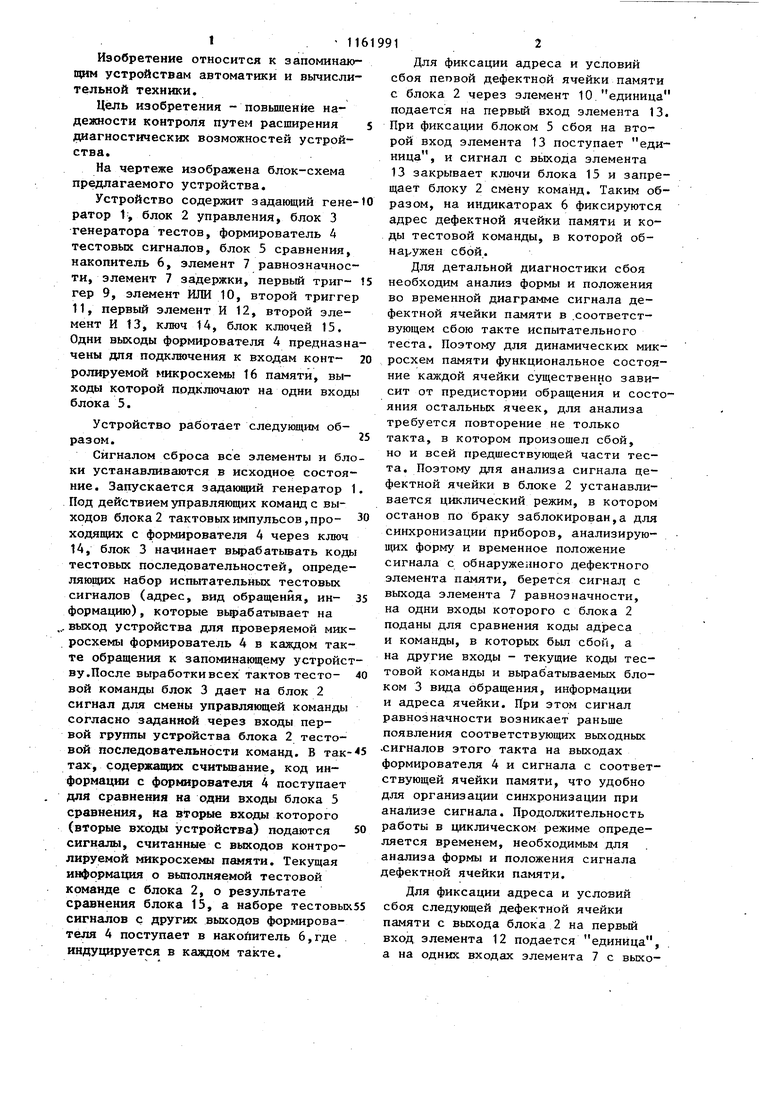

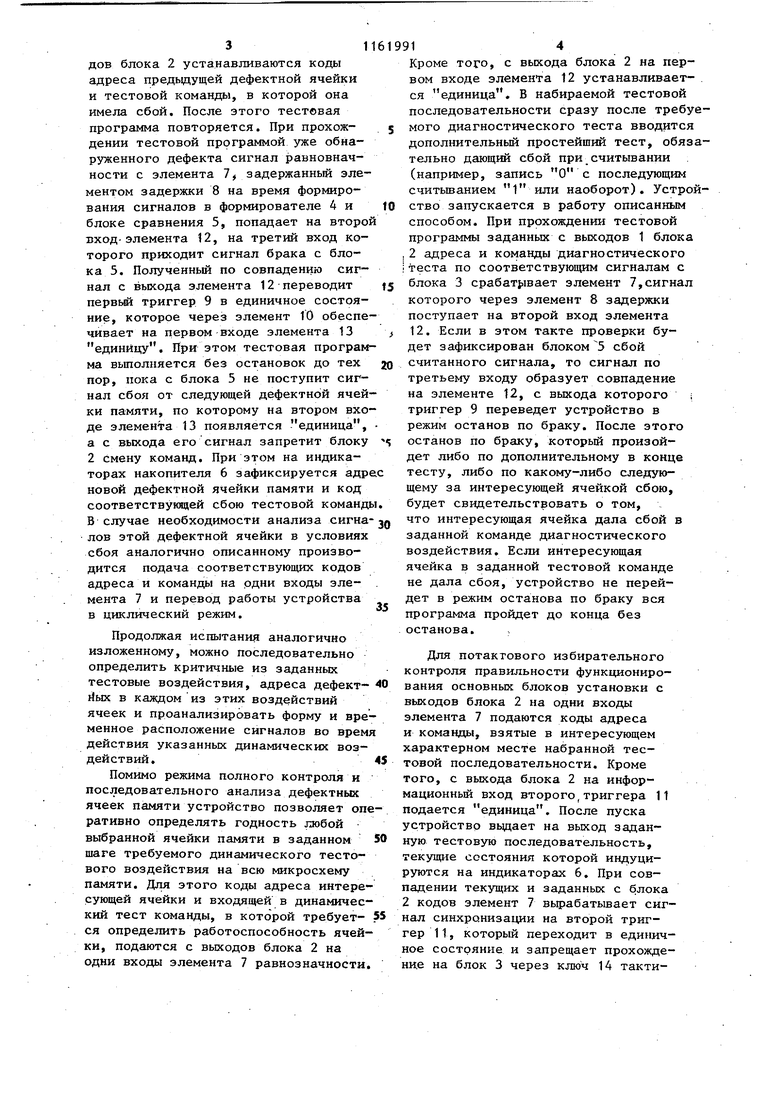

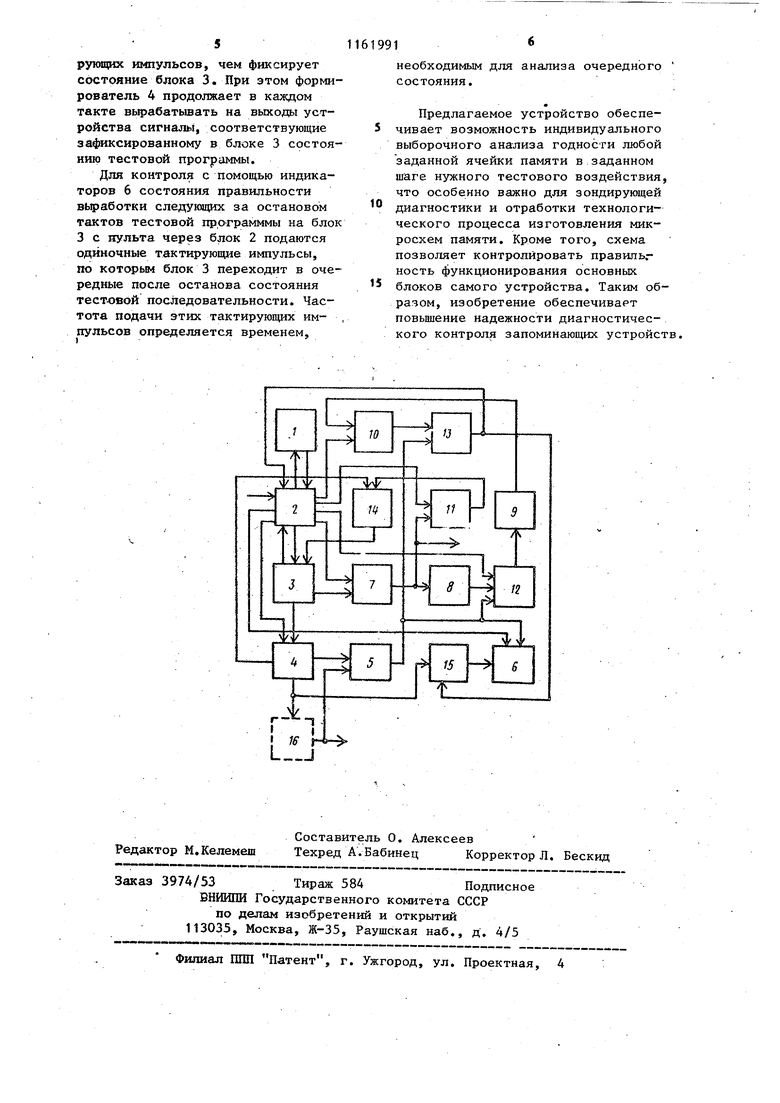

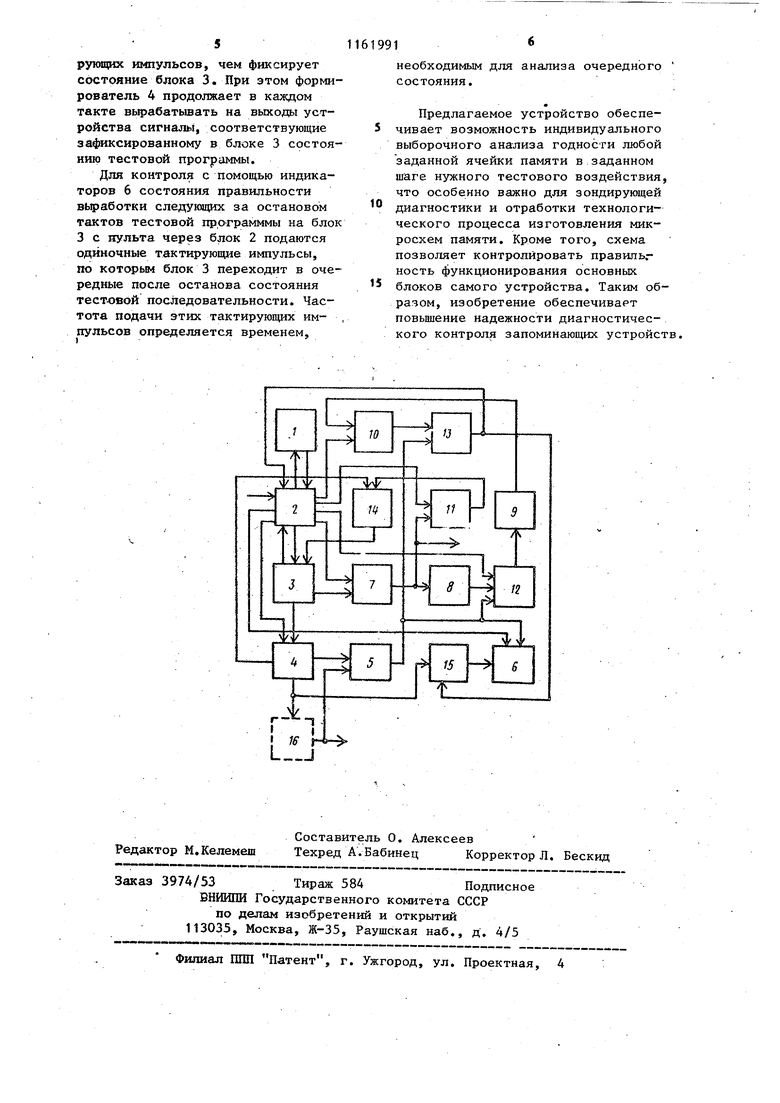

1 1 Изобретение относится к запомннакг щим устройствам автоматики и вычисли тельной текинки. Цель изобретения - повьшенйе надежности контроля путем расширения диагностических возможностей устройства. На чертеже изображена блок-схема предлагаемого устройства. Устройство содержит задающий гене ратор 1, блок 2 управления, блок 3 генератора тестов, формирователь 4 тестовых сигналов, блок 5 сравнения, накопитель 6, элемент 7 равнозначнос ти, злемент 7 задержки, первый триггер 9, элемент ИЖ 10, второй тригге 11, первый элемент И 12, второй элемент И 13, ключ 14, блок ключей 15, Одни выходы формирователя 4 предназн чены дпя подкгаочения к входам контролируемой микросхемы 16 памяти, выходы которой подключают на одни вход блока 5. Устройство работает следующим образом. Сигналом сброса все элементы и бл ки устанавливаются в исходное состоя ние. Запускается задакнций генератор Под действием управляющих команде выходов блока 2 тактовых импульсов, проходящих с формирователя 4 через ключ 14, блок 3 начинает вырабатьюать код тестовых последовательностей, опреде ляющих набор испытательных тестовых сигналов (адрес, вид обращения, информацию), которые вырабатывает на .выход устройства для проверяемой мик росхемы формирователь 4 в каждом так те обращения к запоминающему устройс ву.После выработкивсех тактов тестовой команды блок 3 дает на блок 2 сигнал для смены управляющей команды согласно заданной через входы первой группы устройства блока 2 тестовой последовательности команд. В так так, содержащих считывание, код информацш с формирователя 4 поступает для сравнения на одни входы блока 5 сравнения, на вторые входы которого (вторые входы устройства) подаются сигналы, считанные с выходов контролируемой микросхемы памяти. Текущая информация о выполняемой тестовой команде с блока 2, о результате сравнения блока 15, а наборе тестовы сигналов с других выходов формирователя 4 поступает в накоАитеЛь 6,где индуцируется в каждом такте. 12 Для фиксации адреса и условий сбоя пепвой дефектной ячейки памяти с блока 2 через элемент 10.единица подается на первый вход элемента 13. При фиксации блоком 5 сбоя на второй вход элемента 13 поступает единица, и сигнал с выхода элемента 13 закрывает ключи блока 15 и запрещает блоку 2 смену команд. Таким образом, на индикаторах 6 фиксируются адрес дефектной ячейки памяти и коды тестовой команды, в которой обнаружен сбой. Для детальной диагностики сбоя необходим анализ формы и положения во временной диаграмме сигнала дефектной ячейки памяти в .соответствующем сбою такте испытательного теста. Поэтому для динамических микросхем памяти функциональное состояние каждой ячейки существенно зависит от предистории обращения и состояния остальных ячеек, для анализа требуется повторение не только такта, в котором произошел сбой, но и всей предшествующей части теста. Поэтому для анализа сигнала дефектной ячейки в блоке 2 устанавливается циклический режим, в котором останов по браку заблокирован,а для синхронизации приборов, анализирующих форму и временное положение сигнала с обнаруженного дефектного элемента памяти, берется сигнал с выхода элемента 7 равнозначности, на одни входы которого с блока 2 поданы для сравнения коды адреса и команды, в которых был сбой, а на другие входы - текущие коды тестовой команды и вырабатываемых блоком 3 вида обращения, информации и адреса ячейки. При этом сигнал равнозначности возникает раньше появления соответствующих выходных .сигналов этого такта на выходах формирователя 4 и сигнала с соответствующей ячейки памяти, что удобно для организации синхронизации при анализе сигнала. Продолжительность работы в циклическом режиме определяется временем, необходимым для анализа формы и положения сигнала дефектной ячейки памяти. Для фиксации адреса и условий сбоя следующей дефектной ячейки памяти с выхода блока 2 на первый вход элемента 12 подается единица, а на одних входах элемента 7 с выходов блока 2 устанавливаются коды адреса предыдущей дефектной ячейки и тестовой команды, в которой она имела сбой. После этого тестовая программа повторяется. При прохождении тестовой программой уже обнаруженного дефекта сигнал равновначности с элемента 7, задержанньй элементом задержки 8 на время формирования сигналов в формирователе 4 и блоке сравнения 5, попадает на второ вход-элемента 12, на третий вход которого приходит сигнал брака с блока 5. Полученный по совпадению сигнал с выхода элемента 12 переводит первый триггер 9 в единичное состояние, которое через элемент 10 обеспе чивает на первом входе элемента 13 единицу. При этом тестовая програм ма выполняется без остановок до тех пор, пока с блока 5 не поступит сигнал сбоя от следующей дефектной ячей ки памяти, по которому на втором вхо де элемента 13 появляется единица, а с выхода его сигнал запретит блоку 2 смену команд. При этом на индикаторах накопителя 6 зафиксируется адр новой дефектной ячейки памяти и код соответствующей сбою тестовой команд В случае необходимости анализа сигна лов этой дефектной ячейки в условиях сбоя аналогично описанному производится подача соответствующих кодов адреса и команды на одни входы элемента 7 и перевод работы устройства в циклический режим. Продолжая испытания аналогично изложенному, можно последовательно определить критичные из заданных тестовые воздействия, адреса дефектйых в каждом из этих воздействий ячеек и проанализировать форму и вре менное расположение сигналов во врем действия указанных динамических воздействий. Помимо режима полного контроля и последовательного анализа дефектных ячеек памяти устройство позволяет оп ративно определять годность любой выбранной ячейки памяти в заданном шаге требуемого динамического тестового воздействия на всю микросхему памяти. Для этого коды адреса интере сующей ячейки и входящей в динамичес кий тест команды, в которой требуется определить работоспособность ячей ки, подаются с выходов блока 2 на одни входы элемента 7 равнозначности Кроме того, с вькода блока 2 на первом входе элемента 12 устанавливает- . ся единица. В набираемой тестовой последовательности сразу после требуемого диагностического теста вводится дополнительный простейший тест, обязательно дающий сбой при считывании . (например, запись О с последующим считьшанием 1 или наоборот). Устройство запускается в работу описанным способом. При прохождении тестовой программы заданных с выходов 1 блока 2 адреса и команды диагностического теста по соответствующим сигналам с блока 3 срабат| шает элемент 7,сигнал которого через элемент 8 задержки поступает на второй вход элемента 12. Если в этом такте проверки будет зафиксирован блоком 5 сбой считанного сигнала, то сигнал по третьему входу образует совпадение на элементе 12, с выхода которого i триггер 9 переведет устройство в режим останов по браку. После этого останов по браку, который произойдет либо по дополнительному в конце тесту, либо по какому-либо следующему за интересующей ячейкой сбою, будет свидетельствовать о том, что интересующая ячейка дала сбой в заданной команде диагностического воздействия. Если интересующая ячейка в заданной тестовой команде не дала сбоя, устройство не перейдет в режим останова по браку вся программа пройдет до конца без останова. . Для потактового избирательного контроля правильности функционирования основных блоков установки с выходов блока 2 на одни входы элемента 7 подаются коды адреса и команды, взятые в интересующем характерном месте набранной тестовой последовательности. Кроме того, с выхода блока 2 на информационный вход второго,триггера 11 подается единица. После пуска устройство вьздает на выход заданную тестовую последовательность, текущие состояния которой индуцируются на индикаторах 6. При совпадении текущих и заданных с блока 2кодов элемент 7 вырабатывает сигнал синхронизации на второй триггер 1 1 , который переходит в единичное состояние и запрещает прохождение на блок 3 через ключ 14 тактирующих импульсов, чем фиксирует состояние блока 3. При этом формирователь 4 продолжает в каждом такта вырабатьшать на выходы устройства сигналь, соответствующие зафиксированному в блоке 3 состоянию тестовой программы.

Для контроля с помощью индикаторов 6 состояния правильности вьфаботки следующих за остановом тактов тестовой пррграмммы на блок 3 с пульта через блок 2 подаются одиночные тактирующие импульсы, по которым блок 3 переходит в очередные после останова состояния тестовой последовательности. Частота подачи этих тактирующих импульсов определяется временем.

необходимым для анализа очередного состояния.

Предлагаемое устройство обеспечивает возможность индивидуального выборочного анализа годности любой заданной ячейки памяти в заданном шаге нужного тестового воздействия, что особенно важно для зондирующей диагностики и отработки технологического процесса изготовления микросхем памяти. Кроме того, схема позволяет контролировать правшть,ность функционирования основных блоков самого устройства. Таким образом, изобретение обеспечивает повьшение надежности диагностического контроля запоминающих устройст

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля выполнения тестовой программы | 1986 |

|

SU1317442A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1228109A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957278A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

УСТРОЙСТВО ДЛЯ ДИАГНОСТИЧЕСКОГО КОНТРОЛЯ ПАМЯТИ, содержащее задающий генератор, вход и выход которого соединен с соответствующими выходом и входом блока управления, входы и выходы первой группы которого подключены к соот- ветствующим выходам и входам блока генерации тестов, входы второй группы блока управления являются входами первой группы устройства, а выхода второй группы соединены с входами первой группы накопителя, вход управления которого подключен к выходу блока сравнения, одни входы которого соединены с одними выходами формирователя тестовых сигналов, а другие входы являются вторыми входами уст- ройства, входы формирователя тестовых сигналов подключены к соответствующим выходам блока управления и блока генераций тестов, а другие выходы являются выходами устройства, первый выход блока управления соединен с одним входом элемента равнозначности, другой вход которого Подключен к выходу блока генерации тёе- тов, а выход является выходом синхронизации устройства, отличающееся тем, что, с целью повышения надежности контроля, устройство содержит элемент задержки, первый и второй триггеры, элемент ИЛИ, ключ, блок ключей, первый и второй элементы И, причем второй выход блока управления соединен с первым входом первого элемента И, третий выход блока управления подключен к информационному входу второго триггера, а четвертый выход к второму входу элемента ИЛИ, выход элемента равнозначности соединен с входом элемента задержки и входом синхронизации второго триггера, выход которого под(Л ключен к первому входу ключа, второй вход которого соединен с выходом формирователя тестовых сигналов, а виход - с входом блока генерации тестов, выход элемента задержки подключен к второму входу первого элемента И, третий вход которого соединен с выходом блока сравнения и вторым а входом второго элемента И, а выход с входом первого триггера, выход которого подключен к первому входу со со элемента ШШ, выход которого соединен с первым входом второго элемента И, выход которого подключен к входу блока управления и к входу управления: блока ключей, информационные входы которого соединены с другими выходами формирователя тестовых сигналов, а выходы подключены к входам второй группы накопителя.

| Патент США № 3806243, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля полупроводниковой памяти | 1978 |

|

SU771730A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-06-15—Публикация

1983-06-15—Подача