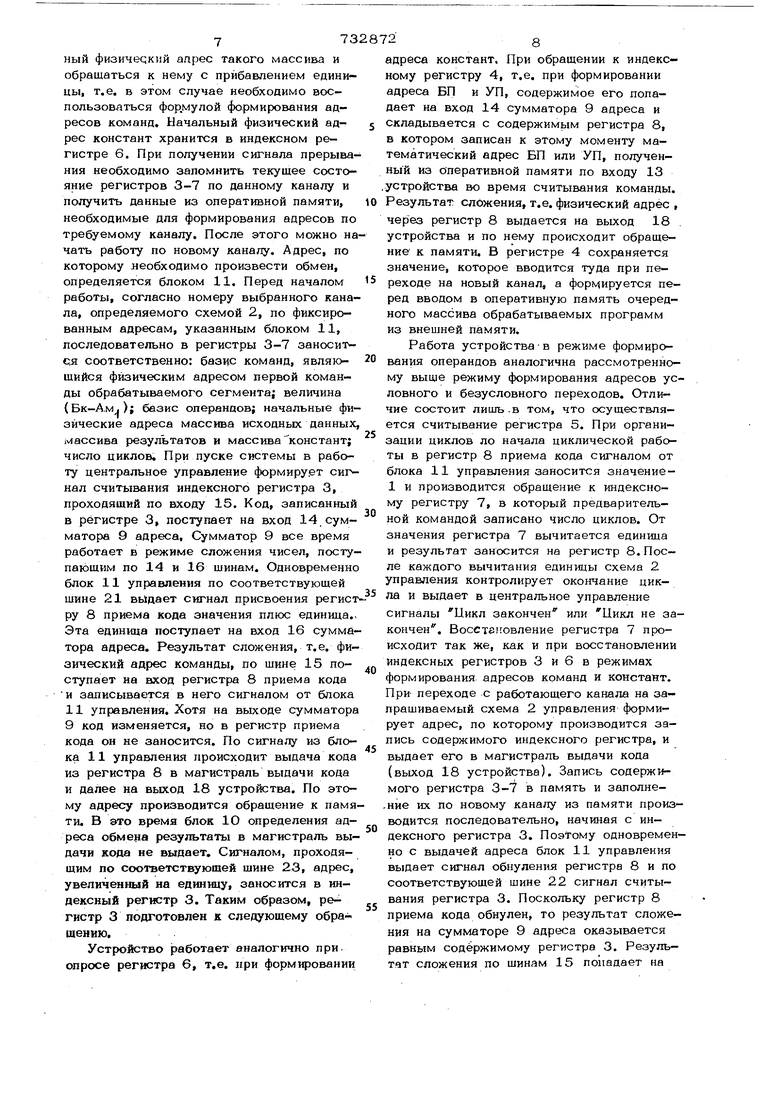

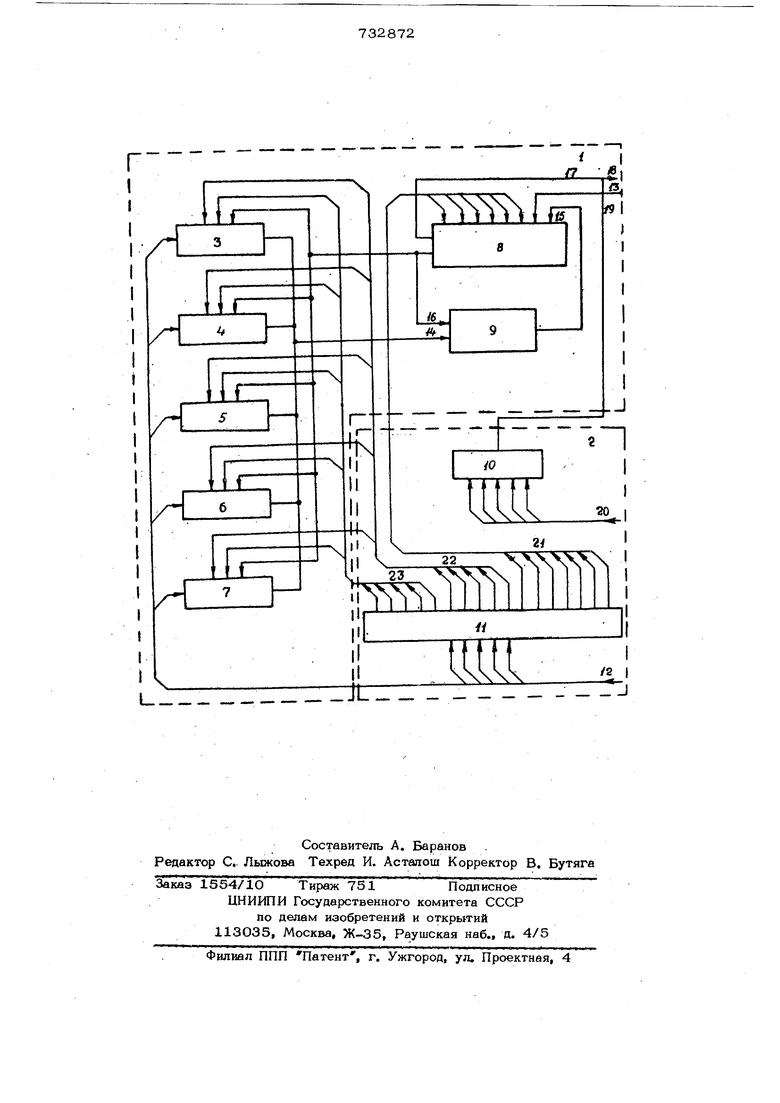

Устройство относится к вычислительной технике и может быть использовано в ЦВМ для формирования адресов. Известны устройства для формирования адресов, содержащие сумматор, регистр индексный, регистр базиса команд IJ. Наиболее близким к изобретению является устройство для формирования адресов, содержащее -блок управления, группа входов которого является первой группой входов устройства, группу индексных регистров, первые входы которых соединены с группой входов блока управления, вто-. рые входы группы индексных регистров подсоединены к первой группе выходов блока управления, а третьи входы группы индексных регистров подключены ко второ группе выходов блока управления, регистр приема кодов, группа входов которого соответственно подключена к третьей груп- пе выходов блока управления, первый вход регистра приема кодов является вторым входом устройства, второй вход подключен к выходу сумматора адреса, первый вход которого подключен к первому выходу регистра приема кодов, блок оцределения адреса обмена, группа входов которого является третьим входом устройства, а выходвыходом устройства. Индексные регистры предназначены для хранения базиса команд, являющегося физическим адресом первой команды обрабатываемого сегмента программы, базиса операндов, начального физического адреса констант, числа циклов, величины (Бк-Ам ), где Бк - базис команд; AM, - математический адрес первой команды участка программы, вводимого в оперативную память. Перед началом работы устройства из фиксированных адресов оперативной памяти в индексные регистры последовательно заносится соответствук щая информация. При атом блок определения адреса обмена в соответствии с номером запрашиваемого канала формирует адрес обращения к памяти. Этот адрес поступает на выход устройства. Одновременво микропрограммный блок управления выдает сигнал на подготовку соответствуюшего индексного регистра к приему . Содержимое фиксированной ячейки памяти, адрес которой сформирован, поступает ли вход устройства и фиксируется в регистре приема кода и регистре регенерации. По сигналу из микропрограммного блока управления происходит считывание кода из регистра регенерации и запись этого кода в подготовленный индексный регистр Аналогичным образом, но по другим адресам, происходит заполнение остальных индексных регистров. После заполнения последнего индексного регистра выдается сигнал окончания обмена и начинается работа системы по выполнению программы Из центрального управления в устройство на первый вход индексного регистра базиса команд приходит сигнал считыван1Шо Считанный код запоминается в регис ре выдачи кода и поступает на первый вход сумматора адреса. Этот вход определяет работу сумматора с прибавлением единицы. Результат сложения, т.е. физический адрес, поступает на выход устройства. По нему происходит обращение к па мяти. Кроме того, результат из выхода, предварительно усиленный, поступает на вход устройства и фиксируется в регистре регенерации и регистре приема кода. По сигналам из микропрограммного блока управления происходит считывание информации из регистра регенерации и запись ее по второму входу в подготовленный ин дексный регистр (в данном случае подготовлен индексный регистр базиса команд) Подготовка к записи того или иного индексного регистра определяется и выполняется центральным управлением. Таким образом, индексный регистр базиса коман подготовлен к следующему обращению. Устройство работает аналогично при опросе индексного регистра начального физического адреса констант, т.е. в режиме формирования адреса констант. При обращении к индексному регистру, содержащему величину (Бк-Ам), т.е. при формировании адреса условного и безусловного переходов (УП и БП), содержимое его записывается в регистр выдачи кода и попадает на второй вход сумматора адреса. Этот вход определяет режим сложения принятого кода с содержимым регистра приема кода, в котором записан математи ческий адрес БП. или УП, полученный из памяти во время считывания команды. Результат сложения, т.е. физический адрес, выдается на выход устройства и по нему происходит обращение к памяти. Аналогична работа устройства в считывания индексного регистра базиса операндов. Поскольку индексные регистры величины (Бк-Ам) -и базиса операндов выполнены с регенерацией, то в них всегда хранится значение, которое вводится туда при переходе на новый канал, а формируется перед вводом в оперативную память очередного массива обрабатываемых программ из внешней памяти. При организации циклов до начала циклической работы производится считывание индексного регистра числа циклов, в который предварительной командой записан код числа.циклов, и запись этого кода в регистр выдачи кода,- откуда код поступает на третий вход сумматора адреса. Этот вход определяет режим работы сумматора с вычитанием единицы. После каждого вычитания единицы микропрограммный блок управления контролирует окончание цикла и выдает в центральное управление сигналы Цикл закончен либо Цикл не закончен. Восстановление содержимого индексного регистра числа циклов происходит так. же, как и при восстановлении индексных регистров при формировании адресов констант и команд. При переходе с работающего канала на запрашиваемый блок определения адреса обмена формирует адрес, по которому производится запись Содержимого индексного регистра, и выдает его на выход устройства. Одновременно происходит считывание содержимого одного из индексных регистров и запись в регистр вьшачи кода. Микропрограммный блок управления формирует сигнал на считывание регистра выдачи кода, содержимое которого попадает на выход устройства и заносится в память по указанному ранее адресу, В рассматриваемом режиме работа сумматора адреса производится, но результаты на выход не выдаются. Далее аналогичным образом, но по другим адресам, переписывают содержимое остальных индексных регистров. Когда в памяти зафиксируется содержимое последнего индексного регистра, нач тается заполнение индексных регистров и работа системы по новому каналу, как описано выше 2J, Недостатком указанного устройства являются больщие аппаратурные затраты на реализацию приема, выдачи и регенерации кода. Цель изобретения - сокращение аппаратурных затоат устройства. 5732 Поставленная цель достигается тем, что выходы ifflaoKCHbix регистров подключены ко второму входу сумматора адреса, а четвертые входы -к.первому выходу регистра приема кодов, второй выход которого подключен к выходу устройства. Таким образом, прием, выдачу и регенерацию кода выполняет один регистр приема кода. На чертеже представлена схема предлагаемого устройства. Схема содержит индексный арифметический блок 1 и схему 2 управления. Индексный арифметический блок 1 состоит из рабочих индексных регистров 3-7, регистра 8 приема кода и сумматора 9 адреся. В состав схемы 2 управления входят блок 1О определения адреса обмена и блок 11 управления. Индексные регистры 3-7 и блок 11 управления соединены с центральным управлением системы шина ми режима, подключенными к первому вхо ду 12 устройства. Кроме того, блок 1 связан со вторым входом 13 устройства посредством регистра 8 приема кода. Сум матор 9 адреса соединен вторым входом с выходами индексных регистров 3-7 шинами 14 и выходами с регистром 8 приема кода шинами 15. Регистр 8 приема кода первым выходом посредством шин 16 соединен со вторым входом сумматора 9 и вторыми входами индексных регистров 3-7, а вторым выходом соединен шинами 1.7 с магистралью выдачи кода, подключенной к выходу 18 устройства. К магист рали выдачи кода шинами 19 подключен также блок 1О определения адреса обмена Блок Ю связан с центральным управлением, определяющим номер работающего канала, шинами переключении каналов, сое диненными с третьим входом 2О устройства. Блок 11 управления связан с центральным управлением шинами режима (пер вый вход 12 ycTpotiCTBa), с регистром 8 приема кода третьей группой шин 21, с цепями считывания индексных регистров 3-7 второй группой шин 22 и с цепями записи индкесных регистров 3-7 первой группой шин 23. Каждая программа располагается в оперативной памяти системы в ячейках, следующих одна за другой, т.е. последова тельно, Для того, чтобы начать обработ ку какой-то программы, необходимо иметь адрес первой команды программы., После выполнения первой команды к этому адресу нужно прибавить единицу для получе н-ия адреса второй команды и т.д. Поскол 2 ку устройство для формирования адресов работает в мультипрограммном режиме, а программы пишутся в математических адресах, возникает необходимость различать, к какому каналу относится тот или иной адрес. Под каналом понимается совокупность аппаратных и программных средств, предназначенных для обработки группы программ, обьединенньк по неко- торому обшек-гу признаку принадлежности ИЗ всего множества программ. Для установления принадлежности каналу вводится величина, которая называется базисом команд. Эта величина постоянна в данной системе для каждого канала и является физическим адресом первой команды вводимого сегмента. В индексном регистре 3 хранится значение базиса команды работающего в данный момент канала. Физический адрес команды условного и безусловного переходов формируется по правилу: Аф Бк-Ам;1+АМ, где Аф - физический адрес УП или БП; Бк - базис команд; математический адрес первой команды участка программы, вводимого в память; Ам - математический адрес команды УП (БП), Математический адрес УП и БП хранится в слове команды. Для хранения величины (Бк-Ам) текущей программы предусмотрен индексный регистр 4. Для каждого канала в памяти отводится область для операндов. Они могут выбираться и заноситься туда в любом порядке. Чтобы сформировать физический адрес операнда необходимо иметь базис операндов и прибавлять к нему математический адрес операнда, который хранится в слове команды. Для хранения базиса операндов прецусмот рен индексный регистр 5. При вьтолнении программ часто приходится иметь дело с циклическими режимами работы. В устройстве для формирования адресов нужно иметь данные о числе циклов и по мере прохождения цикла вычитать из не.го единицу, сравнивая все время с нулем. Сигналы циклического режима работы поступают в центральное управление, где они анализируются, и затем либо цикл продолжается, либо кончается. Число циклов текущей программы хранится в индексном регистре 7. В памяти отводятся участки для массива исходных данных, массива результатов и массива констант. Каждый из этих массивов располагается в памяти в последовательных ячейках, и обращение к ним происходит тоже последовательно. Таким образом, необходимо иметь началь773ный физичедкнй адрес такого массива и обращаться к нему с прибавлением единицы, т.е. в этом случае необходимо воспользоваться фор.мулой формирования адресов команд. Начальный физический адрес констант хранится в индексном регистре 6. При получении сигнала прерывания необходимо запомнить текущее состояние регистров 3-7 по данному каналу и получить данные из оперативной памяти, необходимые для формирования адресов по требуемому каналу. После этого можно на чать работу по новому каналу. Адрес, по которому необходимо произвести обмен, определяется блоком 11. Перед началом работы, согласно номеру выбранного канала, определяемого схемой 2, по фиксированным адресам, указанным блоком 11, последовательно в регистры 3-7 заносится соответственно: базис команд, являк щийся физическим адресом первой команды обрабатываемого сегмента; величина {Бк-А.м,); базис операндов; начальные физические адреса массива исходных данных, массива результатов в массива констант; число циклов. При пуске системы в работу центральное управление формирует сигнал считывания индексного регистра 3, проходящий по входу 15. Код, записанный в регистре 3, поступает на вход 14. сумматора 9 адреса. Сумматор 9 все время работает в режиме сложения чисел, поступающим по 14 и 16 шинам. Одновременно блок 11 управления по соответствующей шине 21 сигнал присвоения регист ру 8 приема кода значения плюс единица., Эта единица поступает на вход 16 сумматора адреса. Результат сложения, т.е. физический адрес команды, по шине 15 поступает на вход регистра 8 приема кода и записывается в него сигналом от блока 11 управления. Хотя на выходе сумматора 9 код изменяется, но в регистр приема кода он не заносится. По сигналу из блока 1 1 управления происходит выдача кода из регистра 8 в магистраль выдачи кода и далее на выход 18 устройства. По этому адресу производится обращение к памяти. В это время блок 10 определения адреса обмена результаты в магистраль выдачи кода не выдает. Сигналом, проходящим по соответствуюшей щине 23, адрес, увеличенный на единицу, заносится в индексный регистр 3. Таким образом, регистр 3 подготовлен к следующему обращению. Устройство работает аналогично при. опросе регистра 6, т.е. при формировании 2 адреса констант. При обращении к индексному регистру 4, т.е. при формировании адреса БП и УП, содержимое его попадает на вход 14 сумматора 9 адреса и складывается с содержимым регистра 8, в котором записан к этому моменту математический адрес БП или УП, полученный из оперативной памяти по входу 13 устройства во время считывания команды. Результат сложения, т.е. физический адрес , черкез регистр 8 выдается на выход 18 устройства и по нему происходит обращение к памяти. Б регистре 4 сохраняется значение которое вводится туда при переходе на новый канал, а формируется перед вводом в оперативную память очередного массива обрабатываемых программ из внешней памяти. Работа устройства-в режиме формирования операндов аналогична рассмотренному выше режиму формирования адресов условного и безусловного переходов. Отличие состоит лишь .в том, что осуществляется считывание регистра 5. При организации циклов ло начала циклической работы в регистр 8 приема кода сигналом от блока 11 управления заносится значение1 и производится обращение к индексному регистру 7, в который предварительной командой записано число циклов. От значения регистра 7 вычитается единица и результат заносится на регистр 8. После каждого вычитания единицы схема 2 управления контролирует окончание цикла и выдает в центральное управление сигналы Цикл закончен или Цикл не закончен . Восстановление регистра 7 происходит так же, как и при восстановлении индексных регистров 3 и 6 в режимах формирования адресов команд и констант. При переходе с работающего канала на запрашиваемый схема 2 управления формирует адрес, по которому производится запись содержимого индексного регистра, и выдает его в магистраль выдачи кода (выход 18 устройства). Запись содержимого регистра 3-7 в память и заполне- ние их по новому каналу из памяти производится последовательно, начиная с индексного регистра 3. Поэтому одновременно с выдачей адреса блок 11 управления выдает сигнал обнуления регистра 8 и по соответствующей шине 22 сигнал считывания регистра 3. Поскольку регистр 8 приема кода обнулен, то результат сложения на сумматоре 9 адреса оказывается равным содержимому регистра 3. Результат сложения по шинам 15 попадает на 973 вход регистра 8 приема кода и заносится. После этого блок 11 управления формирует сигнал по соответствующей шине 21 на считывание регистра 8, содержимо которого выдается в магистраль выдачи кода, откуда попадает в фиксированную ячейку памяти по указанному ранее адресу. Далее аналогичным образом, но по другим адресам, переписывают содержимое регистров 4-7 в память. Когда в памяти зафиксируется содержимое последнего индексного регистра 7, с помощью схемы 2 начинается запись содержимого запрашиваемого канала из фиксированных ячеек памяти в регистры 3-7. При этом блок 10 определения адреса обмена в соответствии с номером запрашиваемого канала, который подается по входу 20, формирует адрес обращения к памяти. Этот адрес поступает в магистраль выдачи кода. Содержимое фиксированной ячейки памяти, адрес которой сформирован, поступает на вход 13 устройства и сигналом от блока 11 управ ления записывается в регистр 8 приема кода. Сигналом по соответствующей шине 23 содержимое регистра 8 заносится в индексный регистр. В данном случае запись осуществляется в регистр 3. Аналогичным образом, но по другим адресам, осуществляется заполнение регистров 4-7 После заполнения индексного регистра 7 схема 2 управления выдает сигнал окончания обмена информацией между сигналами и начинается работа системы по новому каналу. В устройстве для формирования адресо аппаратурные затраты на построение, любог индексного регистра, регистра приема ко да или блока определения адреса обмена можно считать примерно одинаковыми, за траты на построение сумматора адреса., вдвое, а блока управления втрое больше, чем затраты на любой регистр устройства Примем аппаратурные затраты на построе ние регистра за единицу. Тогда затраты на построение известного устройства составляет 14 единиц, а на предлагаемое устройство - 12 единиц. Таким образом, построение предлагаемого устройства позволяет сократить аппаратурные затраты на 2 единицы, что составляет 14% аппаратурных затрат известного. Формула изобретения Устройство для формирования адресов. Содержащее блок управления, группа входов которого является первой группой входов устройства, группу индексных регисгров, первые входы которых соединены с группой входов блока управления, вторые входы группы индексных регистров подсоединены к первой группе выходов блока управления, а третьи входы группы индексных регистров подключены ко второй группе выходов блока управления, регистр прИема кодов, группа входов которого, соот ветственно подключена к третьей группе выходов блока управления, первый вход регистра приема кодов является вторым входом устройства, второй вход подключен к выходу сумматора адреса, первый вход которого подключен к первому выходу регистра приема кодов, блок определения адреса обмена, группа входов которого я&ляется третьим входом устройства, а выход - выходом устройства, отличающееся тем, что, с целью уменьщения аппаратурных затрат, выходы индексных регистров подключены ко второму вхоцу сумматора адреса, а четвертые входы - к первому выходу регистра приема кодов, второй выход которого подключен к выходу устройства. Источник информации, принятые во внимание при экспертизе 1.Малиновский Б. Н. и др. Справочник по цифровой вычислительной технике. Техника, 1974. 2.Авторское свидетельство СССР № 438О14, кл. 6 Об F 9/19, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов | 1971 |

|

SU438014A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| ПРОЦЕССОР | 1990 |

|

SU1826787A1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство отсчета времени в цвм | 1977 |

|

SU691828A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1985 |

|

SU1307462A1 |

Авторы

Даты

1980-05-05—Публикация

1977-11-02—Подача