1

Изобретение относится к области вычислительной техники и может использоваться в вычислительных машинах, работающих в мультипрограммном режиме в условиях разделения времени.

Известны устройства для формирования адресов многопрограммной системы, в которых информапия, необходимая для работы по каждой программе, хранится в запоминающем устройстве, а для нахождения нужной в данный момент информации служит адресное запоминающее устройство.

При такой организации формирования адресов в многопрограммных системах необходимо по крайней мере дважды перед выполнением команды обращаться к памяти, что увеличивает время обработки программы.

Целью изобретения является повышение быстродействия устройства для формирования адресов, работающего в мультипрограммном режиме.

Это достигается тем, что в предлагаемом устройстве индексные регистры являются одновременно рабочими регистрами индексной арифметики, причем количество этих индексных регистров не превышает количества их в случае однопрограммной работы.

Сущность изобретения заключается в том, что в устройстве выходы индексных регистров соединены с соответствующими входами регистра выдачи кода, первый, второй и третий выходы которого соединены с одноименными входами сумматора адреса, четвертым входом подключенного к выходу регистра приема кода, первый вход которого соединен с первым выходом сумматора адреса, второй вы.ход сумматора адреса и выход регистра выдачи кода подключены к выходу устройства, третий вход которого соединен с вторым входом регисгра приема кода и входом регистра регенерации, выходом подключенного к первым входам индексных регистров, вторые входы которых соединены с первым входом устройства.

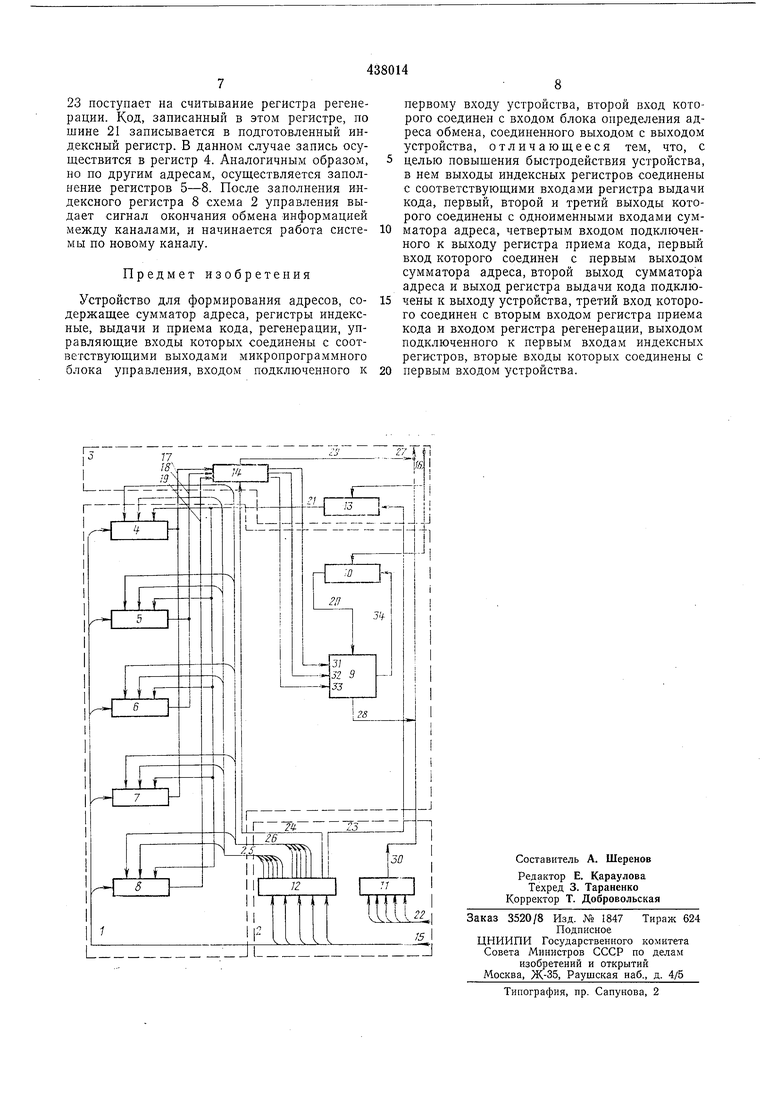

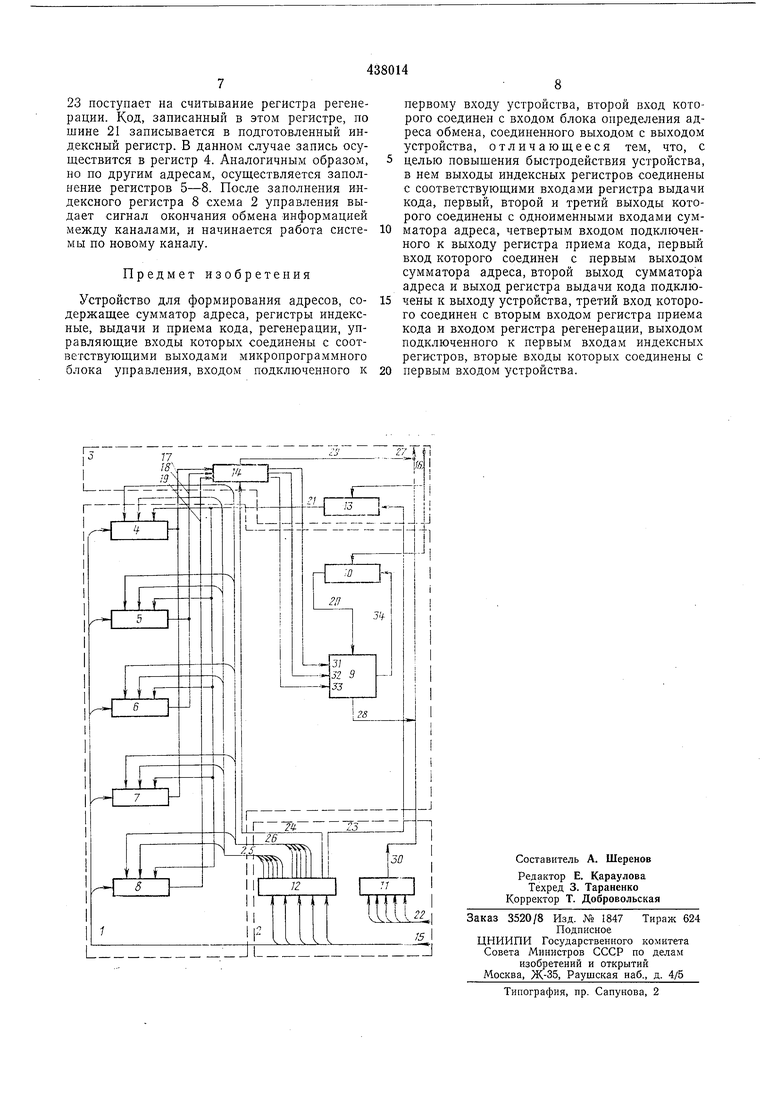

На чертеже представлена схема предлагаемого устройства.

С.хема содержит индексный арифметический блок 1, схему 2 управления, схему 3 обмена и регенерации информации.

Индексный арифметический блок 1 состоит из рабочих индексных регистров 4-8, причем регистры 5 и 6 выполнены с регенерацией сумматора адреса 9 и регистра 10 приема кода.

В состав схемы 2 управления входят блок 11 определения адреса обмена и микропрограммный блок 12 управления.

Схема 3 обмена и регенерации информации состоит из регистра 13 регенерации и регистра 14 выдачи кода.

Индексные регистры 4-8 и блок 12 соединены с центральным управлением системы шинами режима, подключенными к входу 15 устройства для формирования адресов. Кроме того, блок 1 связан с магистралью нриема кода системы, подсоединенной к входу 16 устройства, посредством регистра 10 приема кода. Сумматор 9 соединен через регистр 14 выдачи кода с индексными регистрами 4 и 7 шичой 17, с индексными регистрами 5 и 6 шиной 18, с индексным регистром 8 шиной 19. Регистр приема кода соединен с сумматором 9 шиной 20. Посредством регистра 13 регенерации и шины 21 индексные регистры 4-8 связаны с магистралью системы, подключенной к входу 16. Блок 11 определения адреса связан с-центральным управлением, определяюш,им номер работающего канала, шинами переключения каналов, соединенными с входом 22 устройства. Блок 12 управления связан с центральным управлением шинами режима (вход 15), с регистром 13 регенерации шиной 23, с регистром 14 выдачи кода шиной. 24, с цепями считывания индексных регистров 4-8 шинами 25 и с цепями подготовки регистров 4-8 шинами 26. Один выход сумматора 9, выходы регистра 14 выдачи кода и блока 11 соединены с выходом 27 устройства соответственно шинами 28-30. Выход 27 устройства подключен к магистрали выдачи кода. Сумматор 9 входами 31-33 подключен к выходам регистра 14, а шиной 34-к входу регистра 10.

Ниже рассматриваются режимы работы устройства и характер операций, выполняемых в каждом режиме.

Формирование адресов команд. Каждая программа располагается в оперативной памяти (ОЗУ) системы в ячейках, слеДуюших одна за другой, т. е. последовательно. Для того, чтобы начать обработку какой-то программы, необходимо иметь адрес первой команды программы. После выполнения первой команды к этому адресу нужно прибавить единицу для получения адреса второй команды и т. д.

Поскольку устройство для формирования адресов работает в.мультипрограммном режиме, а программы пишутся в мате.матических адресах, возникает необходимость различать, к какому каналу относится тот или иной адрес. Под каналом понимается совокупность аппаратных и программных средств, предназначенных для обработки группы программ, объединенных по некоторому общему признаку принадлежности из всего множества программ.

Для установления принадлежности каналу вводится величина, которая называется базисом команд. Эта величина в данной системе постоянна для каждого канала и является физическим адресом первой команды вводимого сегмента. В индексном регистре 4 хранится значение базиса команды работающего в данный момент канала.

Формирование адресов команд при условных и безусловных переходах- УП (БП). Физический адрес команды УП и БП формируется по следующему правилу

,-Л„,,

где Аф - физический адрес команды УП

физический адр( (БП);

Б,( - базис команд;

AMI - математический адрес первой команды участка программы, вводимого в память;

AM - математический адрес команды УП (БП).

Математический адрес УП и БП хранится в слове команды. Для хранения величины БК - AMI текущей программы предусмотрен индексный регистр 5.

Формирование адресов операндов. Для каждого канала в памяти отводится область для операндов. Они могут выбираться из нее и заноситься туда в любом порядке.

Чтобы сформировать физический адрес операнда, необходимо иметь базис онерандов и прибавлять к нему математический адрес онеранда.

Математический адрес операнда хранится в слове команды. Для хранения базиса операнда предусмотрен индексный регистр 6.

Ореанизация циклов. При выполнении программ часто приходится иметь дело с циклическими режимами работы. В блоке формирования адресов нужно иметь данные о числе циклов и по мере прохождения цикла вычитать из него единицу сравнения все время с нулем.

Сигналы циклического режима работы поступают в центральное унравление, где они анализируются, и затем либо цикл продолжается, либо кончается. Число циклов текущей 0 программы хранится в индексном регистре 8.

Формирование адреса констант. В памяти отводятся участки для массива исходных данных, массива результатов и массива констант. Каждый из этих массивов располагается в памяти в последовательных ячейках, и обращение к ним нроисходит тоже последовательно. Таким образом, необходимо иметь начальный физический адрес такого массива и обращаться к нему с прибавлением единицы, т. е. в этом случае необходимо воспользоваться формулой формирования адресов команд. Пачальный физический адрес хранится в индексном регистре 7.

Обмен информации при переходе на другой канал. При получении сигнала прерывания необходимо запомнить текущее состояние регистров 4-8 по данному каналу и получить данные из ОЗУ, необходимые для формирования адресов по требуемому каналу. После этого можно начать работу по новому каналу. Адрес, по которому необходимо произвести обмен, определяется блоком 11.

Перед началом работы, согласно номеру выбранного канала, определяемого схемой 2, по 5 фиксированным адресам, указанным блоком

11, последовательно на регистры 4-8 заносится соответственно: базис команд, являющийся физическим адресом первой команды обрабатываемого сегмента; величина Бк-AMI ; базис операндов; начальные физические адреса массива исходных данных, массива результатов и массива констант; число циклов.

После того, как информация на регистры занесена, начинается работа системы по выполнению программ.

При пуске системы в работу центральное управление формирует сигнал считывания индексного регистра 4, проходящий по входу 15. Код, записанный в регистре 4, проходит по шине 17, запоминается в регистре 14 выдачи кода и поступает на вход 31 сумматора 9. Вход 31 определяет режим работы сумматора с прибавлением единицы. Результат сложения, т. е. физический адрес, подается по шине 28 на выход 27 и далее в магистраль выдачи кода. По этому адресу происходит обращение к памяти.

Кроме того, результат нз магистрали выдачи кода, предварительно усиленный, попадает в магистраль приема - вход 16, где фиксируется на регистре 13 регенерации и регистре 10 приема кода. Блок 12 выдает по шине 23 сигнал опроса регистра 13. Код регистра 13 по шине 21 и по подготовленной цепи одного из индексных регистров (в данном режиме подготовлена цепь регистра 4) записывается в индексный регистр 4.

Подготовка той или иной цени определяется режимом и выполняется по сигналам центрального управления блоком 12.

Таким образом, индексный регистр 4 подготовлен к следующему обращению. Устройство работает аналогично при опросе индексного регистра 7, т. е. в режиме формирования адреса констант.

После определения адреса команды и обращения к этой команде в центральном управлении производится дещифрация кода операции, в результате которой возможно обращение к любому индексному регистру 4-8.

При обращении к индексному регистру 5, т. е. при формировании адреса БП и УП, содержимое его, пройдя по щине 18, фиксируется в регистре 14 выдачи кода и попадает на вход 32 сумматора 9. Вход 32 определяет режим сложения принятого кода (по щине 18) с содержимым регистра 10, в котором записан математический адрес УП и БП, полученный из ОЗУ по магистрали приема кода во время считывания команды. Содержимое регистра 10 передается на сумматор 9. Результат CvIIOжeния, т. 6. физический адрес, выдается на выход 27, и по нему происходит обращение к памяти.

Поскольку индексный регистр 5 выполнен с регенерацией, то в нем всегда хранится значение, которое вводится туда при переходе на новый канал, а формируется перед вводом в ОЗУ очередного массива обрабатываемых программ из внешней памяти.

Работа схемы в режиме формирования адресов )дов аналогична рассмотренному выше режиму формирования адресов условного и безусловного переходов. Отличие состоит

лишь в том, что осуществляется считывание и регенерация регистра 6.

При организации циклов до начала циклической работы производится обращение к индексному регистру 8, в который предварительно командой записано чис,чо циклов. Код регистра 8, пройдя по щине 19, фиксируется в регистре 14 и попадает на вход 33 сумматора 9. Вход 33 определяет режим работы сумматора с вычитанием единицы. После

вычитания единицы схема 2 управления контролирует окончание цикла и выдает в центральное управление сигналы «Цикл закончен либо «Пикл не закончен. Восстановление содержимого регистра 8 происходит так

же, как и при восстановлении индексных регистров 4 и 7 в режимах формирования адресов команд и констант.

При переходе с работающего канала на запрашиваемый схема 2 управления формирует

адрес, по которому производится запись содержимого регистра, и выдает его в магистраль выдачи кода (выход 27). Запись содержимого регистров 4-8 в память и заполнение их информацией по новому каналу из памяти производится последовательно, начиная с индексного регистра 4. Поэтому одновременно с выдачей адреса блок 12 формирует сигнал по соответствующей шине 25 на считывание индексного регистра 4. Содержимое регистра 4, проходя по шине 17, фиксируется в регистре 14 выдачи кода.

В рассматриваемом режиме работа сумматора 9 производится, но результаты в магистраль выдачи не выдаются. После того, как

содержимое регистра 4 зафиксировалось в регистре 14, блок 12 формирует сигнал по щине 24 на считывание регистра 14, содержимое которого выдается в магистраль выдачи, откуда попадает в фиксированную память по

указанному ранее адресу.

Далее аналогичным образом, но по другим адресам, переписывают содержимое регистров 5-8 в память. Когда в памяти зафиксируется содержимое последнего индексного регистра 8, с помощью схемы 2 начинается запись содержимого запрашиваемого канала из фиксированной памяти в регистры 4-8. При этом блок 11 определения адреса обмена в соответствии с номером запрашиваемого канала, который подается по входу 22, формирует адрес обращения к памяти. Этот адрес поступает в магистраль выдачи кода. Одновременно микропрограммный блок 12 управления выдает сигнал по соответствующей шине 26 на подготовку регистра 4 к приему кода с входа 16. Содержимое фиксированной ячейки памяги, адрес которой сформирован, поступает в магистраль приема (вход 16) и фиксируется в регистре 10 приема кода и регистре 13 регенерации. Блок 12 выдает сигнал, который по шине

23 поступает на считывание регистра регенерации. Код, записанный в этом регистре, по шине 21 записывается в подготовленный индексный регистр. В данном случае запись осуществится в регистр 4. Аналогичным образом, но по другим адресам, осуществляется заполнение регистров 5-8. После заполнения индексного регистра 8 схема 2 управления выдает сигнал окончания обмена информацией между каналами, и начинается работа системы по новому каналу.

Предмет изобретения

Устройство для формирования адресов, содержащее сумматор адреса, регистры индексные, выдачи и приема кода, регенерации, управляющие входы которых соединены с соответствующими выходами микропрограммного блока управления, входом подключенного к

первому входу устройства, второй вход которого соединен с входом блока определения адреса обмена, соединенного выходом с выходом устройства, отличающееся тем, что, с целью повыщения быстродействия устройства, в нем выходы индексных регистров соединены с соответствующими входами регистра выдачи кода, первый, второй и третий выходы которого соединены с одноименными входами сумматора адреса, четвертым входом подключенного к выходу регистра приема кода, первый вход которого соединен с первым выходом сумматора адреса, второй выход сумматора адреса и выход регистра выдачи кода подключены к выходу устройства, третий вход которого соединен с вторым входом регистра приема кода и входом регистра регенерации, выходом подключенного к первым входам индексных регистров, вторые входы которых соединены с первым входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов | 1977 |

|

SU732872A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для формирования исполнительных адресов цифровой вычислительной машины | 1978 |

|

SU728129A1 |

| ПРОЦЕССОР | 1990 |

|

SU1826787A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Система обработки данных | 1980 |

|

SU1003063A1 |

Авторы

Даты

1974-07-30—Публикация

1971-11-01—Подача