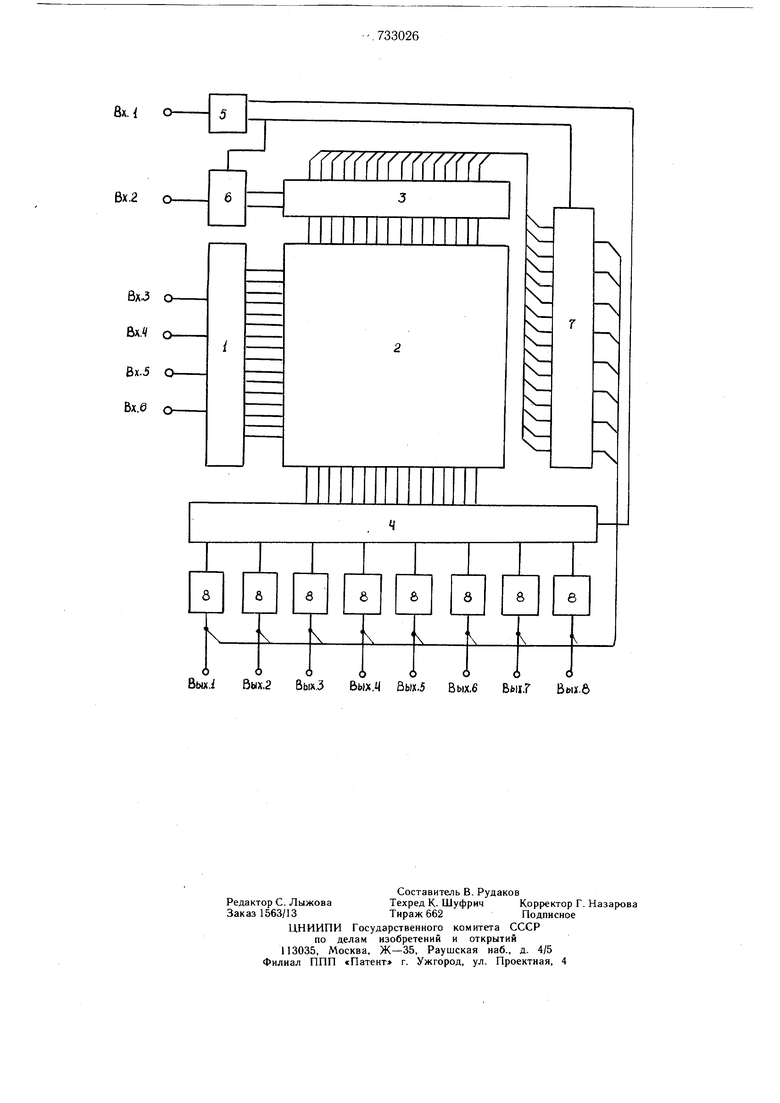

го через дешифратор слов с первым выходом блока управления, и выходные усилители, введены дешифратор разрядов и инверторы, входы которых соединены со вторым выходом блока управления, а выходы подключены соответственно к матричному накопителю и выходным усилителям, выходы которых соединены ,со входами дешифратора разрядов, управляющий вход которого подключен к первому выходу блока управления, а выходы дешифратора разрядов соединены с соответствующими входами селектора. На чертеже изображена блок-схема предлагаемого программируемого постоянного запоминающего устройства. Выходы входного дешифратора 1 присоединены к соответствующим входам выборки строки матричного накопителя 2, ко входам выборки слов/разрядов которого подключены выходы селектора 3. Выходы накопителя 2 соединены со входами инверторов 4, к дополнительному входу которых подсоединен второй выход блока 5 управления, первый выход которого связан с дополнительным .выходом дешифратора 6 слов и с дополнительным входом дешифратора 7 разрядов. Первый и второй выходы дешифратора 6 слов соединены с первым и вторым входами селектора 3, остальные входы которого объединены с соответствуюшими выходами дешифратора 7 разрядов. Выходы инверторов 4 соединены со входами усилителей 8 выхода. Выходы ППЗУ присоединены ко входам дешифратора 7 разрядов. Предлагаемое программируемое постоянное запоминаюш,ее устройство работает в режимах записи, хранения и считывания информации. В режиме записи информации подача входного сигнала логической «1 на вход 1 блока 5 управления переводит ППЗУ в режим необращения, при котором производится запись информации. Выходные сигналы блока управления блокируют инверторы 4 и дешифратор 6 слов, запрещая подачу адресного кода управления селектором 3 и считывание информации через инверторы 4, одновременно подается разрешающий сигнал на дешифратор разрядов 7. Инверторы 4 устанавливают выходы усилителей выхода 8 ППЗУ в состояние логической «1. Комбинацией входного кода на входном дешифраторе 1 выбирается строка матричного накопителя. На выходы Вых. .8 ППЗУ, соединенные со входами дешифратора, разрядов 7, подается комбинация логических сигналов, в соответствии с которой дешифратор 6 разрядов вырабатывает выходной код, управляющий выбором селектором 3 определенного разряда выбранной строки накопителя 2, в который производится запись информации. Запись логической «I производится подачей импульса тока питания накорителя. который пережигает плавкую перемычку ячейки выбранного разряда (цепи питания на блок-схеме условно не показаны). Запись логического «О определяется наличием плавкой перемычки, и импульс тока при этом в выбранную ячейку не подается. Перебором комбинаций логических сигналов на выходах Вых. .8 и, следовательно, на входах дещифратора разрядов 7 выбираются последовательно адреса всех ячеек выбранной строки матричного накопителя и записывается информация в соответствии с заданной программой. Комбинации кода на входах Вх.З-Вх.6 входного дешифратора 1 обеспечивают перебор всех строк накопителя 2. В режиме записи работают входной дешифратор 1, блок 5 управления, дешифратор 7 разрядов, селектор 3, матричный накопитель 2. В режиме считывания информации в ППЗУ поступающий на входы Вх.З-Вх.6 входного дешифратора 1 входной код преобразуется в адресный, подаваемый на входы накопителя 2 и возбуждающий одну из строк. На вход Вх.2 дешифратора 6 слов приходит сигнал обращения к одному из слов выбранной строки накопителя. Адресный код с дешифратора слов поступает в половину селектора 3, работающую при считывании, и подготавливает к считыванию выбранное слово. Таким образом, наличие адресной информации на входах Вх.З-Вх.6 входного дешифратора и входе Вх.2 дешифратора слов в сочетании с разрешающим сигналом логического «О на входе Вх.1 блока 5 управления выбирают в матричном накопителе и подготавливают к считыванию ячейки одного слова. Считывание информации начинается при поступлении на инверторы 4 разрещающего сигнала с блока 5 управления. Инверторы 4 производят опрос подготовленных к считыванию информации ячеек слова, и считываемую информацию поразрядно в параллельном коде передают на входы выходных усилителей 8. Следует отметить, что в режиме считывания информации схемы дещифратора 7 разрядов часть схемы селектора 3, работающая только при записи, находится в обесточенном состоянии, что дает заметную дополнительную экономию по току потребления. Блок 5 управления в зависимости от сигнала на входе Вх.1, выдает сигналы разрешения считывания информации, а при записи информации вырабатывает два управляющих сигнала, один из которых разрешает работу дешифратора 7 разрядов с одновременным запрещением работы дешифратора 6 слов, второй сигнал запрещает считывание информации инверторами 4. Введение новых блоков в ППЗУ, а также наличие новых связей между ранее существовавшими блоками обеспечивает снижение потребляемой мощности на единицу информации, улучшение теплового режима кристалла и фактора качества (произведение мощности потребления на время задержки распространения сигнала), а также повышение надежности устройства и степень интеграции на кристалле. Логическое управление в цепи записи информации через выходы ППЗУ и введение дополнительных цепей между блоками ППЗУ и матричным накопителем, а также возможность отключения части устройства, работающей только при записи, от цепей питания приводит к дополнительному снижению мощности потребления и требований к параметрам элементов, а также к улучшению температурного режима кристалла. Уменьшение напряжения программирования запоминающей матрицы значительно снижает требования к пробивным напряжениям транзисторов и размерам элементов матрицы. Использование трехпроводной схемы обращения к запоминающей матриде с управлением по двум линиям и считыванием по третьей позволяет разделить цепи записи и считывания, уменьщить число элементов и протяженность цепей протекания значительных по величине токов записи информации.

Формула изобретения

Программируемое постоянное запоминающее устройство, содержащее матричный накопитель, входы которого соединены с выходами дешифратора строк и селектора, соединенного через дешифратор слов с первым выходом блока управления, и выходные усилители, отличающееся тем, что, с целью повышения И11формационной емкости и снижения потребляемой мощности устройства за счет разделения каналов записи и считывания, в него введены дешифратор разрядов и инверторы, входы которых соединены со вторым выходом блока управления, а выходы подключены соответственно к матричному накопителю и выходным усилителям, выходы которых соединены со входами дешифратора разрядов, управляющий вход которого подключен к первому выходу блока управления, а выходы дешифратора разрядов соединены с соответствующими входами селектора.

Источники информации,

принятые во внимание при экспертизе 1. MCI-LSI Memory. Каталог. 1975, серии 5330, 5331, 6330, 6331, с. 97, рис. В132.

2. «Электронная промышленность, № 1, 1974, с. 23, рис. 4 (прототип). оО Вых. Вых.2 rrrrrrrrrrrrrrrr О6666О Вых.З Ьых.Ц аых.5 Выхб Вы. Вых.б

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1977 |

|

SU746731A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

| Полупроводниковое оперативное запоминающее устройство | 1985 |

|

SU1295446A1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU930388A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1795521A1 |

| Устройство для графического отображения синтезируемой устной речи | 1986 |

|

SU1411802A1 |

| Полупостоянное запоминающее устройство | 1975 |

|

SU611251A1 |

Авторы

Даты

1980-05-05—Публикация

1977-05-03—Подача