(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

1

Изобретение относится к области вычислительной техники и предназначено для многократной записи, хранения и многоразового считывания информации произвольно большого объема.

Известно постоянное запоминающее устройство (ПЗУ), содержащее накопитель, построенный на элементах на халькогенидных стеклах, и дешифратор-формирователь, выходы которого соединены со входами накопителя 1.

Недостатками устройства являются необходимость перестройки функциональной схемы при увеличении емкости накопителя, что требует введения внешних устройств коммутации выходных выводов ИМС и формирования по величине и длительности информационных сигналов при записи программы в накопитель, а также значительная потребляемая мощность.

Наиболее близким по технической сущности к изобретению является ПЗУ, содержащее матричный накопитель, первые входы которого соединены свыходами входного дешифратора, а также выходной усилитель и выходной дешифратор 2.

Недостатками ПЗУ являются одноразовое программирование и высокая мощность потребления на единицу информации, особенно Б режиме записи, что ухудшает температурный режим кристалла, накладывает повышенньЧе требования на размеры элементов, изоляцию между ними и усложняет технологию изготовления кристалла, а также длительное время программирования.

Цель изобретения заключается в повышении быстродействия ПЗУ и его надеж10ности.

Поставленная цель достигается тем, что в ПЗУ, содержащее накопитель, первые входы которого подключены к выходам входного дешифратора, выходной дешифратор и блок выходных усилителей, введены ком15мутатор тактовых сигналов разрядный формирователь, блок задания режимов записи и считывания, дополнительный дешифратор, селектор считываемого слова и формирователь информационных сигналов, выходы которого 20 подключены ко вторым входам накопителя, входы формирователя информационных сигналов соединены с соответствующими входами дополнительного дешифратора, выходного дешифратора и с первым и вторым выходами блока задания режимов записи и считывания, третий выход которого через разрядный формирователь подключен к третьим входам накопителя и ко входу селектора считываемого слова, выходы которого соединены с соответствующими входами блока выходных усилителей. Выходы дополнительного дешифратора подключены к соответствующим входам разрядного формирователя, выходы выходного дешифратора - к соответствующим входам селектора считываемого слова, а четвертый выход блока задания режимов записи и считывания через коммутатор тактовых сигналов - к одному из входов входного дешифратора.

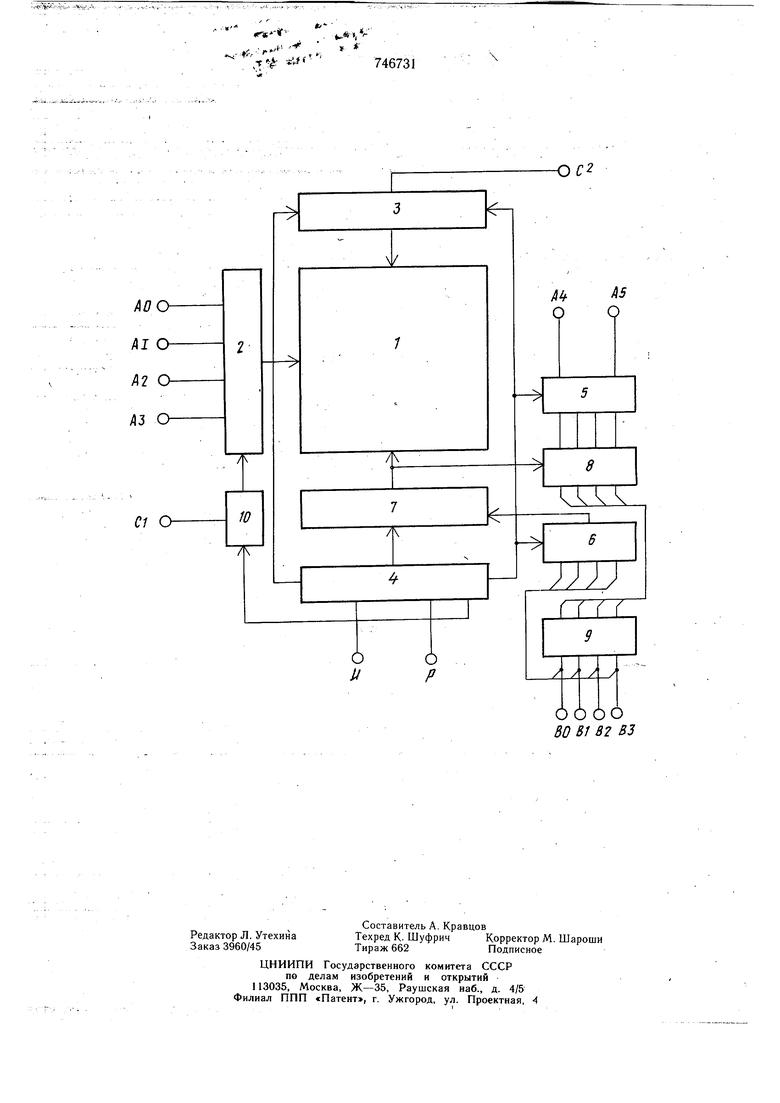

Структурная схема предлагаемого программируемого ПЗУ изображена на чертеже.

Первые входы накопителя 1 соединены с выходами входного дешифратора 2, вторые - с выходами-формирователя информаДйонйы: сигналов 3, ко входам которого ггодсоединены два выхода блока задания режимов записи и считывания 4, входы выходного Дешифратора 5 и входы доцолнительHbfp дешифратора 6. Третьи входы накопителя 1 соединены с выходами разрядного формирователя 7 и со входами селектора считываемого слова 8. Выходы дешифратора 5 подсоединены ко входам селектора 8.

Выходы селектора 8 подключены ко входам блока выходных усилителей 9, выходы которого объединены со входами дешифратора 6. Выходы дешифратора 6 соединены со входами формирователя 7, ко второму входу которого подключен третий выход блока задаиия режимов записи и считывания 4 четвертый выход которого связан со входом коммутатора тактовых сигналов 10, выход которого подключен к соответствующему входу дешифратора 2. Предлагаемое ПЗУ работает в режимах записи и считывания информации, а также обеспечивает хранение записанной информации как угодно долго при отключении тока питания.

Приход сигнала логического «О на вход «Р блока задания режимов записи и считывания 4 определяет переход ПЗУ в режим записи информации. Выходной сигнал блока 4 блокирует передачу импульсов синхронизации от входа CI на дешифратор 2 в коммутатор тактовых сигналов 10. Одновременно блок 4 вырабатывает сигнал для подготовки к режиму записи дешифратора 6, формирователя 3, а также сигнал запрета адресной выборки слов дешифратором 5, чем перекрывается канал прохождения информационного сигнала с накопителя 1 через селектор 8 и блок выходных усилителей 9. На выходах блока усилителей 9 устанавливаются в этим случае потенциалы логической единицы, что необходимо для функционирования дешифратора 6, входы которого объединены с выходами блока 9.

Поступающий на входы АО-A3 дешифратора 2 сигнал преобразуется в адресный

код, возбуждающий одну из строк накопителя 1. Адресный сигнал выборки разряда подается на входы дешифратора 6 через выводы ВО-ВЗ и далее управляет формирователем 7, осуществляющим выбор разряда накопителя 1, в который будет внесена информация, приходящая на вход И блока 4. Одновременно блок 4 вырабатывается сигнал, поступающий на формирователь 3 для формирования из импульса С2 импульса тока, по длительности соответствующего записываемой в ячейку накопителя информации: короткий импульс при записи «1 и длинный при записи «О.

Для записи информации в накопитель необходимы нормированный по амплитуде и времени действия ток записи, соответствующий записываемой информации и сочетание входных сигналов, определяющих режим записи ПЗУ, и адреса соответствующих ячеек накопителя.

Поступление входного сигнала «1 на вход блока 4 переводит ПЗУ в режим считывания с отключением блоков и цепей, участвующих только при записи информации.

Управляющий сигнал с блока 4 запрещает прохождение сигнала с дешифратора б на формирователь 7 и отключает накопитель 1 от токозадающих цепей блока 4 для предупреждения процесса ложной записи информации. Одновременно разрешается работа дешифратора 5, управляющего цепями считывания информации (селектором считываемого слова 8, блоком выходных усилителей 9) и блокируется формирователь 3.

В режиме считывания работа устройства определяется тактовым сигналом С1, который формируется коммутатором 10. Адресный код, поступающий на входы АО-A3 дешифратора 2, преобразуется дешифратором и за время действия синхроимпульса С1, которое значительно короче времени записи информации, возбуждает определенную строку накопителя 1. Отсутствие синхросигнала CI запрещает адресную выборку строки накопителя. Входной код по входам А4-А5 дешифратора 5 вырабатывает адресный код выборки селектором 8 иеобходимых разрядов считываемого слова с возбужденной строки накопителя.

Считанное слово поступает на усилитель 9 и в параллельном коде на выходы ПЗУ ВО-ВЗ. Динамическое считывание слова информации осуществляется только за время действия синхроимпульса CI и обусловлено структурой и режимом работы запоминающих ячеек накопителя.

Функциональня схема ПЗУ универсальна по своей структуре построения и допускает сколь угодно большое увеличение емкости ПЗУ и разрядности считываемого слова без изменения функциональной схемы. Построение накопителя на запоминающих

элементах на халькогенндных стеклах обеспечивает большое число повторных записей и считывания информации с длительным хранением ее при отключении питания ПЗУ.

Предварительная подготовка при считывании информации нужного адреса входным дешифратором и выборкой его с приходом синхроимпульса CI обеспечивает повышение быстродействия ПЗУ.

Введение в функциональную схему ПЗУ формирователя информационного сигнала позволяет из одного входного сигнала С2 формировать два нормированных по величине и длительности сигнала записи «1 или «О. Это позволяет уменьшить общее количество входов ПЗУ.

Введение в функциональную схему ПЗУ блока задания режимов записи и считывания, коммутатора тактовых сигналов, формирователя информационного сигнала и соответствующих связей между ними позволяет оптимизировать построение функцнональной схемы и при ее универсальности повь1сить быстродействие, надежность и улучщить температурный режим кристалла ПЗУ.

Формула изобретения

Постоянное запоминающее устройство, содержащее накопитель, первые входы которого подключены к выходам входного дещифратора, выходной дещифратор и блок выходных усилителей, отличающееся тем.

что, с целью повышения быстродействия устройства и его надежности, оно содержит коммутатор тактовых сигналов, разрядный формирователь, блок задания режимов записи и считывания, дополнительный дещифр тор, селектор считываемого слова и форI мйрователь информационных сигналов, выходы которого подключены ко вторым входа1М накопителя, входы формирователя информационных сигналов соединены с соответствующими входами дополнительного дещифратора, выходного дешифратора и с первым и вторым выходами блока задания режимов записи и считывания, третий выход которого через разрядный формирователь подключен к третьим входам накопителя и ко входу селектора считываемого слова, вы5 ходы которого соединены с соответствующими входами блока выходных усилителей, выходы дополнительного дешифратора подключены к соответствующим входам разрядного формирователя, выходы выходяоро де-, шифратора соединены с соответствующими входами селектора считываемого слова, а четвертый выход блока задания режимов записи и считывания через коммутатор тактовых сигналов подключеи к одному из,вхо-. дов входного дещнфратора.

iИсточники информации,

принятые во внимание при экспертизе

1.MCi-LSI Мемогу Д. А. Т. А Book, 1976 editio i 10, pp. 113.

2.MCI-LSI Мемогу Д. А. Т. А. Book, 1976 edition 10, p. 133 (прототип).

f ..,.и ;.

746731

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Программируемое постоянное запоминающее устройство | 1977 |

|

SU733026A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1288756A1 |

6666 3D B1 82 B3

Авторы

Даты

1980-07-05—Публикация

1977-12-30—Подача