.BTopojo, третьего, четвертого, пятого, шестого и седьмого сумматоров, при этом узел образования частного содержит элементы неравнозначности, и и ИЛИ,, причем первый и второй входы узла подключены к первым входам первого и второго элементов не1 равнозначности соответственно, третий вход узла подключен к вторым вхолйм первого и второго элементов неравнозначности и к первым входам

пятого,

четвертого(

:третьего,

шестого, седьмого и восьмого элементов неравнозначности, вторые входы которых подключены,к jleTBepToMy, пятому, шестому,седь- мому,, восьмому и девятому входам узла соответственно, первый вход первого элемента И подключен к прямому выходу седьмого элемента не.равнозначности, инверсный выход которого подключен к первому входу второго элемента И, второй вход которого подключен к второму входу второго элемента И и к прямому выходу четвертого элемента неравнозначности, инверсный выход которого подключен к первым входам третьего и четвертого элементов- И, второй вход которого подключен к прямому выходу .восьмого элемента неравнозначности, инверсный выход которого подключен к второму входу третьего элемента И третий вход которого подключен к третьим входам первого, второго и четвертого элементов И и к инверснo y выходу второго элемента неравнознфчности, прямой выход которого подключен к первым входам пятого, шестого,седьмого и восьмого элементов И, второй вход которого подключен к второму входу шестого элемента И и к инверсному выходу третьего элемента неравнозначности, прямой выход которого подключен к вторым входам пятогр и седьмого элементов И, третий вход которого подклю-

чен к инверсному выходу пятого элемента неравнозначности, прямой выход которого подключен к третьему входу пятого элемента И, третий вход Эосьмого элемента И подключен к выходу шестого элемента неравКозначности, инверсный выход которого подключен к третьему входу шестого элемента И,информационные входы: узла подключены к выходам девятого, десятого и одиннадцатого элементов не|з&внозначности соответственно, ервые входы которых подключены к дополнительному управляющему выходу узла и к прямому выходу первого элемента неравнозначности, инверсный выход которого подключен к дополни- тельному управляющему выходу узла, вторые входы девятого, десятого и одиннадцатого элементов неравнозначности подключены к выходам первого, второго и третьего элементов ИЛИ соответственно, первый вход которого .подключен к первым входам первого и второго элементов ИЛИ и к выходу третьего элемента И, второй ,вxoji первого элемента ИЛИ подключен к выходу второго элемента И и к второму входу третьего элемента ИЛИ, третий вход которого подключен к выходу шестого элемента И и к второму входу второго элемента ИЛИ, третий вход которого подключен к выходу четвертого элемента И и к третьему входу первого элемента ИЛИ, четвер тый вход которого подключен к выходу первого элемента И, выход седьмого элемента И подключен к четвер- JEPiiy входу третьего элемента ИЛИ, , выход восьмого элемента И подключен к четвертому входу второго элемента ИЛИ.первый,второй,третий/четвертый, пятый, шестой, седьмой и вось1мой управлякядие выходы узла подключены к выходам первого, вось- мого, четвертого, седьмого, шес;ннотого, второго, третьего и пятого элементов И соответственно

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для деления десятичных чисел | 1984 |

|

SU1241235A1 |

| Устройство для деления двоичных чисел | 1981 |

|

SU1008733A1 |

| Устройство для деления двоичных чисел | 1984 |

|

SU1233139A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления двоичных чисел | 1982 |

|

SU1103224A1 |

| Устройство для вычисления элементарных функций | 1974 |

|

SU560229A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных арифметических устройствах для быстрого деления двоичных чисел, представленных в дополнительном коде.

Известно устройство для деления ДВОИЧНЫХчисел, формирующее в каждом цикле К цифр 4acTHoro.(k 2, 3,4,5,...) и содержащее регистры делимого и делителя, регистр частного с цепью сдвига, блок умножения, вычитатель, шифратор предсказания k цифр частного, регистр адреса, блок памяти, регистры верхнего и нижнего значений k цифр

частного, группы элементов И, причем входы шифратора предсказания k цифр частного соединены с выходами k старших разрядов регистров делимого и делителя 1 .

Недостатками известного устройстг эа являются невозможность деления чисел в дополнительном коде и низкое быстродействие ввиду большой длительности цикла формирования i цифр частного (k цифр частного в известном устройстве формируются по многотантному принципу: минимал ное число тактов в цикле равно 2, максимальное ( k + 1) . Наиболее близким по технической сущности к предлагаемому является устройство для деления чисел, содержащее регистры делимого и делителя, регистр частного с цепью сдв га, сумматор, коммутатор и узел об зования цифр частного, причем выход регистра делимого соединен с первы входами сумматора и коммутатора, второй вход сумматора соединен с выходом регистра делителя, а выход соединен с вторым входом ком мутатора, выходы знаковых разрядов регистров делимого и делителя, а также сумматора соединены с входами узла образования цифр частного, управляющие входы регистров делимого, делителя и частного, коммута тора и узла образования цифр частного соединены с входом устройства, выход узла образования цифр частного соединен с входом младааего разряда регистра частного I Недостатками известного устройс ва являются невозможность деления чисел в дополнительном коде и низкое быстродействие, вызванное в первую очередь тем, что в каждом цикле работы устройства формируется только одна двоичная цифра част ного. Цель изобретения - повышение бы родействий путем одновременного фop рования в цикле нескольких двоич|ных цифр частного и расширение области применения за счет возможнос деления чисел в дополнительном код Поставленная цель достигается тем, что устройство для деления чи сел, содержащее регистры делимого и делителя, регистр частного, первый сумматор, первый коммутатор и узел образования частного, причем выход регистра делимого подключен к первым информационным входам пер вого сумматора и первого коммутатора, информационный выход первого сумматора подключен К второму информационному входу первого коммутатора, выход которого соединен с информационным входом регистра делимого, выходы знаковых разрядов регистра делителя и первого сумматора подключены к первому и второму входам узла образования частного соответственно, входы прие ма информации регистров делимого и делителя и вход приема и сдвига информации регистра частного подключе к управляющему входуустройства, дополнительно содержит второй,тре тий, четвертый, пятый, шестой и сумматоры и второй коммута-. тор, причем первые информационные входы второго и четвертого сумматоров подключены к выходу регистра делимого, первые информационные входы третьего и шестого сумматоров подключены к информационному выходу первого сумматора, первый информационный вход пятого сумматора подключен к информационному выходу второго сумматора и к третьему информационному входу первого коммутатора, четвертый, пятый, шестой и седьмой информационные входы которого подключены к информационным выходам четвертого, пятого, шестого и седьмого сумматоров, первый информационный вход которого подключен к информационному выходу третьего сумматора и к восьмому, информационному входу первого коммутатора, первый , второй, третий, четвертый, пятый, шестой, седьмой и восьмой, управляющие входы которого подключены к управляющим выхоДс1М узла образования частного соответственно, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый входы которого подключены к выходам знаковых разрядов . регистров делимого, второго, третьего, четвертого, пятого, шестого и седьмого сумматора соответственно, прямой и инверсный информационный выходы регистра делителя подключены к первому и второму информационным входам второго коммутатора, выход которого подклк чен к вторым информационным входам первого, второго, третьего, четвертого, пятого, шестого и седьмого сумматоров, первый, второй и третий информационные входы регистра частного подключены к информационным выходам узла образования частного соответственно, дополнительный управляющий выход занесения прямого и инверсного кодов которого подключен к дополнительному одноименному управляющему входу регистра частного и к одноименным управляющим входам второго коммутатора и первого, второго, третьего, четвертого, пятого, шестого и седьмого сумматоров, при этом узел образования частного содержит элементы неравнозначности, И и ИЛИ, причем первый и второй входцл узла подключены к первым, входам первого и второго элементов неравнозначности соответственно, третий вход узла подключен к вторым входам первого и второго элементов неравнозначности. и к первым входам третьего, четвёртого, пятого, шестого седьгАэго и восьмого элементов неравнозначности, вторые входы которых подключены к четвертому, пятому, шестому, седьмому, восьмому и девятому входам узЛа соответственно, первый вход первого элемента И подключей к прямому выходу седьмого элемента неравнозначности, инверсный выход которого подключен к первому входу второго элемента И, второй вход которого подключен к второму входу первого элемента И и к прямому выходу четвертого элемента неравнозначности, инверсный выход которого подключен к первым входам третьего и четвертого элементов И, второй вход которого подключен к прямому выходу восьмого элемента неравнозначности, инверсный.выход котрого подключен к второму входу третьего -элемента И, третий вход которого подключен к третьим входам первого, второго и четвертого элементов И и к инверсному выходу второго элемемта неравнозначности, прямой выход которого подключен к первым входам пятого/ шестого, седьмого и восьмого элементов И, второй вход которого подключен к второму входу шестого элемента И и к инверсному выходу третьего элемента неравнозначности, прямой выход которого подключен к вторым входам пятого и седьмого элементов И, третий вход которого подключен к инверсному пятого элемента неравнозначности, прямой выход которого подключен к тpeтьe 1y входу пятого элемента-И, третий вход восьмого элемента И подключен к прямому выходу шесто- го элемента неравнозначности, инверсный выход которого подключен к третьему входу шестого элемента П, информационные входы узла подключены к выходам девятого, десятого и одиннадцатого элементов неравнрэначности соответственно, первые входы которых подключены к дополнительному управляющему выходу узла и к прямому выходу.первого элемента неравнозначности, инверсный выход которого подключен к дополнительному управляющему выходу узла, вторые входы девятого, десятого и одиннадцатого элементов неравнозначности прдключены к выходам первого, второго и третьего элементов ИЛИ соответственно, первый вход которого подключен к первым входам,первого и второго элементов ИЛИ и к выходу третьего элемента И, второй вход первого элемента ИЛИ подключен к выходу второго элемента Инк второму входу третьего элемента ИЛИ, третий вход которого подключен к выходу шестого элемента И и к второму входу второго элемента ИЛИ, третий вход которого подключен к выходу четвертого элемента И и к третьему вход первого элемента ИЛИ, четвертый вход которого подключен к выходу первого элемента И, выход седьмого элемента И подключен к четвертому

входу третьего элемента ИЛИ, выход восьмого элемента И подключен к четвертому входу второго элемента ИЛИ, первый,второй,третий,четвертый,пятый, шестой,седьмой и восьмой управляющие выходы узла подключены квыходам первого, восьмого, четвертого, седьмого, шестого, второгр., третьего и пятого элементов И соответственно.

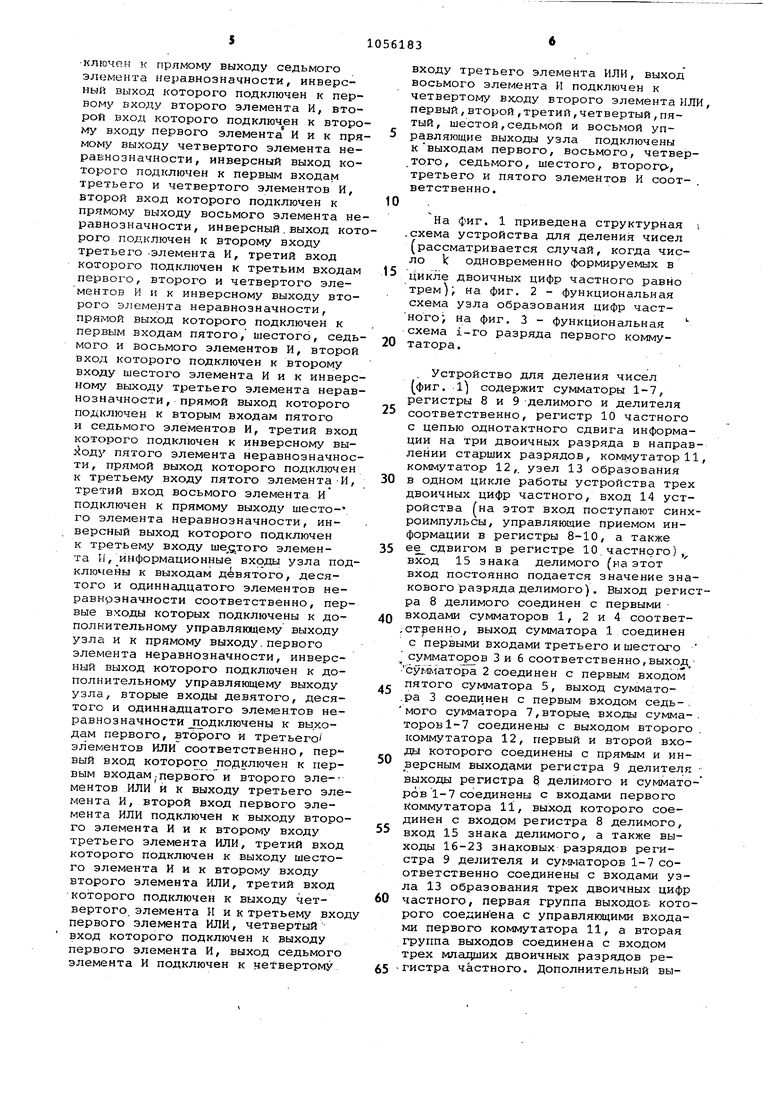

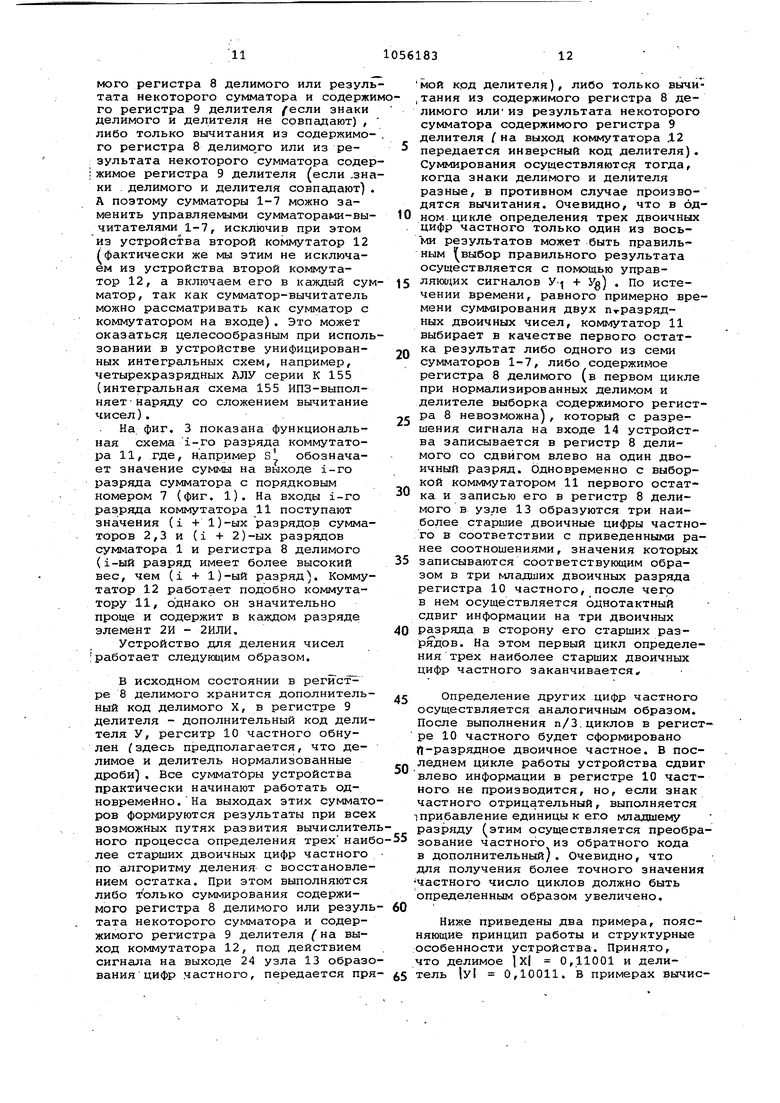

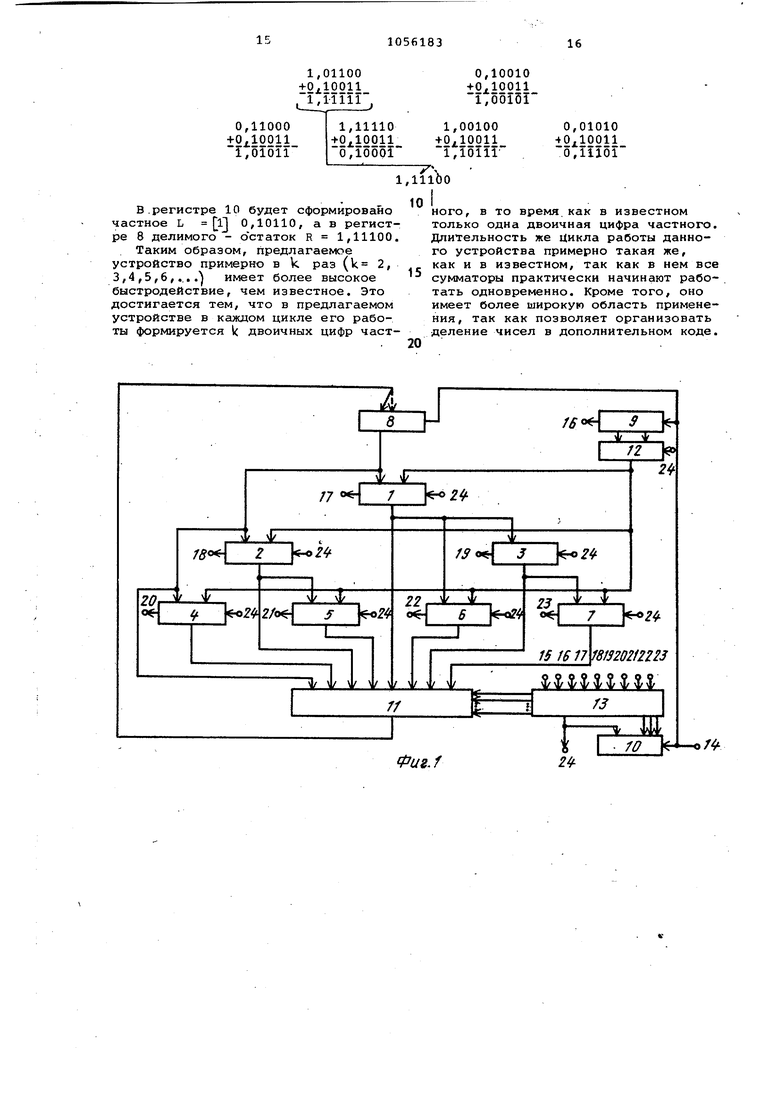

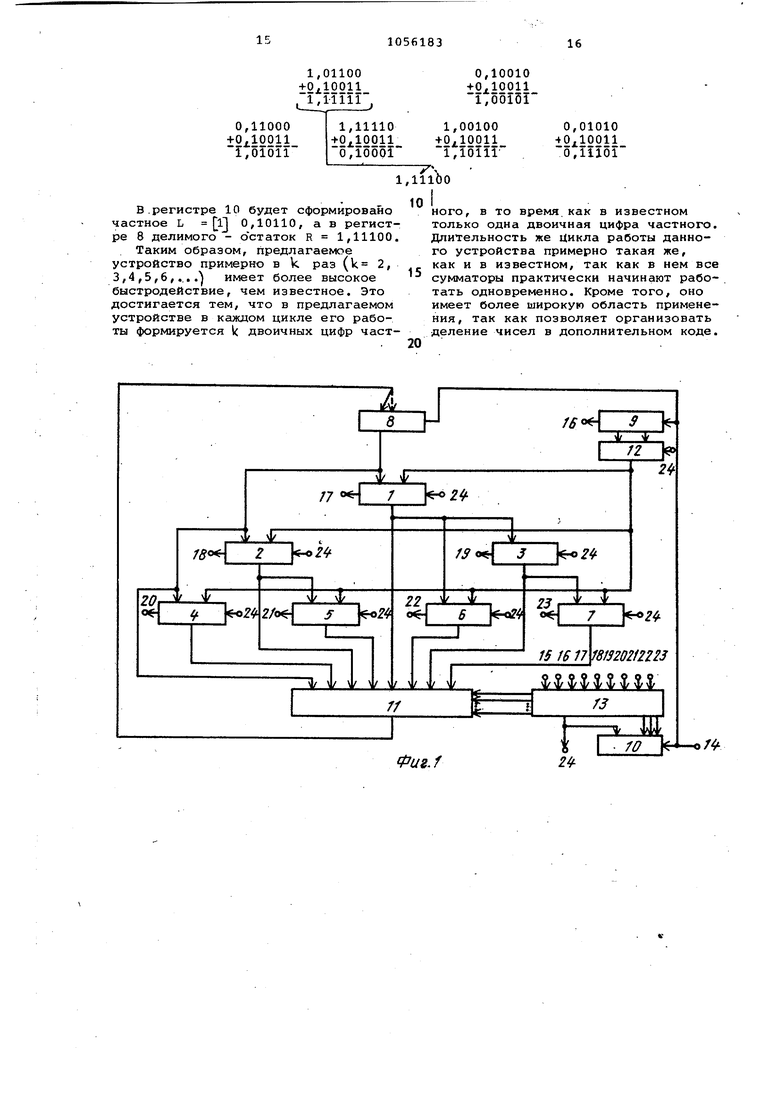

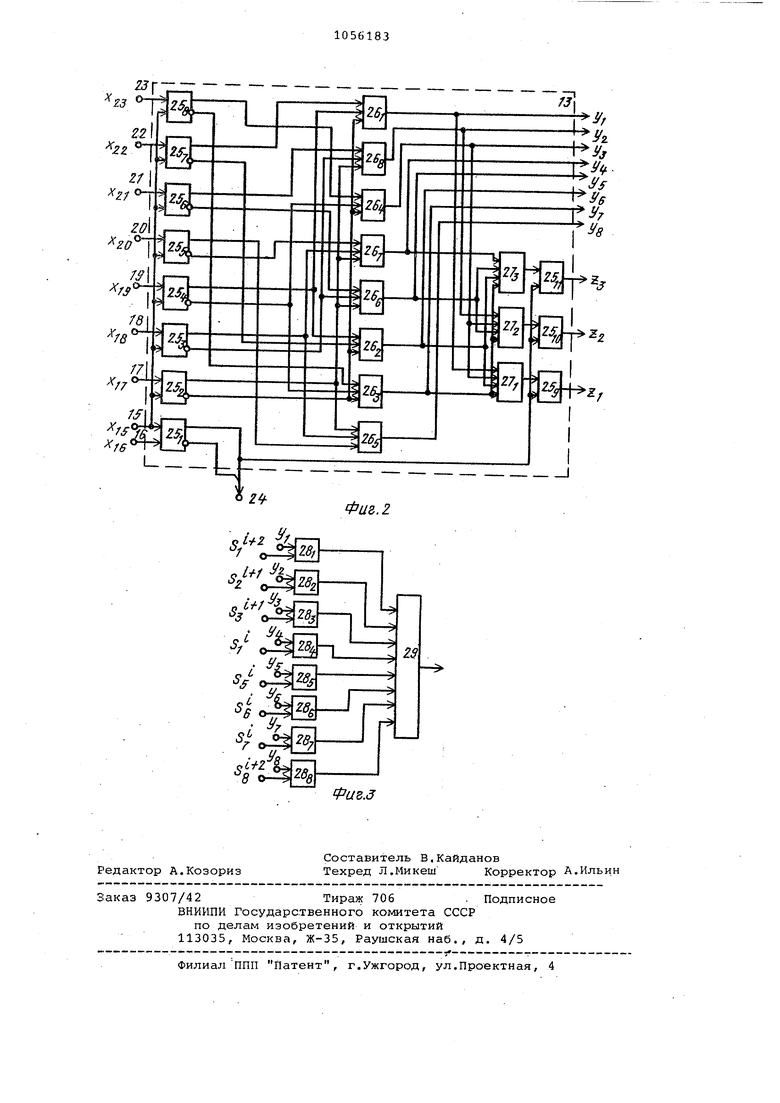

На фиг. 1 приведена структурная i .схема устройства для деления чисел (рассматривается случай, когда число k одновременно формируемых в

цикле двоичных цифр частного равно трем); на фиг. 2 - функциональная схема узла образования цифр частного на фиг. 3 - функциональная схема i-ro разряда первого комму0 татора.

Устройство для деления чисел фиг. 1) содержит сумматоры 1-7, регистры 8 и 9 делимого и делителя

5 соответственно, регистр 10 частного с цепью однотактного сдвига информации на три двоичных разряда в направлении старших разрядов, коммутатор 11, коммутатор 12,. узел 13 образования

0 в одном цикле работы устройства трех двоичных цифр частного, вход 14 устройства (на этот вход поступают синхроимпульсы, управляющие приемом информации в регистры 8-10, а также

5 ее сдвигом в регистре 10, частного) , вход 15 знака делимого (на этот вход постоянно подается значение знакового разряда делимого) . Выход регистра 8 делимого соединен с первыми

п входами сумматоров 1, 2 и 4 соответ,стренно, выход сумматора 1 соединен

с первыми входами третьего и шестого J сумматоров 3 и б соответственно,выход сур.шатора 2 соединен с первым входом

пятого сумматора 5, выход суммато.ра 3 соединен с первым входом седь-, мого сумматора 7,вторые входы сумма-, торов 1-7 соединены с выходом второго . коммутатора 12, первый и второй входы которого соединены с прямым и инверсным выходами регистра 9 делите.пя выходы регистра 8 делимого и сумматоров 1-7 соединены с входами первого коммутатора 11, выход которого соединен с входом регистра 8 делимого,

вход 15 знака делимого, а также выходы 16-23 знаковых разрядов регистра 9 делителя и сумматоров 1-7 соответственно соединены с входами узла 13 образования трех двоичных цифр

частного, первая группа выходов которого соединена с управлякядими входами первого коммутатора 11, а вторая группа выходов соединена с входом трех млад:5111их двоичных разрядов ре-гистра частного. Дополнительный выход 24 узла 13 образования трех двоичных цифр частного соединен с входом регистра 10 частного, с управляющим входом коммутатора 12 и с цепями входных переносов сумматоров 1-7.

В устройстве все регистры могут быть построены, например, на двутакных синхронных D-триггерах, а все сумматоры комбинационного типа - со сквозным либо ускоренным формированием разрядных переносов. С целью обеспечения максимально возможного быстродействия устройства в нем необходимо использовать сумматоры с ускоренным формированием разрядных

.переносов. Однако этого же быстродействия можно достичь при меньших аппаратурных затратах, если в устройстве испрльзовать сумматоры без распространения переносов ( сумматорв с сохранением переносов), организовав при этом ускоренное формирование переносов только в их знаковые разряды. Структура устройства

при этом не изменяется, если предполагать, что на выходной шине каждого сумматора результат формируется в двухрядном коде (т.е. в виде двух чисел), а регистр 8 делимого имеет такую разрядность, что обеспечивает хранение промежуточных остатков в двухрядном коде.

С ПОМОЩЬЮ сумматоров 1-7 формируются результаты при всех возможных путях развитии вычислительного .процесса определения трех двоичных

(Y + Y, 4 У, t У)ф(Х,уфХ„) (Y4 4 Y,- +- 7)®

цифр частного по алгоритму деления с восстановлением остатка. Чтобы отразить этот цепной (ветвящийся) процесс, сумматоры (фиг. 1) изображены в виде пирамиды. В первой

ступени этой пирамиды находятся сумматоры 4-7, во второй ступени сумматоры 2 - и 3 и в третьей ступени пирамиды расположен первой сумматор 1. Число ступеней пирамиды рав0 но числу одновременно формируемых в цикле двоичных цифр частного. Так, например, при значении |( 5 пирамида сумматора пятиступенчатая, причем ее первая ступень должна вклю5 чать шестнадцать сумматоров.

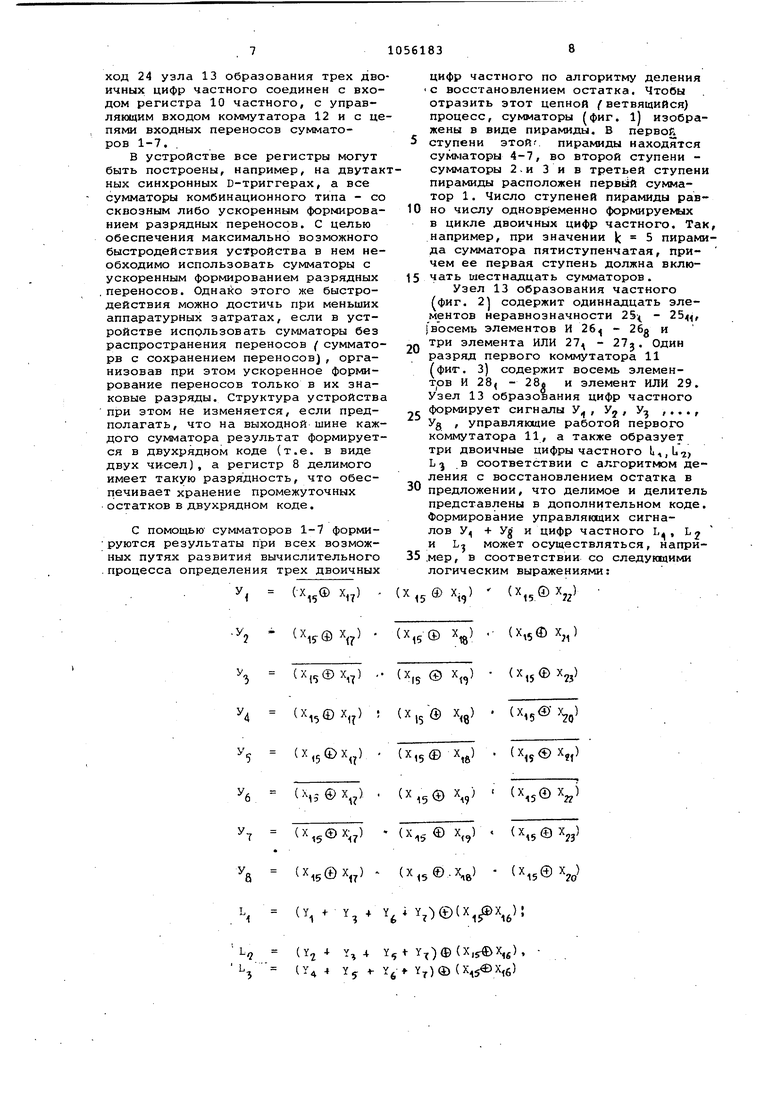

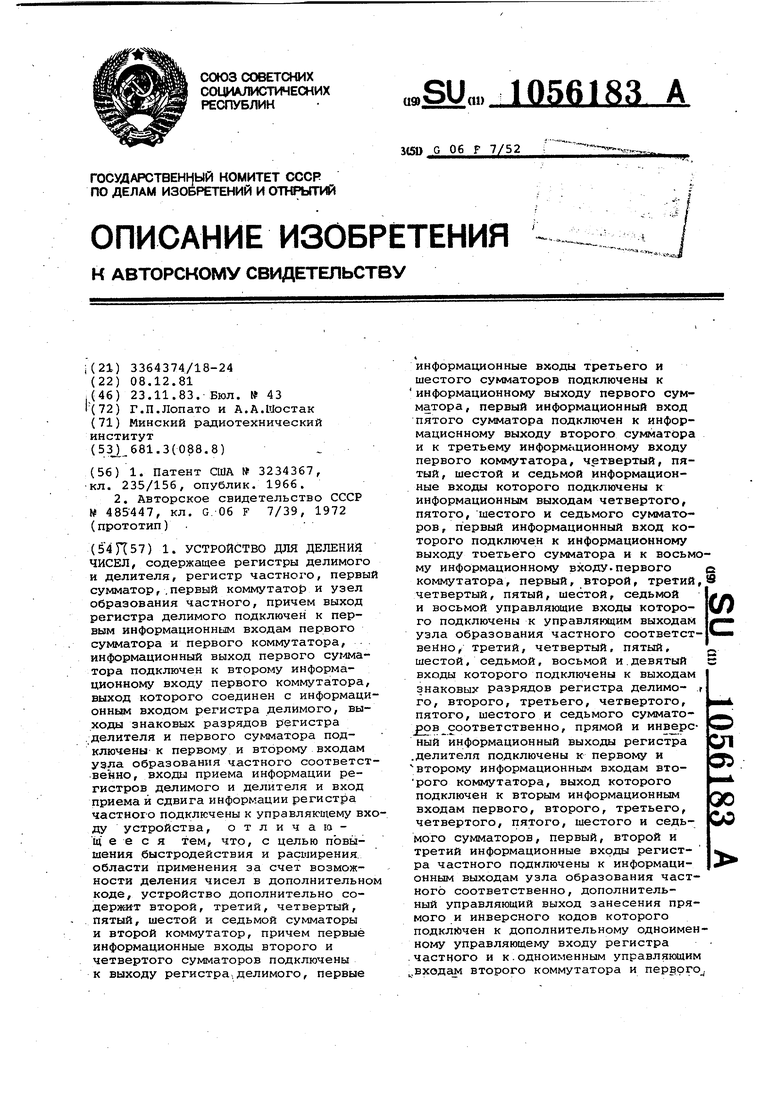

Узел 13 образования частного /фиг. 2| содержит одиннадцать элементов неравнозначности 25 - 25, восемь элементов И 26 - 26g и

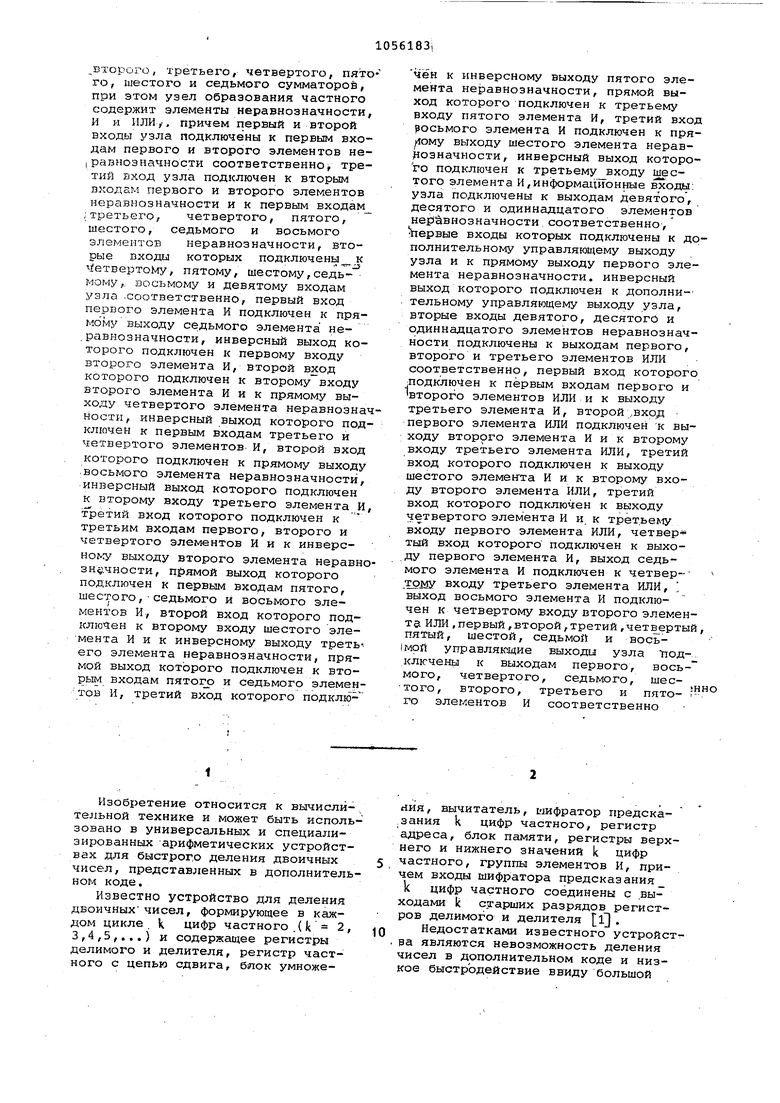

- три элемента ИЛИ 27 - 27j. Один разряд первого коммутатора 11 (фиг. 3) содержит восемь элемент ов И 28, - 28 и элемент ИЛИ 29. Узел 13 образования цифр частного

формирует сигналы У , Vj , У ,.. . , УЗ / управляющие работой первого коммутатора 11, а также образует три двоичные цифры частного L,,LV) L в соответствии с алгоритмом деления с восстановлением остатка в

0 предложении, что делимое и делитель представлены в дополнительном коде. Формирование управляющих сигналов У + yg и цифр частного L , 1-2 и L может осуществляться, напри5 ,мер, в соответствии со следующими логическим выражениями:

Здесь, например, через У-j обозна чен управляющий сигнал, под действием которого коммутатор 11 осуществляет выборку результата, сфоримрованного на выходе сумматора с порядковым номером 7 (фиг. 1), Х обозначает логическую переменную, равную значению знакового разряда на выходе 16 регистра 9 делителя ((х 1, если делитель отрицательный., в противном случа , 0), L,,, L соответственно старшая и вnaдшaя двбичные цифры частного из трех формируемых одновременно в цикле цифр.

сумматора 1

+ 100

+. 010 + 110

3 4 + 001 + 011

5 + 101

6

+ 111 1

й

регистра делимого

Кроме рассмотренных функций узел 13 образования цифр частного формирует на своём выходе 24 сигнаХ/15® Xfg) , которые,

лы Х, (X24 вo-пepвыx, управляют работой коммутатора 12 (если знаки делимого и делителя не совпадают, то на вход коммутатора 12 передается прямое значение делителя, в противном случае инверсное), во-вторых, формируют знаковый разряд частного (если знаки делимого и делителя не совпадают, то в соответствувдций разряд

На фиг, 2 приведена функциональ ая схема узла 13 образования цифр частного, работающая в соответствии с приведенными логическими выражениями. Эта схема, как и приведенные выше логические выражения, не является единственной, Возможны и другие ее модификации.

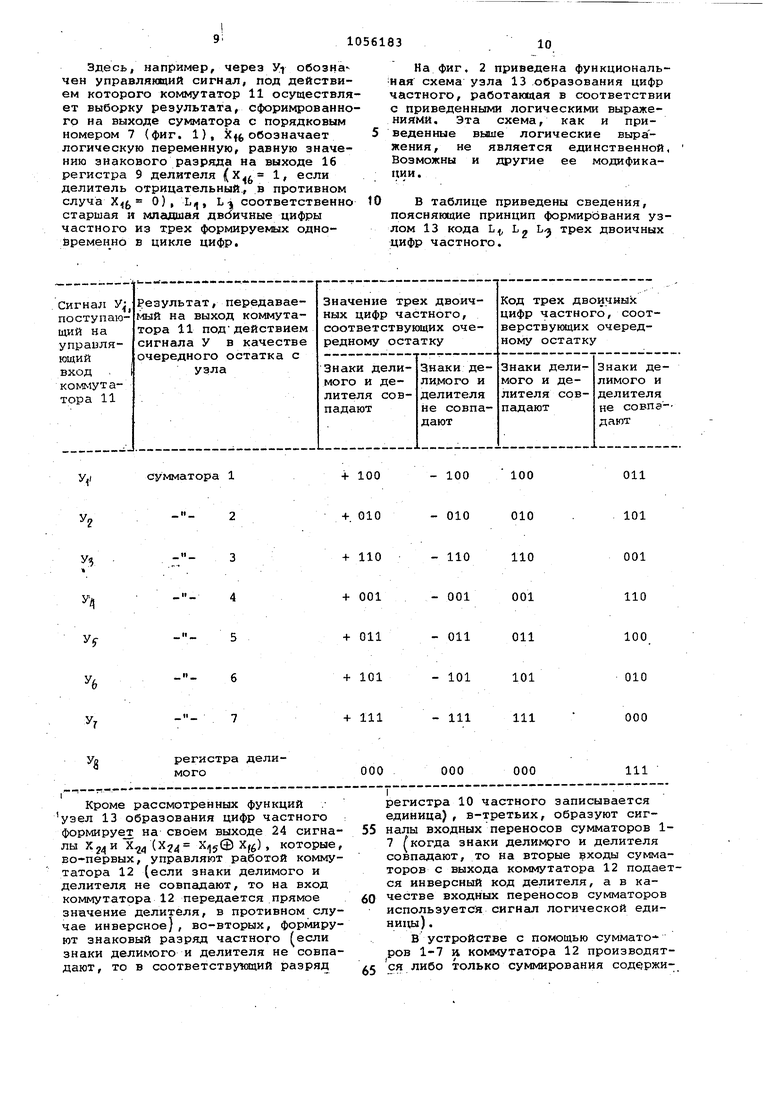

В таблице приведены сведения, поясняющие принцип формирования узлом 13 кода L, Lg L трех двоичных цифр частного.

100

- 100

011

101

010 001 110 001 110 011 100

101 010

111 000

111

000

000

регистра 10 частного записывается единица), в-третьих, образуют сигналы входных переносов сумматоров 17 когда знаки делимого и делителя совпадают, то на вторые входы сумматоров с выхода коммутатора 12 подается инверсный код делителя, а в качестве входных переносов сумматоров используется сигнал логической единицы) .

В устройстве с помощью сумматоров 1-7 и, коммутатора 12 производятся либо только суммирования содержимого регистра 8 делимого или резуль тата некоторого сумматора и содержи го регистра 9 делителя если знаки делимого и делителя не совпадают), либо только вычитания из содержимого регистра 8 делимо,го или из результата некоторого сумматора содер жимое регистра 9 делителя (если .зна ки . делимого и делителя совпадают) А поэтому сумматоры 1-7 можно заменить управляемыми сумматорами-вычитателями 1-7, исключив при этом из устройства второй коммутатор 12 /фактически же мы этим не исключаем из устройства второй коммутатор 12, а включаем его в каждый сум матор, так как сумматор-вычитатель можно рассматривать как сумматор с коммутатором на входе). Это может оказаться целесообразным при исполь зовании в устройстве унифицированных интегральных схем, например, четырехразрядных АЛУ серии К 155 (интегральная схема 155 ИПЗ-выполняет-наряду со сложением вычитание чисел). На фиг. 3 показана функциональная схема i-го разряда коммутатора 11, где, например s обозначает значение суммы на выходе i-ro разряда сумматора с порядковым номером 7 (фиг. 1). На входы i-ro разряда коммутатора 11 поступают значения (i + 1)-ых разрядов сумматоров 2,3 и (i + 2)-ЫХ разрядов сумматора 1 и регистра 8 делимого (i-ый разряд имеет более высокий вес, чем (i + 1)-ый разряд). Коммутатор 12 работает подобно коммутатору 11, однако он значительно проще и содержит в каждом разряде элемент 2И - 2ИЛИ. Устройство для деления чисел работает следующим образом. В исходном состоянии в регистре 8 делимого хранится дополнительный код делимого X, в регистре 9 делителя - дополнительный код делителя У, регситр 10 частного обнулен (здесь предполагается, что делимое и делитель нормализованные дроби). Все сумматоры устройства практически начинают работать одновремейно. На выходах этих суммато ров формируются результаты при всех возможных путях развития вычислител ного процесса определения трех наи лее старших двоичных цифр частного по алгоритму деления с восстановлением остатка. При этом выполняются либо т олько суммирования содержимого регистра 8 делимого или резул тата некоторого сумматора и содержимого регистра 9 делителя на выход коммутатора 12, под действием сигнала на выходе 24 узла 13 образ вания цифр .частного, передается пр мой крд делителя), либо только вычитания из содержимого регистра В делимого ИЛИиз результата некоторого сумматора содержимого регистра 9 делителя { на выход коммутатора .12 передается инверсный код делителя). Суммирования осуществляются тогда, когда знаки делимого и делителя разные, в противном случае производятся вычитания. Очевидно, что в одном цикле определения трех двоичных цифр частного только один из восьми результатов может быть правиль ным выбор правильного результата осуществляется с помощью управляющих сигналов У + У) . По истечении времени, равного примерно времени суммирования двух Птразрядных двоичных чисел, коммутатор 11 выбирает в качестве первого остатка результат либо одного из семи сумматоров 1-7, либо содержимое регистра 8 делимого (в первом цикле при нормализированных делимом и делителе выборка содержимого регистра 8 невозможна), который с разрешения сигнала на входе 14 устройства записывается в регистр 8 делимого со сдвигом влево на один двоичный разряд. Одновременно с выборкой комлф татором 11 первого остатка и записью его в регистр 8 делимого в узле 13 образуются три наиболее старшие двоичные цифры частного в соответствии с приведенными ранее соотношениями, значения которых записываются соответствующим образом в три младших двоичных разряда регистра 10 частного, после чего в нем осуществляется однотактный сдвиг информации на три двоичных разряда в сторону его старших разрядов. На этом первый цикл определения трех наиболее старших двоичных цифр частного заканчивается. Определение других цифр частного осуществляется аналогичным образом. После выполнения п/3.циклов в регистре 10 частного будет сформировано П-разрядное двоичное частное. В последнем цикле работы устройства сдвиг влево информации в регистре 10 частного не производится, но, если знак частного отрицательный, выполняется рибавление единицы к его младшему разряду (этим осуществляется преобразование частного из обратного кода в дополнительный). Очевидно, что для получения более точного значения частного число циклов должно быть определенным образом увеличено. Ниже приведены два примера, поясняющие принцип работы и структурные особенности устройства. Принято, что делимое Х| 0,11001 и делитель |у1 0,10011. Б примерах вычислення расположены подобно тому, как размещены сумматоры на структурной схеме устройства ( фиг. 1}. Из приведенных примеров видно, что при делении одних и тех же чисел с разнымк. знаками правильный вычислительный процесс развивается в одном и том же направлении. Использование в устройстве для деления чисел в

1Певрый цикл определения цифр частного

(0,1,0)

0,10100

+1 01101

о ,00001

0,00010

(-1 01101

1,01111

в регистре 10 будет сформировано; частное L 01010, а в регистре 8 делимого - остаток R 0,00100

Пример 2. ,.

Первый цикл1,00111

определения цифр частного +0 10011

(0,1,0)

0,01110

hOj lOOll

1,00001

0,00010

ю.юои

0,10101

Второй цикл

определения цифр частного

n,o,i)

дополнительном коде алгоритма с вос становлением остатка имеет в некоторых случаях существенное преимущество, так как остаток и частное всегда формируются правильно и не : требуется их дополнительная коррекция.

пример 1. , .

0,11001 н-1,01101

0,00110

1,01110 +1,01101 ОД101Г

1,10110 И 01101 1,00011

0,00100

(здесь знаковый разряд заключен в квадратик).

Пример 2., .

1,11010

1,0100 1-0,10011

otooTii

0,01110 +0 10011

Т,00001

в.регистре 10 будет сформировано частное L {}- 0,10110, а в регистре 8 делимого - остаток R 1,11100.

Таким образом, предлагаемое устройство примерно в k раз (k 2, 3,4,5,6,.... имеет более высокое быстродействие, чем известное. Это достигается тем, что в предлагаемом устройстве в каждом цикле его работы формируется 1 двоичных цифр част0,01010 40 10011

o,Tiioi

I

ного, в то время как в известном

только одна двоичная цифра частного. Длительность же Цикла работы данного устройства примерно такая же, как и в известном, так как в нем все

сумматоры практически начинают работать одновременно. Кроме того, оно имеет более широкую область применения, так как позволяет организовать деление чисел в дополнительном коде.

. f

2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3234367, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Двухтактный двигатель внутреннего горения | 1924 |

|

SU1966A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Прибор для автоматического контроля скорости поездов | 1923 |

|

SU485A1 |

| G | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-11-23—Публикация

1981-12-08—Подача