(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1012263A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1247898A2 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1649544A2 |

| Устройство для диагностики неисправностей цифровых блоков | 1981 |

|

SU1024925A1 |

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для поиска дефектов цифровых узлов | 1980 |

|

SU962957A1 |

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

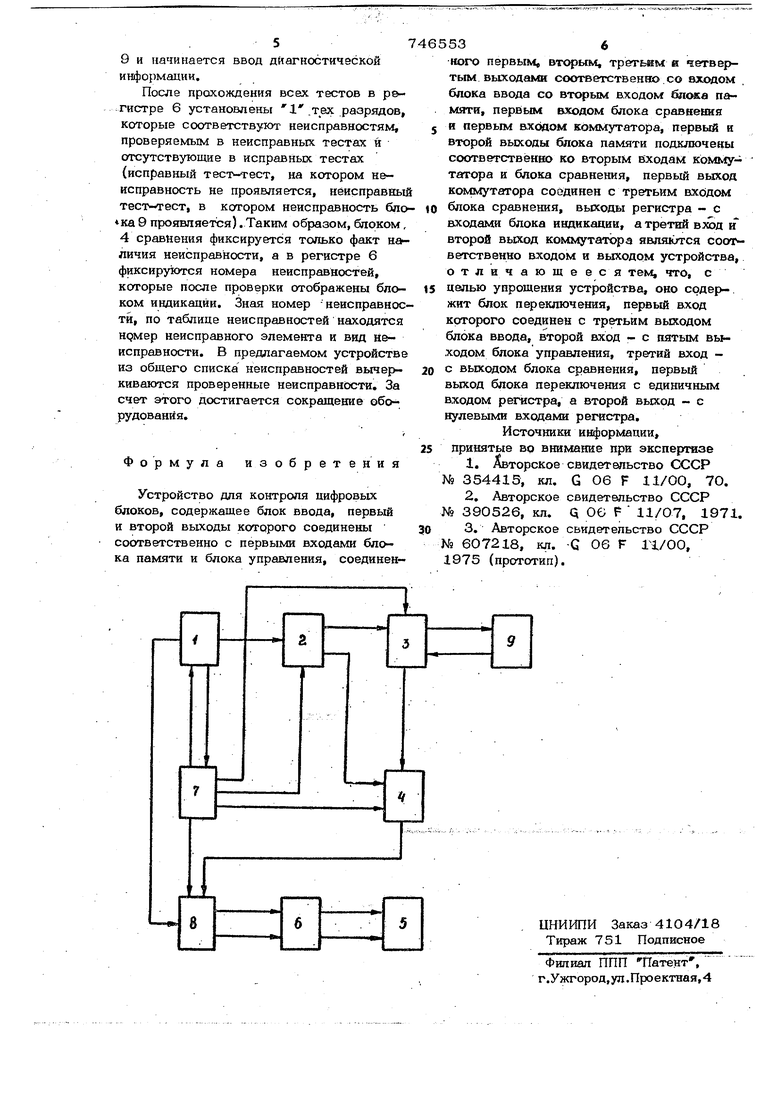

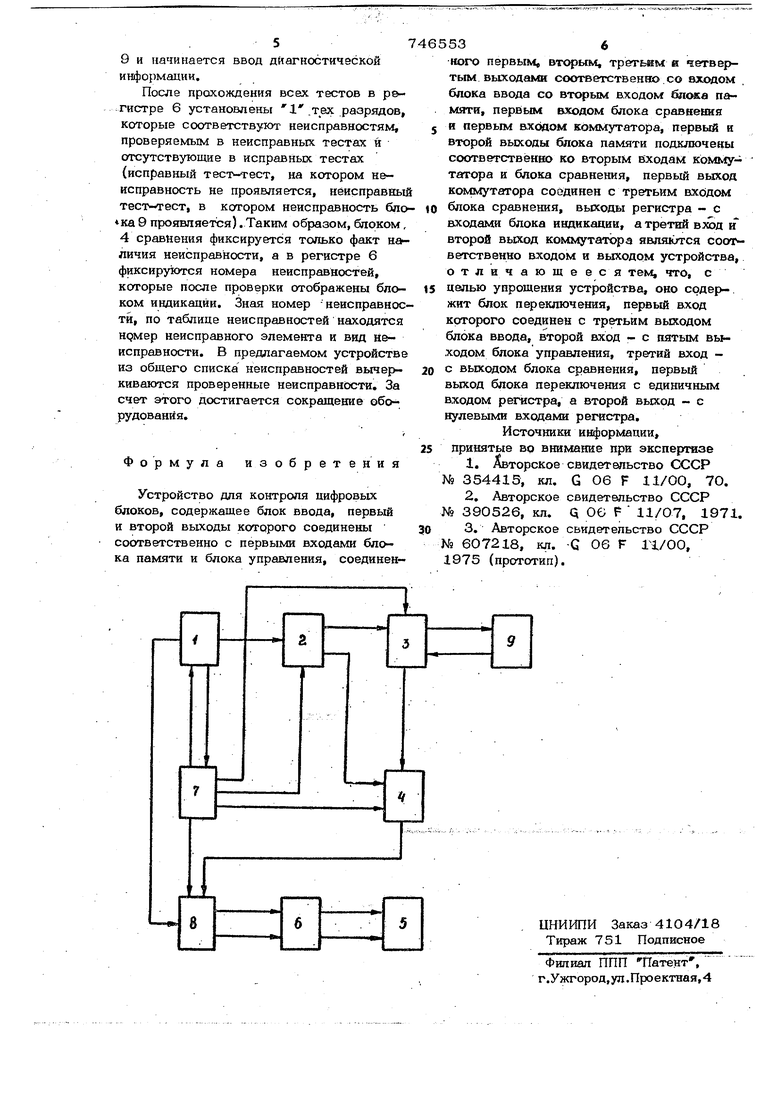

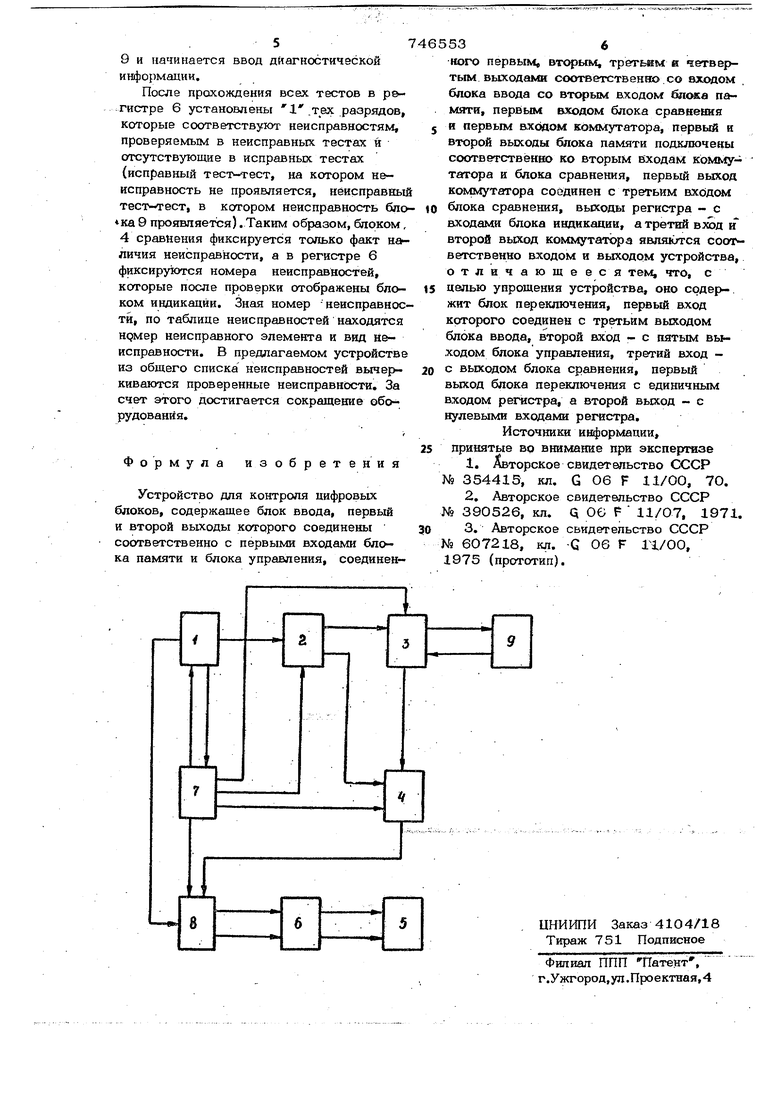

Изобретение относится к вьяислительной технике, в частности к устройствам тестового контрсшя логически.х схем и диагностики неисправностей. Известны устройства для контроля циф ровых блоков, содержащее блок ввода, блок сравнения, блок индикации, блок памяти l и 2 . Недостатком устройств является малая степень автоматизации поиска неисправностей, так как при наличии большего числа неудачных исходов тестов просмотр словаря неисправностей с целью локализации неисправного элемента занимает много времени. Наиболее близким техническим реш&нием к предлагаемому изобретению являе ся устройство контроля цифровых блоков содержащее последовательно соединенные блок управления, блок ввода, блок памяти, коммутатор, блок сравнения и регистры, подключенные к блоку ввода, Щ выкоды блока управления соединены со входами блоков памяти и сравнения et коммутатора |з. Однако это устройство сложно, так Как содержит два многоразрядных регистра, разрядность которых равна числу неисправностей. Целью предлагаемого изобретеш1я является упрощение устройства при cofxpia-. нении выссжой степени автоматизации поиска места неисправнсжти (локализации места неисправности). Цель достигается тем. что устройство для контроля цифровых блоков, содерHtamee блок ввода, первый и второй выходы которого соединены соответственно с первыми входами блока памяти и блока управления соединенного первым, вторым, третьим и четвертым выходами соответственно со входом блока ввода, со вторым входом блока памяти, первым входом блока сравнения и первым входом Коммутатора, первый и второй выходы блока памяти подключены соответственно ко вторым входам коммутатора н блоka сравнения, первый выход коммутатора соединен с третьим входом блока сравнения выходы регистра со входами блока индикации, а третий вход и второй выход коммутатора являются с оответст венно входом и выходом устройства, содержит блок переключения, первый вход которого соединен с третьим выходом блока ввода, второй вход- с пятым выходом блока управления, третий входс выходом блока сравнения, первьй выкод блока переключения с единичными входами регистра, а вькод - с нулевыми входами регистра. На чертеже изображена схема устройс ва. .. ,, Устройство содержит блок 1 ввода, блок 2 памяти, коммутатор 3, блок 4 сравнения, блок 5 И1щикации, регистр 6, блок 7 управления, блок 8 перёкл1очения и контролируемый блок 9. Блок 1 ввода предназначен дпя ввода с перфолетггы тестовой информации, инфо мации с входных (выходных) контактов, информации о проверяемых неисправностя (перечень--прсверяемых неисправностей), диагностической информации (номера неисправностей, проверяеШэЕх в канодом тес те) н командной ин4)0рмации. Блок 2 памяти предназначен для хранения и выдачи через коммутатор 3 на блок 9 тестовой информации. Блок памяти 2 разделен на две зоны: в одной хранятся сти1 Еулы (набор подаваемой на входные контакты блоков), во второй эталоны 5 (значешш сигналов, которые должны появиться на выходах блока 9, если он исправлен). Koм iyтaтop 3 предназначен для коммутации внешних контактов блока 9, при этом входные контакты подключаются к выходам блока 2 памяти (к той части, где хранятся сти ч1улы), выходныеконтакты подключаются ко входам блока 4 сравнения. Блок 5 индикации предназначен для индикации номера цегйсНравности В регистре 6 фиксируются номера обнаруженных неисправностей. БЛОК 8 переключения переключает диагностическую информацию на нулевые или единичные входы регистра 6. Устройство работает следующим обра зом. В исходном состояши блок 2 памят и регистрб по командам с блока 7 установлены в нулевое состояние (дёпй сброса не показаны). Вначале с ёлока вводится информация с проверяемьгх нейо 74 4 правностях и по командам с блока 7 через блок 8 записывается в регистр 6. Информация о проверяемых неисправноетях является перечнем неисправностей, проверяемых в блоке 9 Разрйдность регистра 6 равна мшссимальному количеству проверяемых неисправностей блоков 9, При вводе информации о проверяемых неисправностях соответствующие разряды регистра 6 устанавливаются в 1, я-ый разряд регистра 6 устанавливаете в 1, если J-ая неисправность проверяется в данном, обьекте контроля. После подготовки регистра 6 по командам с -блока 7 тестовая информация (стимулы и эталоны) записываемся в блок 2. Стимулы из блока 2 памяти поступают через коммутатор 3 на входы блока 9, а эталоны на первые выходы блока 4 сравнения. Управление работой Коммутатора ,3 осуществляется по сипналам из блока 7 управления. По результатам сравнения, если контролируемый блок исправлен, появляется высокий потенциал на выкоде блока 4 сравнения. -Посла подачи на входы блока 9 очередного набора по команде из бяока 7 управления из блока 1 вводится диагностическая информация, которая через блок 8 поступает на установку в О разрядов регистра 6. Диагностическая информация представляет позиционный код, длина которого (разрядность) равна общему количеству проверяемьгх неисправностей. Каждому номеру неисправности из списка неисправностей соответствует .один разряд позиционного кода, причем только в разрядах позиционного кода , ссю ветствующих проверяемым в данном тесте неисправностям, записаны 1. Каждому тестовому набору соответствует своя диагностическая информация. Если в очередном тесте не обнаружены неисправности (на выходе блока сравнения ), то разряды регистра 6, соответствующие коду диагностической информации данного теста, устанавливаются в О. Сигнал на вькоде блока 4 сравнения разрешает запись диагностической информации в регистр 6. Если же в очередном тесте обнаружена неисправность, то установление в О разрядов регистра б не происходит. После ввода диагностической информации по командам с блока 7 управления в блок .2 памяти вводится следующий тест, который поступает затем на входы блока

9 и начинается ввод диагностической информации.

После прохождения всех тестов в регистре 6 установлены . разрядов, которые соответствуют неисправностям, проверяемым в неисправных тестах и отсутствующие в исправных тестах (исправный , на котором неисправность не проявляется, неисправный тест-тест, в котором неисправность бло ка9 проявляется).Таким образом, блоком, 4 сравнения фиксируется только факт наличия неисправности, а в регистре 6 фиксируются номера неисправностей, которые после проверки отображены блоком индикации. Зная номер неисправности, по таблице неисправностей находятся нрмер неисправного элемента и вид неисправности. В предлагаемом устройстве из общего списка неисправностей вычеркиваются проверенные неисправности. За счет этого достигается сокращение обо рудованйя.

Формула изобретения

Устройство для контроля цифровых блоков, содержащее блок ввода, первый и второй выходы которого соединены

соответственно с первыми входами блока памяти и блока управления, соединенного первым, вторым, третьим к четвертым выходами соответственно со входом блока ввода со вторым входом блока памяти, первым &ХОДОМ блока сравкешся и первым axdtaoM коммутатора, первый к второй выходы блока памяти подключены соответственно ко вторым входам коммутатора и блока сравнения, первый выход коммутатора соединен с третьим входом блока сравнения, выходы регистра - с входами блока индикации, а третий вход и второй выход коммутатора являются соответственно входом и выходом устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит блок переключения, первый вход которого соединен с третьим выходом блока ввода, второй аход - с пятым выходом блока управления, третий вход с выходом блока сравнения, первый выход блока переключения с единичным входом регистра, а второй выход - с нулевыми входами регистра.

Источники информации, принятые во внимание при экспертизе

№ 354415, кл. G 06 F 11/00, 70.

№ 390526, кп. Q OG F 11/07, 1971

Авторы

Даты

1980-07-05—Публикация

1978-05-03—Подача