(54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОМПОНЕНТ ТЕНЗОРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU1136147A1 |

| Устройство для преобразования сферическихКООРдиНАТ B пРяМОугОльНыЕ | 1978 |

|

SU805308A1 |

| Арифметическое устройство | 1979 |

|

SU796844A1 |

| Вычислительное устройство | 1988 |

|

SU1522196A1 |

| Устройство для вычисления тригонометрических функций | 1981 |

|

SU1003079A1 |

| Устройство для выполнения преобразования координат | 1987 |

|

SU1462299A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Арифметическое устройство | 1978 |

|

SU746508A1 |

| Устройство для реализации безызбыточного алгоритма быстрого преобразования Фурье | 1981 |

|

SU1056206A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

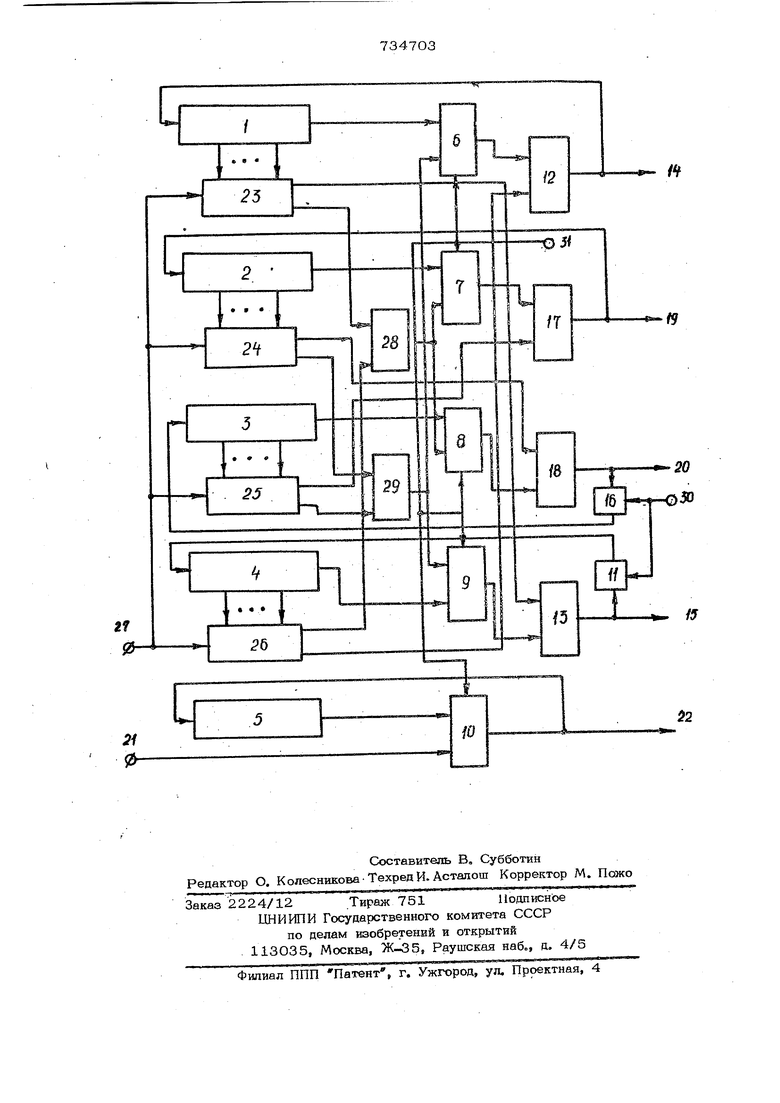

Изобретение относится к вычиспитепьной технике и предназначено для построения на его основе специализированных ЦВМ. Известны арифметические устро ;тва для обработки координат векторов, предназначенных для решения задач, содержащих большое количество координатных пре образований. Эти устройства вьшолняют преобразование координат вектора при повороте осей прямоугольных координат ( X ) на угол , то есть й-4. гпес-1 матрица поворота когде.с. -I ..j cosd L j ординат. Они содержат сдвигающие регистры, коммутирующие блоки, сумматоры-вычитатели и позволяют выполнять преобразование (1) на порядок быстрее, чем традиционные арифметические устройства. Преобразование (1) можно считать преобразованием компонент одновалентного тензора (каким является вектор) на плоскости СЦ. На практике часто требуется проводить преобразование компонент двухвалентного тензора, которое имеет вид ,(2) С т транспортированная матрица вращения;Л АчЛлЛ матрица компонент тензора. Преобразование (2) может быть выполнено с помощью указанных устро1$ств за четыре операции поворота, причем после первой операции будем иметь после второй после третьей и четвертой И-Р ЦОднако такое время реализации не всег допустимо на практике. Наиболее близким по технической реа лизации является арифметическое устрой ство, работающее по алгоритму Волдера , , + -, . позволяющее вычислять координаты и-ш у Q arctg В предыдущих выражениях X значения координат и угла радии; - оператор направления вращ ния, равный для соотношения (4) .,, а для соотношения (5) e..-eign{-Yi)( М угловая скорсхзть, равна di CtpZ k - - коэффициент общего удлинения вектора, равный произведению коэффициенто удлинения на каждой итерации п 1Г м+г Ь{ Х, Y , 00-с.- исходные данные; 1- номер итерадии ( 1 1,2 ..., и). Арифметическое устройство, реализую щее алгоритм {3), состоит из двух сдви гающих регистров, накапливающих значения координат, регистра угла и трех сум ма торов-вычита те лей, причем выходы ре гистров координат соединены с первыми входами двух сумматоров-вычитателей, вторые входы которых соединены через коммутирующие блоки со сдвиговыми вы ходами противоположных регистров; вых регистра угла соединен с первым входом третьего сумматора-вычитателя, на второ вход которого подаются .значения угловы постоянных, выходы сумматоров-вычитателей соединены со входами соответству ющих регистров l. 34 Наиболее близким к предлагаемому ляется устройство для преобразования компонент тензора, содержащее три регистра сдвига, два коммутирующих блока, три сумматора-вычитателя, причем выходы первого и второго регистров сдвига соединень с соответствующими, входами коммутирующих блоков, управляющие входы которых подсоед1шены к первом - входу устройства, вход старшего разряда третьего регистра соединен с выходом третьего сумматора-вычитателя и первым .выходом устройства, выходы младших раз- рядов регистров сдвига подключе 1ы к первым входам сумматоров-вычитателей, второй вход третьего сумматора-вычитателя соединен с вторым входом устройства, входы первого и второго регистров сдвига подсоединены ко второму и третьему выходам устройства соответственно 2}. Недостатком таких устройств является большое время реализации пробразования равное времени выполнения четырех операций поворота вектора. Цель изобретения - повышение быстродействия устройства при вьшолнении преобразования компонент тензора. Указанная цель достигается тем, что устройство содержит четвертый и пятый регистры сдвига, третий и четвертый коммутирующие блоки, четвертый и пятый сумматоры-вычитатели, три сумматора три вычитателя и два элемента запрета, пр1гчем выходы четвертого и пятого регистров сдвига соединены соответственно со входами третьего и четвертого коммутирующих блоков, управляющие входы которых подключены к первому входу устройства, первые выходы первого и четвертого коммутирующих блоков подключены ко входам первого вычитателя, первые выходы второго и третьего коммутирующих блоков соединены с входами первого сумматора; выходы четвертого и пятого регистров сдвига подключены соответственно к первым входам четвертого и пятого сумматоров-вычитателей, выходы первого вычитателя и первого сумматора соединены со вторыми входами второго, четвертого и первого, пятого сумматоров-вычитателей соответственно, входы второго сумматора подключены к выходу первого сумматора-вычитателя и второкгу выходу четвертого коммутирующего блока, а выход - к второму выходу устройства, входы второго вычитателя соединены соответственно с выходом второго сумматора-вычитателя и вторым выходом третьего коммутирующего блока, а выход - с третьт. выходом устройства, входы третьего вы читателя подключены соответственно к выходу четвертого сумматора-вычитателя и второму выходу второго кoм Jyтиpyющeго блока, а выход - к четвертому выходу устройства и входу первого элемента запрета, нходы третьего сумматора соедине ны со вторым выходом первого коммутирующего блока и выходом пятого сумматора-вычитателя, а выход - с пятым выходом устройства и входом второго элемента запрета, управляющие входы элементов запре,та подключены к третьему входу устройства, а выходы - ко входам четвертого и пятого регистров сдвига соответственно, управляющие входы всех сумматоров-вычитателей подключены к четвертому входу устройства. Преобразование компонент тензора вы- полняется по алгоритму Л. VC. г .Vi (ar.i) Лп( eu4-V -. (iм)(iЧ,(,V2 . A„„..,.,-l(A,+ ,)2 22(iH).2 V«r Mil ( где значения , определяются по формуле (6), а-©р-оС-Реализация алгоритма (8) вьшолняется за то же время, что и алгоритм (З), причем результирующие компоненты получаются в масштабе V.n() задании начальных значений А.. Y( A и сохрайении равенства А,,. А „-0 - cohst устройство реализует алгоритм (3). На чертеже показана блок-схема усрройства. Схема устройства содержит пять регистров 1-5 сдвига, три сумматора 12, 13, 29, три вычитателя 17, 18, 28, пять сумматоров-вычитателей 6-10, четыре коммутирующих блока. 23-26, причем выходы младших разрядов регистров 1-5 сдвига соединены с первыми входам сумматоров-вычитателей 6-1О соответст венно, входы старших разрядов регистра 1 непосредственно, а регистра 4 через элемент 11 НЕ соединены с выходами сумматоров 12, 13 и выходами устройст ва 14 (А , 15 (Ao2. соответственно, входы регистра 2 непосредственно, а регистра 3 через элемент 16 НЕ соединены с выходами вычитателей 17, 18 и выходами устройства 19 (А.,, 2О ()соответственноэ выход регистра 5 соединен со входом сумматора-Бычитатэля 1О, второй вход которого является входом 21 устройства, (узловой постоянной Ч ), а выход соединен со входом регистра 5 и является выходом 22 (-&) устройства, выходы всех разрядов регистров 1-4 соединены соответственно со входами коммутируюштсх блоков 23-26, управляющие входы которых соединены со входом 27 (управляющего сигнала) устройства, пер- вые выходы коммутирующих блоков 23, 26 подключены ко входам вычитателя 28, а блоков 24, 25 ко входам сумматора 29, выход вычитателя 28 подключен ко вторым входам сумматоров-вычитателей 7 и 8, а выход сумматора 29 - ко вторым входам сумматоров-вычятателей 6 и 6,первые входы сумматоров 12 и 13 Соединены с выходами сумматоров-вычитателей 6 и 9, вторые входы со вторыми выходами блоков 26 и 23 соответственно, первые входы вычитателей 17, 18 соединены с выходами сумматоров-вычитателей 7,8;а вторые-со вторыми выходами блоков 25 и 24 соответственно, управляк щие входы элементов 11, 16 НЕ соединены с входом 30 устройства, (запрета), а управляющие входы сумматоров-вычитателей 6-1О с входом 31 ( ) устройства. При вычислении соотнощений (2) предлагаемое устройство работает по алгоритму (8), а при вычислении соотношений 4), (5) - по алгоритму (З). В первом случае устройство работает следующим образом. Операнды , А,-, 22.-( хранятся в регистрах 1-5, на вход 30 сигнал запрета не подается, по команде i-й итерации из устройства управления по входу 27 все коммутирующие блоки соединяют свои первые выходы с выходами соответствующих разрядов регистров таким образом, что на входы блоков 28, 29 поступают операнды, умноженные на величину 2 а свои вторые выходы таким образом, чтобы на входы блоков 12, 13, 17, 18 поступали операнды, умноженные на величину . С выходов младших разрядов регистров 1-5 операнды поступают на входы сумматоров-вычитателей 6-1О, где в соответствии с сигналом поступающим по входу 31 из устройства управления,-суммируются (вычитаются) -с величинами ( ) 773470 {A22i )-(, которые поступают с входов блоков 28, 29 и из запоминающего устройства по входу 21 соответственно, С Выходов сумматоров-вычитатепей 6-9 результаты поступают на входы сумматоров 12, 13 и вычитателей 17, 18, где суммируются (вычитаются) с соответствуюшими операндами, умноженными на 2 Результаты операций , + o 2-1(1 н)) ® регистры 10 1-5 соответственно, причем величина подается по выходу 22 в устройство уп- равления, где используются для выработки сигнала - .Процесс повторяется до выполнения заданного количества итераций. 15 В конце операции результаты выводятся из устройства по линиям 14, 19, 2Ои15 При вычислении соотношений (4) рабо.та устройства аналогична описанному процессу с той разницей, что в регистрй 14 заносятся значения X 9 О соответственно, а на вход ЗО поступает .сигнал запрета. В случае вычисления соотношений (5) функция Получается как функция знака - Y сним)земого в уст ройство управления с выхода 19, Эффективность предлагаемого изобретения заключается в сокращении времени преобразования компонент тензора в 4 раза при увеличении объёма оборудования менее чем в 2 раза. Формула изобретения Устройство для преобразования компонент тензора, содержащее три регистра сдвига, два коммутирующие блока, три сумматора-вычитателя, причем выходы пер вого и второго регистров сдвига соединены со входами соответствующих коммутирующих блоков, управляющие входы которых подсоединены к первому входу устрой ства, вход старшего разряда третьего регистра соединен с выходом третьего суМ матора-вычитателя и первым выходом устройства, выходы младших разрядов регистров сдвига подключены к первым входам соответствующих сумматоров-вычитателей, второй вход третьего сумматора-вьпитате ля соединен со вторым входом устройства входы первого и второго регистров сдвига соединены со вторым и третьим выходами устройства соответственно, отличающееся тем, что, с целью по- 3 вышения быстродействия, .устройство содержит четвертый и пятый регистры сдвига, третий и четвертый коммутирующие блоки, четвертый и пятый сумматоры-вычитатели, три сумматора, три вычитателя и Два элемента запрета, причем выходы четвертого и пятого регистров сдвига соединены соответственно со входами третьего и четвертого коммутирующих блоков, управляющие входы которых подключены к первому входу устройства, первые выходы первого и четвертого коммутирующих бло- ков подключены ко входам первого вычитателя, первые выходы второго и третьего коммутирующих блоков соединены с входами первого сумматора, выходы четвертого и пятого регистров сдвига подключены соответственно к первым входам четвертого и пятого сумматоров-вычитателей, выходы первого вычитателя и первого сумматора соед1шены со вторыми входами второго, четвертого и первого, пятого сумматоров-вычитателей соответственно, входы второго сумматора подключены к выходу первого сумматора-вычитателя и второму вькоду четвертого коммутирую - щего блока, а выход - к второму выходу устройства, входы второго вычитателя соединены соответственно с выходом второго сумматора-вычитателя и вторым выходом третьего коммутирующего блока, а выход - с третьим выходом устройства, входы третьего вычитателя подключены соответственно к выходу четвертого сум-. матора-вычитателя и второму выходу второго коммутирующего блока, а выход - к четвертому выходу устройства и входу первого элемента запрета, входы третьего сумматора соединены со вторым выходом первого коммутирующего блока и выходом пятого сумматора-вычитателя, а выход - с пятым выходом устройства и входом второго элемента запрета, управляющие входы элементов запрета подключены к третьему входу устройства, а выходы ко входам четвертого и пятого регистров сдвига соответственно, управляющие входы сумматоров-вычитателей подключены к четвертому входу устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 445О42, кл. G Об F 15/2О, 1974. 2.Электроника, 1966, № 18, ;. ЗО-38 (прототип).

Авторы

Даты

1980-05-15—Публикация

1978-01-23—Подача