фигЛ

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении специализированных ЭВМ для решения задач ста билизации платформ, навигации и др.

Цель изобретения - упрощение при вьтолнении операции вращения вектора вокруг координатных осей.

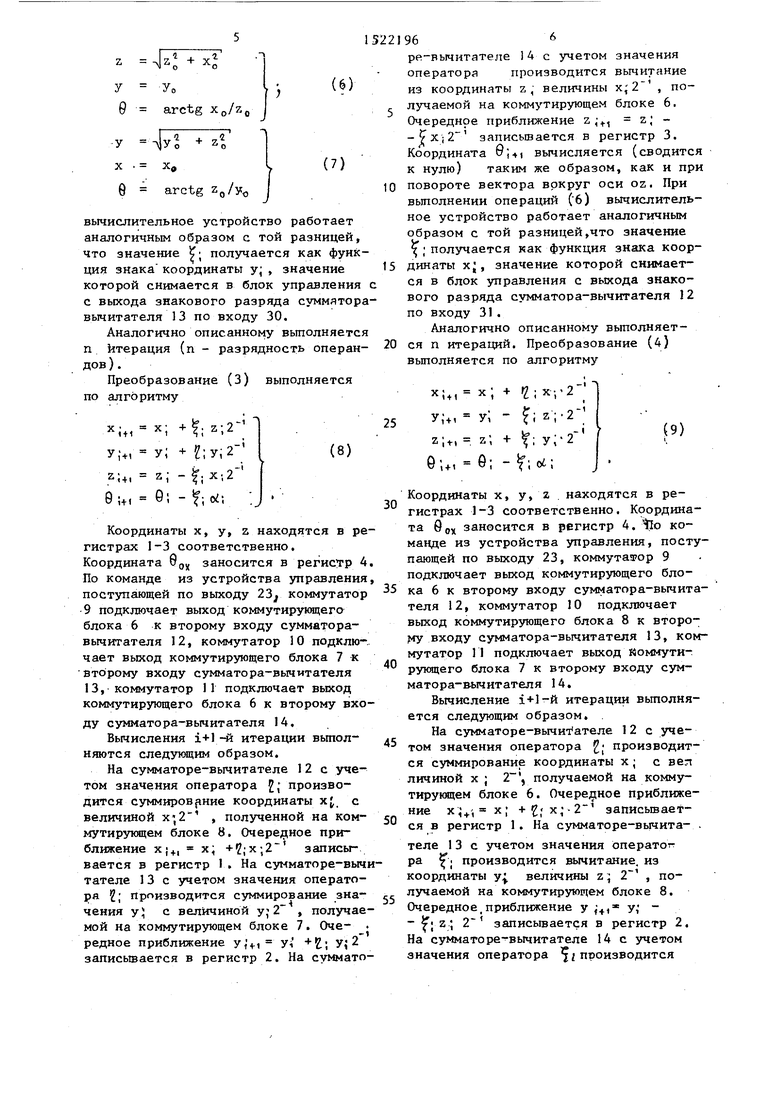

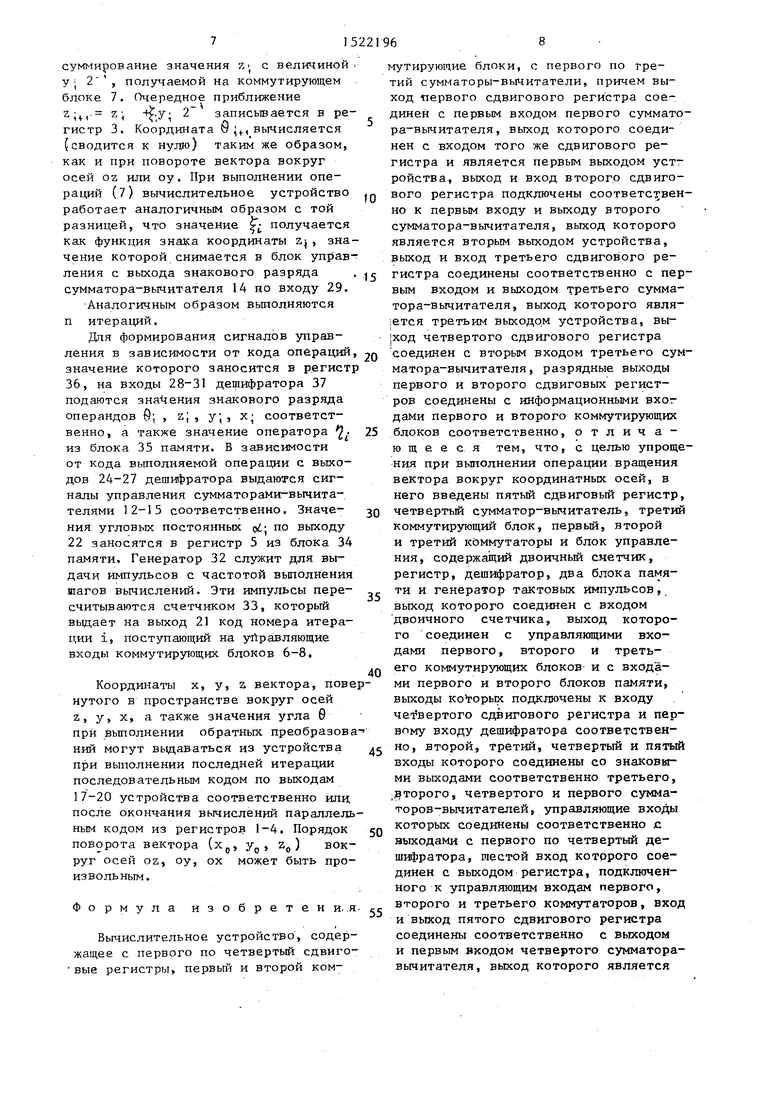

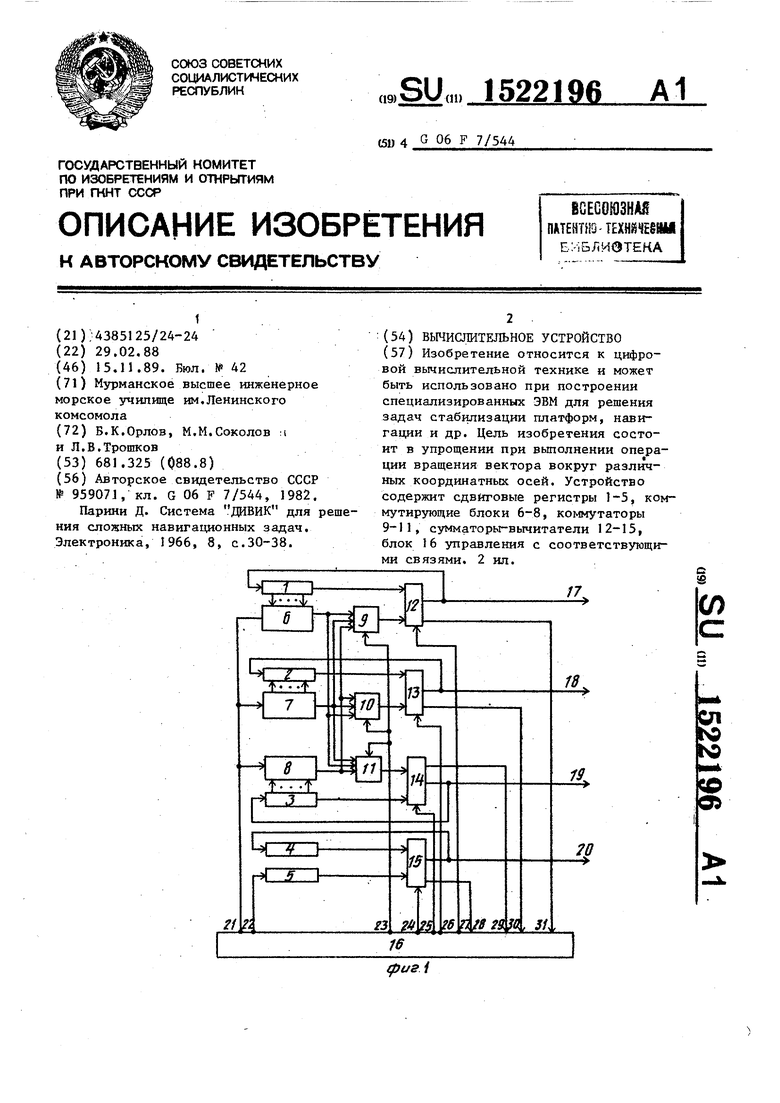

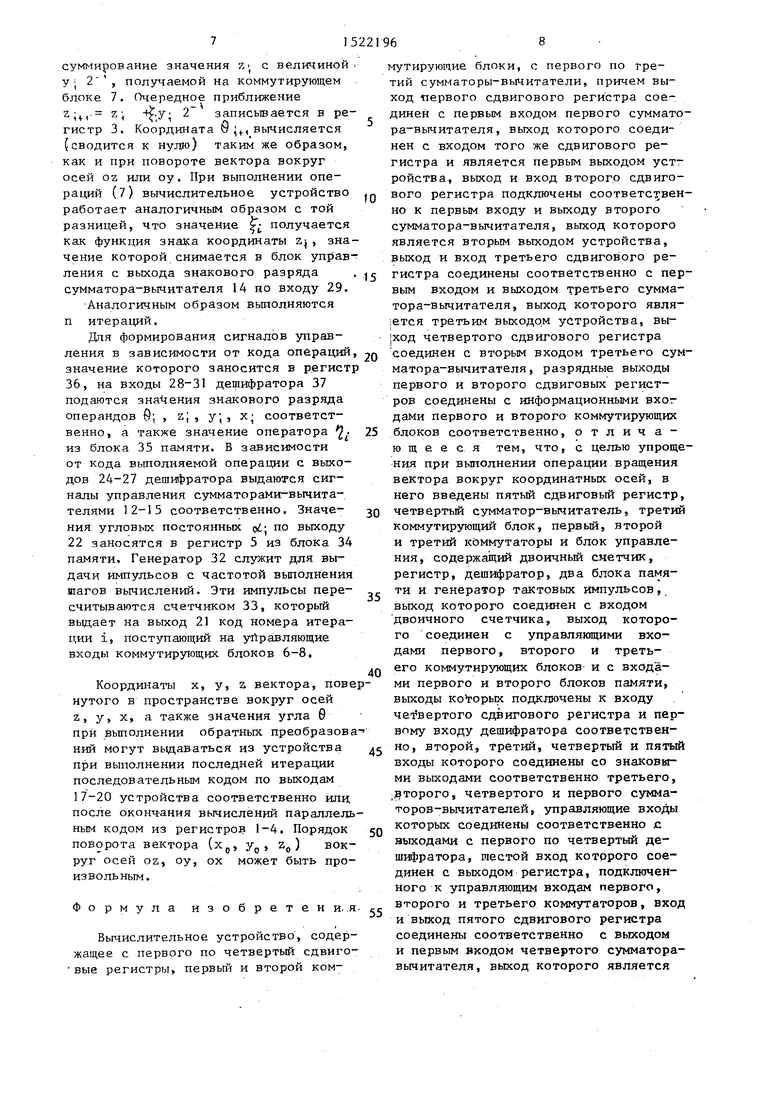

На фиг.1 представлена структурная схема вычислительного устройства; на фиг.2 - структурная схема блока управления.

Устройство.(фиг.1) содержит с первого по пятый сдвиговые регистры 1-5, коммутирующие блоки 6-8, коммутаторы 9-11, сумматоры-вычитатели 12-15, блок 16 управления, выходы 17-20 устройства, выходы 21-27 блока управления, входы 28-31 блока уп- равления.

БЛОК управления (фиг.2) содержит генератор 32 тактовых импульсов двоичный счетчик 33, первый блок 34 памяти, второй блок 35 памяти, per. гистр 36 и дешифратор 37.

Работу устройства можно описать следуюп(им итерационным алгоритмом

-;-Г;п2-,.

у; + ; х,

J

О)

где - signS i - оператор направления вращения; (2 V const - оператор растяжения вектора.

Устройство работает следующим образом.

Для пространственного поворота вектора (хоэУ,,,,) вьшолняются преобразования (2) - (4) в последовательности опе эаций вращения вектора

вокруг оси OZ

sin 0 О cos 9 О О 1

о 2)50

40

вокруг оси у

1 О о о COS0 - sin 9 О sin 6 cos 9

(4)

5 0

5

0

5

в различной последовательности. Координаты х. Уд, ZQ угла поворота

9

значения угловой постоянной / нахо- дятс.я в регистрах 1-5 соответственно.

По команде из устройства управления, поступающей по выходу 23, коммутатор 9 подключает выход коммутатора блока 7 ко второму входу сумматора- вьгчитателя 12, коммутатор 10 подключает выход коммутирукяцего блока 6 к второму входу сумматора-вычитателя 13, коммутатор М подключает выход коммутирующего блока 8 к входу сумматора- выч итателя 14.

Вычисления в i+1-й итерации выполняются следующим образом.

На сумматоре-вычитателе I2 с учетом значения оператора производится вычитание из координаты х величины

у;

получаемой на коммутирующем блоке 7. Очередное приближение 141 x, -ryi2 записьшается в регистр I. На сумматоре-вычитателе 13 с учетом значения оператора | производится суммирование значения у- с величиной х;2 , получаемой на коммутирующем блоке 6. Очередное приближение у 4-1 записывается .в регистр 2. На сумматоре-вычитателе 14 с учетом значения оператора ; производится суммирование значения

с величиной г;

2- ,

получаемой

на коммутирующем блоке 8. Очередное приближение z, +t zj записывается в регистр 3. На сумматоре-вычитателе 15 производится вычитание с учетом знака j из координаты v;. хранимой в регистре 4, величины р{{ , поступающей из регистра 5. Очередное приближение 9 ,, 0; - ; записывается в регистр 4. Значения оператора . с выхода знакового разряда сумматора-вычитателя 15 по входу-28 : поступают в устройство управления на дешифратор 37 кода операции. При выполнении операции обратного преобразования

X

ч

у

(5)

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Устройство для вычисления модуля трехмерного вектора | 1989 |

|

SU1672442A1 |

| Вычислительное устройство | 1981 |

|

SU1136147A1 |

| Вычислительное устройство | 1983 |

|

SU1164696A1 |

| Устройство для определения модуля трехмерного вектора | 1983 |

|

SU1142830A1 |

| Вычислительное устройство | 1981 |

|

SU959071A1 |

| Арифметическое устройство | 1975 |

|

SU547765A1 |

| Арифметическое устройство | 1978 |

|

SU746508A1 |

| Арифметическое устройство | 1982 |

|

SU1022152A1 |

| Арифметическое устройство | 1979 |

|

SU796844A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении специализированных ЭВМ для решения задач стабилизации платформ, навигации и др. Цель изобретения состоит в упрощении при выполнении операции вращения вектора вокруг различных координатных осей. Устройство содержит сдвиговые регистры 1-5, коммутирующие блоки 6-8, коммутаторы 9-11, сумматоры-вычитатели 12-15, блок управления 16 с соответствующими связями. 2 ил.

вокруг оси X

(3)

Z,

б arctg УО/ХО

4 + xf

у Уо

9 arctg Xp/z,

(6)

Ч

у; -

Хв

arctg Z /у

(7)

вычислительное устройство работает аналогичным образом с той разницей, что значение ; получается как функция знака координаты у; , значение которой снимается в блок управления с с выхода знакового разряда суммятора вычитателя 13 по входу 30.

Аналогично описанному вьшолняется п итерация (п - разрядность операн- дов).

Преобразование (3) выполняется по алгоритму

x;,, x;

y,4, y; -

z;;+, z; - j x.,2

9;,, e; oi;

Координаты X, у, z находятся в регистрах 1-3 соответственно. Координата QQ,, заносится в регистр 4 По команде из устройства управления поступающей по выходу 23 коммутатор 9 подключает выход коммутирукицега блока 6 к второму входу сумматора- вычитателя 12, коммутатор 10 подключает выход коммутирующего блока 7 к второму входу сумматора-вычитателя 13, коммутатор 11 подключает выход коммутирующего блока 6 к второму входу сумматора-вычитателя 14.

Вычисления i+1 -si итерации вьтол- няются следуняцим образом.

На сумматоре-вычитателе 12 с учетом значения оператора ; производится суммиров{1ние координаты xj с величиной , полученной на коммутирующем блоке 8. Очередное приближение xj+i х; , записывается в регистр 1, На сумматоре-вычитателе 13 с учетом значения оператора ; Производится суммирование зна- чения у с величиной у;2 , получаемой на коммутирующем блоке 7. Оче- . редное приближение y,Vi Ч, У записьгоается в регистр 2. На суммато

10

15с

0

J96

ре-вычитателе 14 с учетом значения оператора производится вычитание нз координаты z, величины х;2 , получаемой на коммутирующем блоке 6, Очередное приближение z ;, z; - - Х|2 записьюается в регистр 3. Координата вычисляется (сводится к нулю) таким же образом, как и при повороте вектора вокруг оси oz. При выполнении операций ( 6) вычислительное устройство работает аналогичным образом с той разницей,что значение .получается как функция знака координаты X , значение которой снимается в блок управления с выхода знакового разряда сумматора-вычитателя 12 по входу 31.

Аналогично описанному вьтолняет- ся п итераций. Преобразование (4) выполняется по алгоритму

( + 1

х;-f 2;х-,-2у;+, у;- ;

z;, z;+ ; yi 2

Ou, G;-. oil

(9)

0

5

0

с

5

0

Координаты X, у, z находятся в регистрах 1-3 соответственно. Координата 9 ох заносится в регистр 4. tlo команде из устройства управления, поступающей по выходу 23, коммутатор 9 подключает выход коммутирующего блока 6 к второму входу сумматора-вычитателя 12, коммутатор 10 подключает выход коммутирзпощего блока 8 к второ- ку входу сумматора-вычитателя 13, коммутатор 11 подключает выход Коммути- рукяцего блока 7 к второму входу сумматора-вычитателя 14.

Вычисление 1-ь1-й итерации вьтолня- ется следующим образом, .

На сумматоре-вычит ателе 12 с учетом значения оператора 2 производится суммирование координаты х; с вел личиной X ; , получаемой на коммутирующем блоке 6. Очередное приближение , х; + ;х;-2 записьшает- ся в регистр 1. На сумматоре-вычита- теле 13 с учетом значения оператотт ра . производится вычитание, из координаты у| величины z:; , получаемой на коммутирующем блоке 8. Очередное,приближение у , У, - ; z; записьшается в регистр 2. На сумматоре-вычитателе 14 с учетом значения оператора j производится

суммирование значения х с величиной У 2, полу аемой на коммутирующем блоке 7. Очередное приближение Ur 2 ,У -, 2 записьюается в регистр 3. Координата 9 , вычисляется (сводится к нулю) таким же образом, как и при повороте вектора вокруг осей OZ или су. При выполнении операций (7) вычислительное устройство работает аналогичным образом с той разницей, что значение у получается как функция знака координаты Zj, значение которой снимается в блок управления с выхода знакового разряда

сумматора-вычитателя 14 по входу 29.

Аналогичным образом вьшолняются п итераций.

Дпя формирования сигналов управления в зависимости от кода операций значение которого заносится в регистр 36, на входы 28-31 дешифратора 37 подаются значения знакового разряда операндов 0; , zj , у;, х; соответственно, а также значение оператора - из блока 35 памяти. В зависимости от кода выполняемой операции с выходов 24-27 дешифратора выдаются сигналы управления сумматорами-вычита- телями 12-15 соответственно. Знача- ния угловых постоянных oi- по выходу 22 заносятся в регистр 5 из блока 34 памяти. Генератор 32 служит для выдачи импульсов с частотой выполнения иагов вычислений. Эти импульсы пересчитываются счетчиком 33, который выдает на выход 21 код номера итерации 1, поступающий на управляющие входы коммутирующих блоков 6-8,

Координаты X, у, z вектора, повенутого в пространстве вокруг осей Z, у, X, а также значения угла 0 при выполнении обратных преобразова НИИ могут выдаваться из устройства при выполнении последней итерации последовательным кодом по выходам 17-20 устройства соответственно или; после окончания вьиислений параллельным кодом из регистров 1-4. Порядок поворота вектора (х, у, z) вокруг осей OZ, оу, ох может быть произвольным.

Формула изобретен и. .я

Вычислительное устройство, содержащее с первого по четвертый сдвиго- вые регистры, первый и второй коммутирующие блоки, с первого по третий сумматоры-вычитатели, причем выход первого сдвигового регистра соединен с первым входом первого сумматора-вычитателя, выход которого соединен с входом того же сдвигового регистра и является первым выходом устг ройства, выход и вход второго сдвигового регистра подключены соответс вен но к первым входу и выходу второго сумматора-вычитателя, выход которого является вторым выходом устройства, выход и вход третьего сдвигового регистра соединены соответственно с первым входом и выходом третьего сумматора-вычитателя, выход которого явля- ;ется третьим выходом устройства, вы- |ход четвертого сдвигового регистра соединен с вторым входом третьего сумматора-вычитателя, разрядные выходы первого и второго сдвиговых регистров соединены с информационными вхог дани первого и второго коммутирующих блоков соответственно, о т л и ч а - ю щ е е с я тем, что, с целью упрощения при выполнении операций вращения вектора вокруг координатных осей, в него введены пятый сдвиговый регистр четвертьй сумматор-вычитатель, третий коммутирующий блок, первый, второй и третий кЬммутаторы и блок управления, содержащий двоичный снетчик, регистр, дешифратор, два блока памяти и генератор тактовых импульсов, выход которого соединен с входом двоичного счетчика, выход которого соединен с управляющими входами первого, второго и третьего коммутирующих блоков и с входами первого и второго блоков памяти, выходы которых подключены к входу четвертого сдвигового регистра и первому входу дешифратора соответственно, второй, третий, четвертый и пятый входы которого соединены со знаковм- ми выходами соответственно третьего, ,второго, четвертого и первого сумма- то ров-вычитат ел ей, управляющие входы которых соединены соответственно с вькодами с первого по четвертый дешифратора, шестой вход котррого соединен с выходом регистра, подключенного к управляющим входам первого, второго и третьего коммутаторов, вход и выход пятого сдвигового регистра соединены соответственно с выходом и первым входом четвертого сумматора- вычитателя, выход которого является

9J5221

четвертым выходом устройства, разрядные выходы пятого сдвигового регистра соединены с информационными входами третьего коммутирующего блока, выход первого коммутирующего блока соединен с первыми информационными входами первого, второго и третьег го коммутаторов, вторые и третьи ий96 ° .

формационные входы которых подключены к одноименным выходам соответственно второго и третьего коммутирующих блоков, выходы первого, второго и третьего коммутаторов соединены с вторыми входами соответственно первого, четвертого и второго сумматоров-вычк- тателей.

(риз.2

| Автомат для завальцовки верхнего края бумажных патронов | 1951 |

|

SU95907A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Парини Д | |||

| Система ДИВИК для решения сложных навигационных задач | |||

| Электроника, 1966, 8, с.30-38. | |||

Авторы

Даты

1989-11-15—Публикация

1988-02-29—Подача