(54) ЦИФРОВОЙ ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Параллельный цифровой интегратор с пла-ВАющЕй зАпяТОй | 1977 |

|

SU828199A1 |

| Масштабный интегратор | 1976 |

|

SU746601A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1977 |

|

SU703840A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1974 |

|

SU518781A1 |

| Цифровой интегратор для однородных цифровых интегрирующих структур (оцис) с плавающей запятой | 1973 |

|

SU510727A1 |

| Цифровой интегратор с плавающей запятой | 1975 |

|

SU590774A2 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

;-:. ; , . ,

Предлагаемое изобретение относится к области вычислительной техники, а именно, к цифровым интегрируюшнм ма шинам и может быть использовано в oRHoppaHbix вычислительных системах.

Известны цифровые интеграторы для бинарной и тернарной систем к6аирования|11 , каждый из которых состоит иэсумматен ров подынтегральной функции и остатка, регистров поцинтегральной функции и остатка, реверсивного сче-т ика прирдадений, тригзгера начального им17льса, пр© обризоватепя коаа, схемы пуска и :останова. За кажаь1й шаг интегрирования счетчик приращений производит подсчет импульсов. Сумма импульсов прецстав ляет собой приращение подинтегральнрй функции.

к недостаткам известньтх устройств : следует отнести то, что в процессе программирования нужно вводить начальные данные с меньшим масштабом, что снижает точность вычислений.

Из известных BHtei paTopcm наиболее близким по техш еской сртиости явяя6ТСЯ цифрсдаой интегратор 2j, сро жащий суммат подынтегральной функций, сумматор остатка, умнояштоп, которого соединен с &ходсяи1сумматора остатка, блок выселения прире щений, вход которсяго среоинен с выхо awn сумматора остатка, а ОЕОЦ является информационным выхоя(«( устровсть. ва. ; . . .

HedbCTaTKWvi известйм о устройства является то, что прихогщтся производить предварителыюе. масштабирование неременных, что представляет собой трудоёмкую задачу и в Конечном счете понв: жает быстродействие.

Целью изобретения является повышение быстродействия.

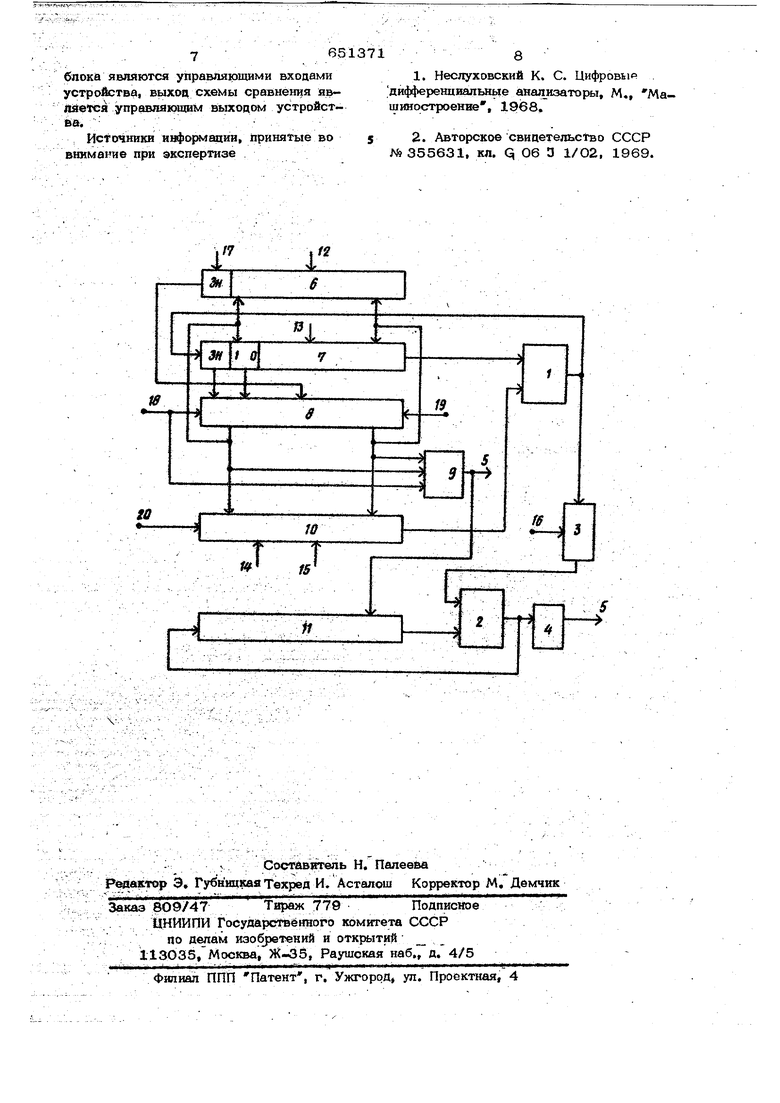

Поставленная цель достигается тем, что в интегратор введены счетчик, регистр подынтегральной функции, блок нррмализац ш мантиссы, схема сравнения, масштабный блок, pejpHCTp остатка,при65ЧОМ ВЫХОД сумматора подынтегральной (jyiiKHiTii соешгнен с первым бхоаом умн жителя и с первым входом регистра поц чнтогральньй функции, выхоц счетчика подключен к ьгрво:,;1у входу блока нормализации мантиссы, выход младшего разряда регистра подинтегральной функции подключен к первому входу сумматора подынтегральной функции, а 1вь1х6ды старшего и знакового разрядов - соответственно ко второму и т{Ьетьему входам блока нормализации мантиссы, первый йыход которого пошспючен к первому входу масштабного блока, ко входу старшего разряда регистра подынтегральной функции, а первым входам счетчика и схемы сравнения, а второй выход - ко входу младшего разряда регистра подынтегральной фушц.ии, ко вторым входам счетчика, схемы сравнения и масштабного блока, выход которого подключен ко второму входу сумматора подинтегральной функций, 6ЫХОД схемы сравнения соединен с первым входом региЬтра остатка, второй вход которого сое- дияен с выходом сумматора остатка а выхой - со втЪрым взводом ёумШтбра остатка, третий вХод счётчика, второй вход регистра подынтегральной фу нкции, Третий и четвертый входы масштабного блока, второй вход умножителя являются информационными входами устройства четвертый; вход счётчика, четвертый и пятый входы блока нормализации мантиссы, третий вход схемы сравнения и пятый вход масштабного блока являют-ся управлякоцими входами устройства, выход схШЬ СрШШШя являетсяуправляющим выхбдом устройства. : -: На чертеже предстаншена блок-схема HHTerpavopa, Интегратор содержит сумма тор 1 подинтегральной функции, сумматор 2 остатка, умножитель 3, блок 4 выделения приращений, информационный выход 5 устройства, счетчик 6, регистр 7 подынтегральной функции, блок 8 нормалясзадий 1иантиссы, схема 9 сравнения, масштабный блок 10, регистр сютатка 11, информационные входы 12, 13, 14, 15, 16, управляющие входы 17/ 18, 19, 20.:-Устройство работает следующим о разом. .,.,,:-,-,.,„,..,„,-.., ... :. , -:-v,..--.-,., -- Процесс решения разбивается на два этапа.. Прецв13рй тельно вычисляв тся jpasHocTb между порядками подынтегральной функции иее приращениями. В счетчик 6 за 4 письшаются порядки начальньцс значений подннтегральных функций, причем знаки порядков включают блок 8. По положительному знаку блоком 8 вырабатываются сигналы нормализации влево. При этом в счетчике 6 вычитаются импульсы до тех пор, пока не запишутся нулевые коды. По отри11атёльному знаку блоком 8 вырабатываются сигналы нормализации вправо, а в счетчике 6 суммируются импульсы до записи в них нулевого кода. При этом схемой 9 вырабатьшаютёй ёигналы изменения веса. По атим сигналам и сигналам нормализации в масштабном блоке 10 (в который предварительно записываются по входу 14 начальные масштабные импульсы одного веса) вырабатывак)ТСя масштабные йМпульсы с соответствук щими весами и знаками масштабов. По окончании выравнивания порядков по канйпшл связи прекращается передача сигналов. При этом в масштабном блоке 10 зафиксируется разность порядков начальных значений. В елейующем этапе вводят начальное значение мантиссы подынтегральной функции в регистр 7, а ее порядок в счетчик 6. В блоке 8 анализируются старшие (два из них знаковые) разряды мантиссы подынтегральной, функции и на основании анализа вырабатываются сигналы возможности нормализации мантиссы подынтегральной функции влево и необходимости нормализации функции вправо. Сигналы возможн1х;ти нормализации влево вырабатываются блоком 8, если в результате анализа окажется, что в старших разрядах функции все нули (единицы), и если поступит на вход i8 сигнал увеличения веса приращения переменной интегрирования, а при отсутствии последнего сигнал нормализации влево не вырабатывается.. По сйгналу нормализации влево схемой 9 ёапрёшается вйдаЧа сигнала увеличения веса выходного приращения, Ив регистре 7 осуществлйется сдвиг кода подынтегральной функции влево на один . Такое действие равносильно увеличению скорости выдачи приращений, поскольку сдвиг кода функции влево приВбцйТк увеличению заполнения регистра 7. В управляемрм масштабном блоке 10 по сигналу нормализгщии функ11ии влево вырабатывается приращение подынтегральной функции с увеличенным весом , а если при этом сто поступит 5 (на вход 20) сигнал увеличения веса п ращения, то вес прирашсн.ия подинтеррал нрй функции увеличится в 2 раза, Сигнал нормализации нкции вправо вырабатывается блоком 8i если в результате анализа старших разрядов подынтегральной функции окажется, что знеи ковые разряш 1 функции не совпадают. При этом по сигналу нормализации вправо в регистре 7 происходит сдвиг кода подынтегральной функции вправо на один рйзряд и схемой 9 выдается сигнал увеличения веса выходного при- ращиния. А если на входы схемы 9 поступает одновременно сигнал нормали зации вправо и сигнал увеличения веса приращения переменной интегрирова1тя, то схемой 9 выдается один сигнал увеличения веса выходного приращения, а второй - запоминается этой рхёмой. Последний выдается, когда не поступает (на вход 18) сигнал увеличения веса приращения переменной интегрирования и отсутствует сигнал нормализации вправо. Каждый раз при выдаче сигнала увеличения веса выходного приращения в регистре 11 сдвигается код остатка влево на один разряд, По сигналу нормализации вправо в управляемом масштабном блоке 10 вырабатывается приращение подинтегральной функции с уменьшенным весом 2 , если при нормализации вправЬ на вхоа. 20 блока 1О одновременно поступает сигнал увеличения веса приращения, то в масщтабном блоке 10 вырабатывается приращение подынтегральной функции без изменения веса. Причем, если На вход масштабного блока 10 поступает только один сигнал увеличения веса приращения, то в масщтабном блоке 10 вырабатывается приращение подын- теграл1.ной функции с увеличенным ве-, .. Достой 1и;тво изобретения состоит в том, что отсутствует необходимость в предварительном сложном , масщтаоирова нни переменнья. При широком диапазон изменения переменных достигается оптимальное соотнош€ нне между скорость н точностью решения. Последнее достигается, если весь интервал решения разбить на несколько участков, На каж- до.{ пз которых тлеется различный масштаб, а на границе участков осуществляется автоматическое изменение масштабов. Поэтому отсутствие необход ысх:ти в преоварительном масштабиро1вании переменных позволяет существенно облегчить программирование, а также повысить быстродействие, так как при этом рещение производится на всем интервале с максимально возможным заполнением регистров. Формула изобретения Цифровой интегратор, содержащий сумматор подынтегральной функции, сумматйр остатка, умножитель, выход которого соединен с первым входом сумматора остатка, блок выделения приращений , вход которого соединен с выходом сумматора остатка, а выход является информационным выходом устройства, отличающий с я тем, что, с целью повыщения быстродействия в интегратор введень счетчик, регистр поцинтегральной функции, блок нормализации мантиссы, схема сравнения, масштабный блок, регистр остатка, причем выход .сумматора подынтегральной 4 нкции соединен с первым входом умножителя и с первым входом регистра подынтегральной функции, выход счетчика подключен к первому входу блока нормализации мантиссы, выход мла Щ1его разряда регистр подынтегральной-, функции подклкяен к первому входу сумматора подынтегральной функции, а выходы старшего и знакового разрядов соответственно ко второму .и третьему входам блока нормализации м энтиссы, первый выход которого подключен к первому входу масштабного блока, ко . входу старЩего разряда регистра подьштегральной функции, к первым входам счетчика и скецы сравнения, а второй выход - ко входу младшего разряда регистра подинтегральной функции, ко вторым входам счетчика, схемы сравнения и масштабного блока, выход которого подключён ко второму входу сумматора подынтегральной функции, выход схемьг сравнеш1Я соединен с первым входом регистра остатка, второй вход Ko-i-oporo соединен с выходом сумматора остатка, а выход - со вторым входом сумматора остатка, третий вход счетчика, второй вход регистра подынтегральной функции, третий и четвертый вХоды масштабного блока, второй вход умножителя являются информационными входами устройства, четвертый вход счетчика, четвертый и пятый входы блока нормализации мантиссы, третий вход схемы сравнения и пятый вход масштабного 65 блока являются управляющими входами устройства, выход схемы сравнения яэйяется управлякэщим выходом устройст ба. . . ,,., Источники ивфо{ у1ации, принятые во внимание при экспертизе

1/7

/f 718 1. Неслуховский К. С. Цифровые дифференциальньте анализаторы, М., Машиностроение, 1968, S2. Авторское свидетельство СССР №355631, кл. q Об D 1/О2, 1969.

Авторы

Даты

1979-03-05—Публикация

1976-12-28—Подача