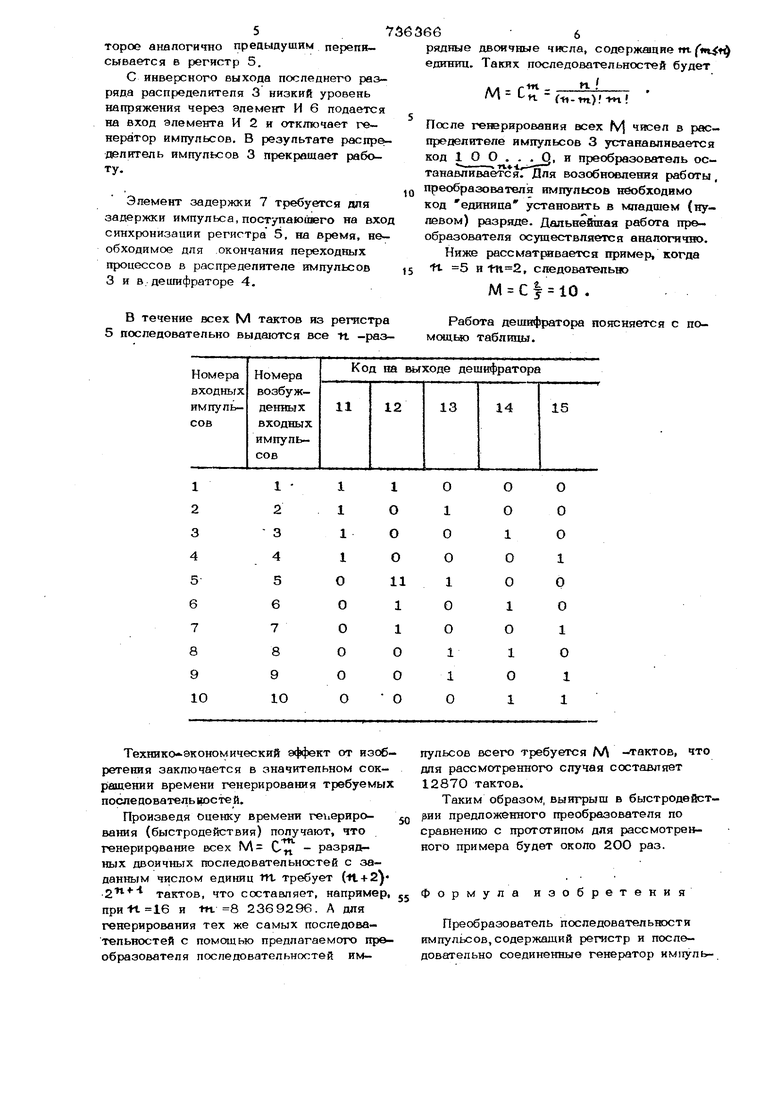

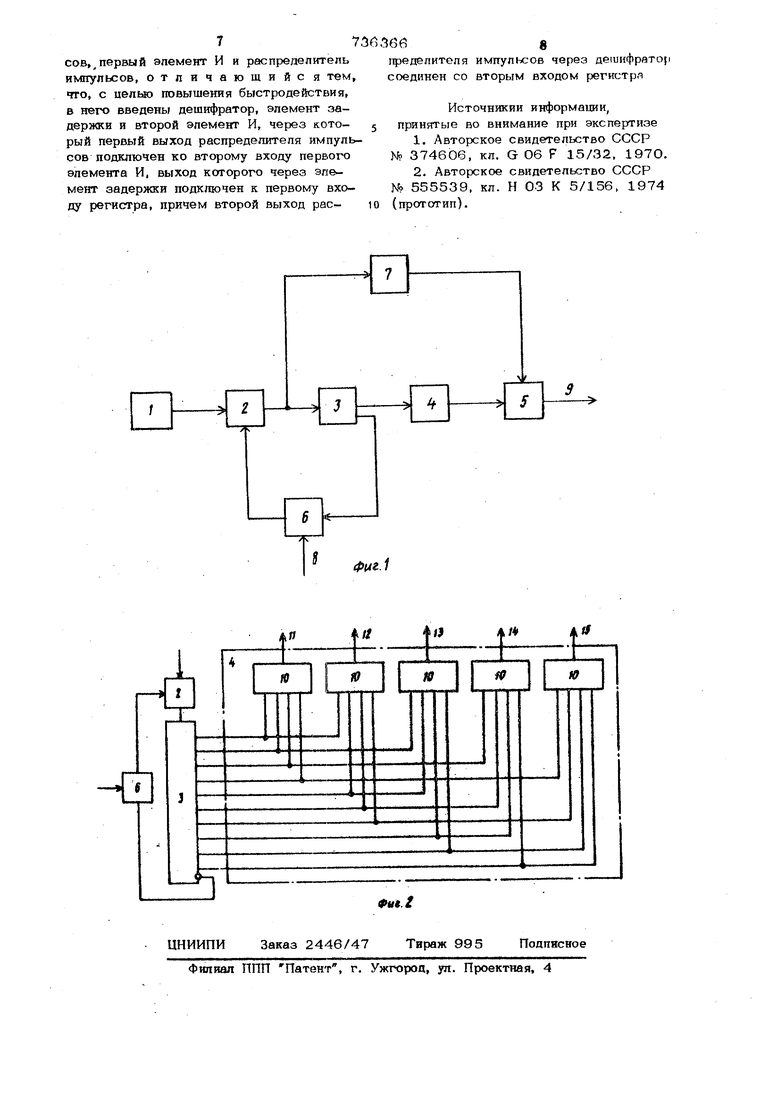

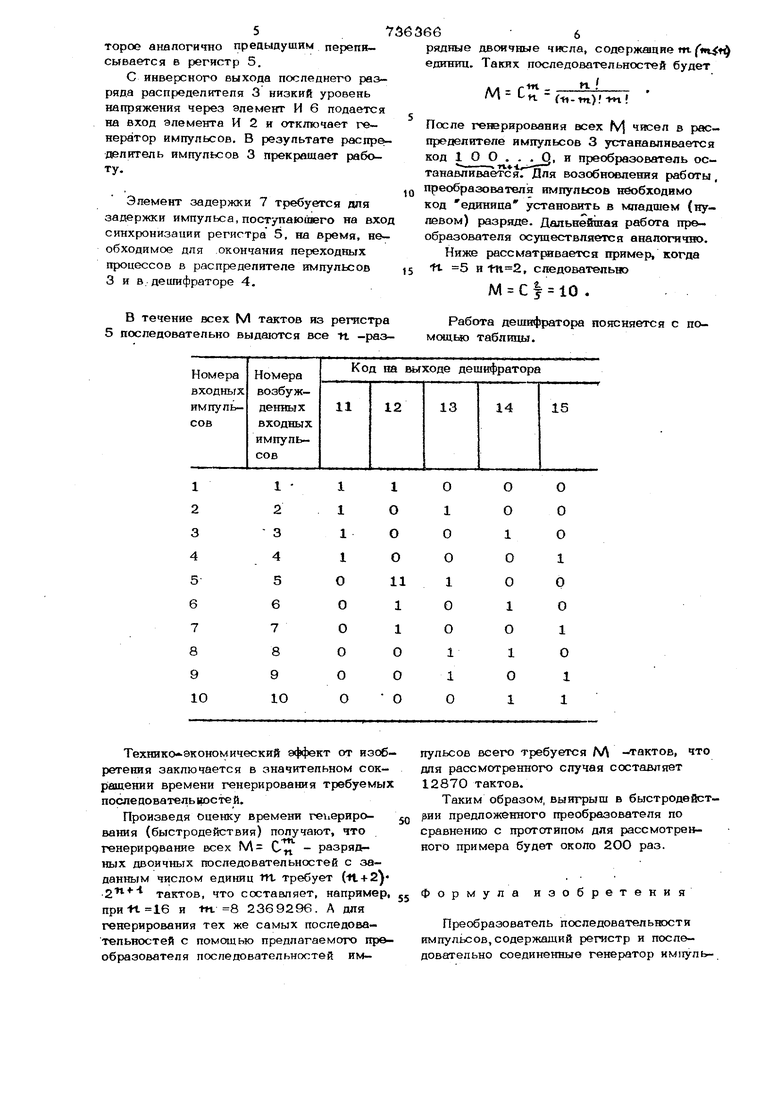

эпемента ИЛИ. Выход второго счетчика подключен к первому входу блока сравнения, второй вход которого соединен с выходом программиругадего устройства. Выход блока сравнения соединен с синхронизирующим входом регистра, разрядные входы которого соединены с выходом первого счетчика и со вторыми входами блока элементов И. Третьи входы регистра подключены к счетному входу первого счетчика. Однако 8ТОТ преобразователь имее1Т низкое быстродействие. Цепь изобретения - повышение быстродействия. Эта нель достигается тем, что в преобрасзователь последовательности импупьсов, содержащий регистр и последователь но соединенные генератор импульсов, первый элемент И и распределитель импульсов, введены дешифратор, элемент задержки и второй элемент И, через который первый выход распределителя импульсов подкщочен ко второму входу пер Бого эпемента И, выход которого через элемент задержки подключен к первому входу регистра, причем второй выход распределителя импульсов через дешифра тор соединен со вторым входом регистра На фиг. 1 изображена функциональная схема предлагаемого преобразователя; на фиг. 2 - структурная схема дешш|)ратора. Устройство содержит генератор .им- пульсов 1, первый элемент И 2, распредеоитель 3 импульсов, дешифратор 4, ре гистр 5, второй элемент И 6, элемент задержки 7, шину Пуск 8 и шину 9. Дешифратор 4 имеет разряд э1 1 и вьтхощ 1 . Число состояний распределителя 3 им пульсов равно ( С-и +i} одно из которых под номером О является исходным Выходы распределителя импульсов 3 под номером с 1 по подсоединены к входам дешифратора 4, число выходов которого соответствует чиспу разрядов р гистра 5, равного ft . Преобразователь работает следующим образом. Перед началом работы в нулевом раз ряде распределителя 3 устанавливается код 1, в остальных разрядах - О. В результате на инверсном выходе последнего разряда -появляется высокий урЭ- вень напряжения, который поступает на - вход второго элемента И 6. При подаче разрешающего сигнала (высокого уровня напряжения) на шине Пуск 8 на выход второго элемента И 6 появляется высоий уровень напряжения, благодаря которому серия импульсов, вырабатываемая генератором пмп мьсов 1 поступает через элемент И 2 на вход ситгхронизации импул1тсов доишфратора 4 и одновременно через элемент задержки 7 - на вход сттхронизации регистра 5. Первый импульс, вырабатываемый генератором импульсов 1, переписывает единицу из нулевого разряда в первь й разряд распределителя импульсов 3. С выхода первого разряда распределителя высокий потенциал поступает на первый вход дешифратора 4, В результате на выходах дешифратор вырабатывает первое TL -разрядное число, содерисаш е На едщсиц в старших разрядах JjjLiiQ tjS Первый импульс с выхода элеме1Йа И 2, пройдя через элемент задержки 7, поступает на вход сиггкронизации регистра 5. В результате этого в регистр 5 записывается первое генерируемое двоичное число 11... 10ОО...,0, которое с его выходных шин 9 передается по назначению. Во втором такте второй импульс в распре депителе импульсов 3 сдвигает единицу на один разряд, возбуждая соответственно его вторую выходную шину и соответствующий вход дешифратора 4, Благодаря этому дешифратор 4 вырабатывает второе генерируемое П. --разрядное члсло с ttl единицами, содержащее Ш-1 единиц в старших разрядах, а в («i- +1 )-ом разряде одну едишплу, т,е, двоичное число iT.T.ij3lO...OQ, которое аналогично первому пе шшется в регистр 5. В каждый последхтоздий такт импупьс с генератора га-лпульсов в распределителе 3 сдвигает едтгиду не один разряд, благодаря этим импульсам сдвига единица последовательно перемещается от младшбГО разряда к старшему, последователЕ но возбуждая выходные шины распределителя 3 и соответствующие входные шитшг дешифратора 4. Каждому возбужденному входу дешифратора 4 соответствует определенное двоичное число на его выходах, которое по тактам поступает в регистр 5. В последнем М -ом такте { М С1Г ) во буждается последняя-( ) выходная шина дешифратора 4, в результате чего на выходах дешифратора 4 появляется последнее генерируемое н -разрядное двоичное число, содержащее ги -одинип в младших разрядах 00...011 ...1, ко- торое аналогично предыдушим переписывается в регистр 5. С инверсного выхода последнего разряда распределителя 3 низкий уровень напряжения через элемент И 6 подается на вход элемента И 2 и отключает генератор импульсов, В результате распределитель импульсов 3 прекращает работу. Элемент задержки 7 требуется для задерхжи импульса, поступающего на вхо синхронизации регистра 5, на время, необходимое для окончания переходных процессов в распределителе импульсов 3 и в. дешифраторе 4. В течение всех М тактов из регистра 5 последовательно выдаются все tt -раз 7 6в рядные двоичные числа, содержадие т- ( единиц. Таких последовательностей будет f-H-tn). После генерирования всех fVl чисел в распределителе импульсов 3 устанавливается код 1 О О . ..Q, и преобразователь останавливается. Для возобновления работы, преобразователя импульсов нdoбxoднмo код единица установить в младшем (нулевом) разр51де. Дальнейшая работа преобразователя осуществляется аналогично. Ниже рассматривается пример, когда Н 5 и , следовательно М С| 10. Работа деишфратора поясняется с помощыо таблицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор циклов | 1981 |

|

SU964616A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1976 |

|

SU646327A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU930650A2 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU744546A1 |

Технико экономический эффект от изобретения заключается в значительном сокращении времени генерирования требуемых последователыюстей.

Произведя оценку времени геьерирования (быстродействия) получают, что генериррвание всех М С„ - разрядных двоичных последовательностей с заданным числом единиц ttt требует (tH-2) ,2И.-- тактов, что составляет, например, при-К 16 и ttt 8 2369296. А для генерирования тех же самых последовательностей с помощью предлагаемого преобразователя последовательностей импульсов всего требуется М -тактов, что для рассмотренного случая составляет 12870 тактов.

Таким образом, выигрыш в быстродейстрии предложенного преобразователя по сравнению с прототипом для рассмотренного примера будет около 2ОО раз.

формула изобретения

Преобразователь последовательности импульсов, содержащий регистр и последовательно соединенные генератор имцуль77сов,первый элемент И и распределитель иктульсов, отличающийся тем, «гго, с целью повышения быстродейс:твия, в него введены дешифратор, элемент задержки и второй элемент И, через который первый выход распределителя импульсов подключен ко второму входу первого элемента И, выход которого через элемент задержки подключен к первому входу регистра, причем второй выход расев8пределителя импульсов через дешифратор соединен со вторым входом регистря Источникии информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 374606, кл. G Об F 15/32, 197О. 2.Авторское свидетельство СССР № 555539, кл. Н 03 К 5/156, 1974 (прототип).

Авторы

Даты

1980-05-25—Публикация

1977-12-01—Подача