(54) ЯЧЕЙКА ПАМЯТИ ДЛЯ РЕГИСТРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования временных интервалов | 1982 |

|

SU1070532A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Устройство для ввода дискретных сигналов | 1988 |

|

SU1522221A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| Устройство для разделения импульсного потока на периодические последовательности импульсов | 1988 |

|

SU1608791A1 |

| Цифровой компенсатор выпадений телевизионного сигнала яркости | 1985 |

|

SU1269274A1 |

| ЦИФРОВОЙ ПЕРИОДОМЕР | 1991 |

|

RU2011997C1 |

| Сенсорный переключатель | 1982 |

|

SU1051720A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в электронных вычислительных машинах .

Известен счетный триггер, содержащий прямой и инверсный однофазные тактируемые D-триггеры с перекрестным переключением их выходов ко. входам, объединенные тактовые входы которых образуют счетный вход триггера 1.

Наиболее близким к предлагаемому по технической сущности является регистровое запоминающее устройство с последовательной записью, содержащее в качестве ячеек памяти регистры, соединенные через вентили записи, сигнальные триггеры по числу.регистров, линии задержки и вентили задержки 2 .

Каждое из рассматриваемых устройств можно использовать тсшько для одной цели: либо только для счёта, либо толькоДЛЯ записи и хранения информации.X

Недостатком известных устройств является низкая помехоустойчивость в силу выбранных схем построения.

Цель изобретения - повышение помех бус т ойчйв сю Ти ячейки памяти для регистра.

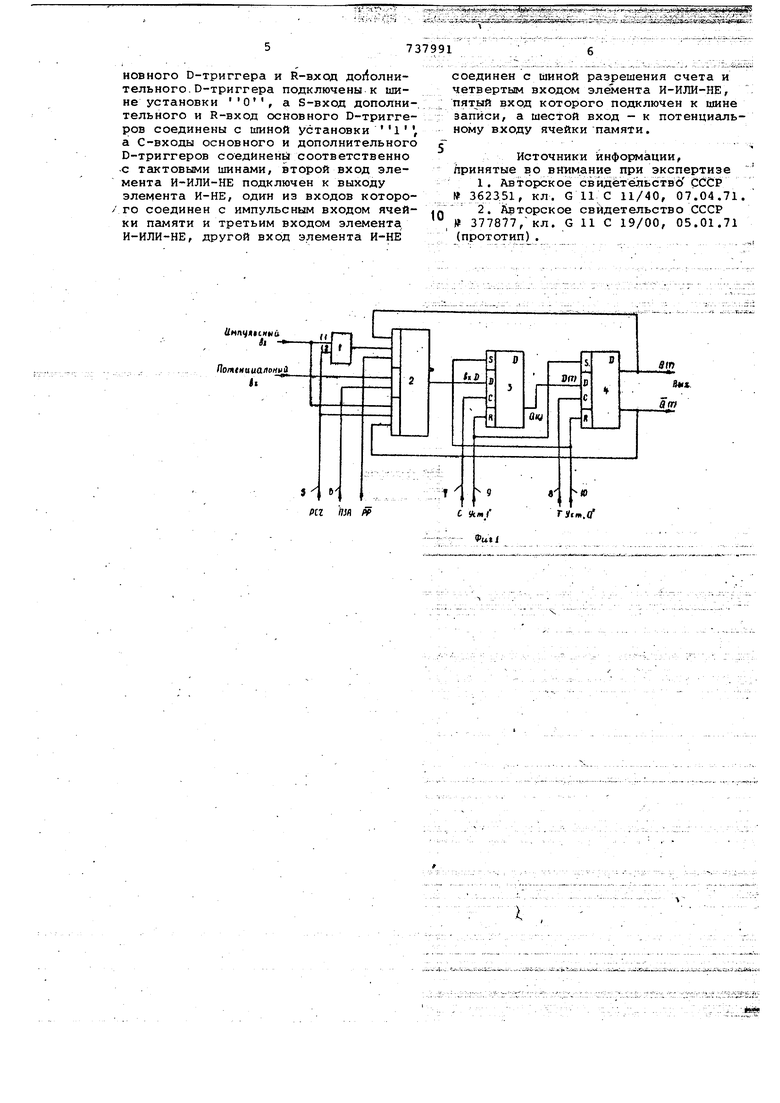

Поставленная цель достигается тем, что в ячейку памяти для регистра,содержащую основной D-триггер и элемент И-НЕ, шину разрешения счета, шину

5 зап,иси, тактовые щины и шины установки Ч и О, введены дополнительный D-триггер и элемент И-ИЛИ-НЕ; выход которбТб Соединен с D-входом основного D-триггера, выход основно0 го р-триггера подсоединен к D-входу дополнительного D-триггера, выходы которого соединены с выходами разряда регистра и с первыми входбми элемен там И-ИЛИ-НЕ соответственно, S-вход

15 основного D-триггера и R-вход допол-нительног D-триггера подключены к

Ш4№у тайо§кй О V а S-вход дополн.ительного и R-вход основного D-триггерЬв соединены с .шиной установки , С-входы основного и дополнительного D-триггеров сюединены соответственно с тактовыми шинами,

второй .вхбд элемента И-КЛ1 -НЕ подклю:; чен к выходу элемента И-НЕ, один из

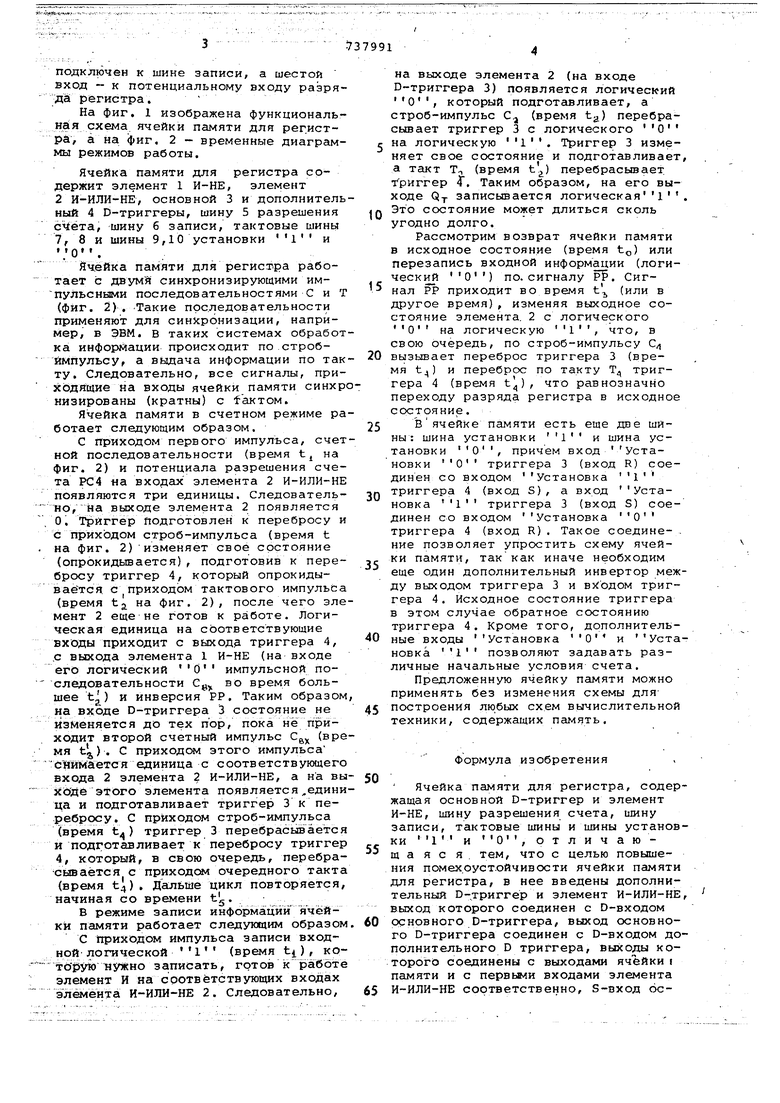

25 входов которого соединен с импульсным входом разряда регистра и третьим входом элемента И-ИЛИ-НЕ, другой вход элемента И-НЕ соединен с циной разрешения счета и четвер;гым входом элемента И-ИЛИ-НЕ, пятый вход которого подключен к шине записи, а шестой вход - к потенциальному входу разряда регистра. На фиг, 1 изображена функциональна я схема ячейки памяти для регистра, а на фиг. 2 - временные диаграммы режимов работы. Ячейка памяти для регистра содержит элемент 1 И-НЕ, элемент 2 И-ИЛИ-НЕ, основной 3 и дополнитель ный 4 D-триггеры, шину 5 разрешения , шину б записи, тактовые шины 7, 8 и шины 9,10 установки i и . О . Ячейка памяти для регистра работает с двумй синхронизирующими импульсными последовательностями С и Т (фиг. 2) . -Такие последовательности применяют для синхронизации, например, в ЭВМ. в таких системах обработ ка информации происходит по стробимпульсу, а выдача информации по так ту. Следовательно, все сигналы, приходящие на входы ячейки памяти синхр низированы (кратны) с fактом. Ячейка памяти в счетном режиме ра ботает следующим образом. С приходом первого импульса, счет ной последовательности (время tj на фиг. 2) и потенциала разрешения счета РС4 «а входах элемента 2 И-ИЛИ-НЕ появляются три единицы. Следовательно, на выходе элемента 2 появляется 0. Триггер Подготовлен к перебросу и с приходом строб-импульса (время t на фиг. 2)изменяет свое состояние (опрокидьшается), подготовив к перебросу триггер 4, который опрокидывается с приходом тактового импульса (время tj на фиг. 2), после чего эле мент 2 еще не готов к работе. Логическая единица на соответствующие Бходы приходит с выходэ триггера 4, ,с выхода элемента 1 И-НЕ (на входе его логический О импульсной последовательности Cg во время большее tj) и инверсия PP. Таким образом на входе D-триггера 3 состояние не изменяется до тех пор, пока не приходит второй счетный импульс С (вре мя tj) . С приходом этого импульса снимается единица с соответствующего входа 2 элемента 2 И-ИЛИ-НЕ, а на вы хеде этого элемента появляется,едини ца и подготавливает триггер 3 к перебросу. С приходом строб-импульса (время Ц) триггер 3 перебрасыв ается и подготавливает к перебросу триггер 4, который, в свою очередь, перебраСБшаётся с приходом очередного такта (время t,) . Дальше цикл повторяется, начиная со времени t. В режиме записи информа цйй ячейки памяти работает следующим образом С гфиходом импульса записи входной логической 1 (время t), коtdpyto нужно записать, готов к работе элемент И на сротвётствуюпщх входах элетлёнта И-ИЛИ-НЕ 2. Следовательно, на выходе элемента 2 (на входе D-триггера 3) появляется логический О, который подготавливает, а строб-импульс С (время tj.) перебрасывает триггер 3 с логического О на логическую Ч. Триггер 3 изменяет свое состояние и подготавливает, а такт Тт (время t.) перебрасывает. триггер Т. Таким образом, на его выходе QT записывается логическая . Это состояние может длиться сколь угодно долго. Рассмотрим возврат ячейки памяти в исходное состояние (время t,) или перезапись входной информации (логический О) по. сигналу PP. Сигнал РР приходит во время t, (или в другое время), изменяя выходное состояние элемента. 2 с логического 0 на логическую , что, в свою очередь, по строб-импульсу С вызывает переброс триггера 3 (время и переброс по та.кту Т, триггера 4 (время t,), что равнозначно переходу разряда регистра в исходное состояние. Вячейке памяти есть еще две шины: шина установки и шина усУстатановкипричем вход новки О триггера 3 (вход R) соединен со входом Установка i триггера 4 (вход S) , а вход Установка триггера 3 (вход S) соеУстановкадинен со входом триггера 4 (вход R) . Такое соедине- . ние позволяет упростить схему ячейки памяти, так как иначе необходим еще один дополнительный инвертор между выходом триггера 3 и триггера 4. Исходное состояние триггера в этом случае обратное состоянию триггера 4. Кроме того, дополнительУстаные входы Установка позволяют задавать различные начальные условия счета. Предложенную ячейку памяти можно применять без изменения схемы для построения любых схем вычислительной техники, содержащих память. Формула изобретения Ячейка памяти для регистра, содержащая основной D-триггер и элемент И-НЕ, шину разрешения счета, шину записи, тактовые шины и шины установки Ч и О, отличающ а я с я . тем, что с целью повышения помехоустойчивости ячейки памяти для регистра, в нее введены дополнительный D-триггер и элемент И-ИЛИ-НЕ, выход которого соединен с D-входом основного D-триггера, выход основного D-триггера соединен с D-входом дополнительного D триггера, выходы которог1Э соединены с выходами ячейки памяти и с первыми входами элемента И-ИЛИ-НЕ соответственно, S-вход 6сновного D-триггера и R-вход дополнительного. D-триггера подключены к шине установки О, а S-вход дополнительного и R-вход основного D-триггеров соединены с шиной установки 1, а С-входы основного и дополнительного D-триггеров соединена соответственно с тактовыми шинами, второй вход элемента И-ИЛИ-НЕ подключен к выходу элемента И-НЕ, один из входов которого соединен с импульсным входом ячейки памяти и третьим входом элемента/ И-ИЛИ-НЕ, другой вход элемента И-НЕ

tfHnV IICMNU

il

flonHHUUCLItOHVU

t

т п№ №

737991

соединен с шиной разрешения счета и четвертым входом элемента И-ИЛИ-НЕ, пятили вход которого подключен к шине записи, а шестой вход - к потенциальному входу ячейки -памяти.

Источники информации, принятые во внимание при экспертизе

TUtm.ff

с Vimf futi

Фаг.2

Авторы

Даты

1980-05-30—Публикация

1978-01-11—Подача