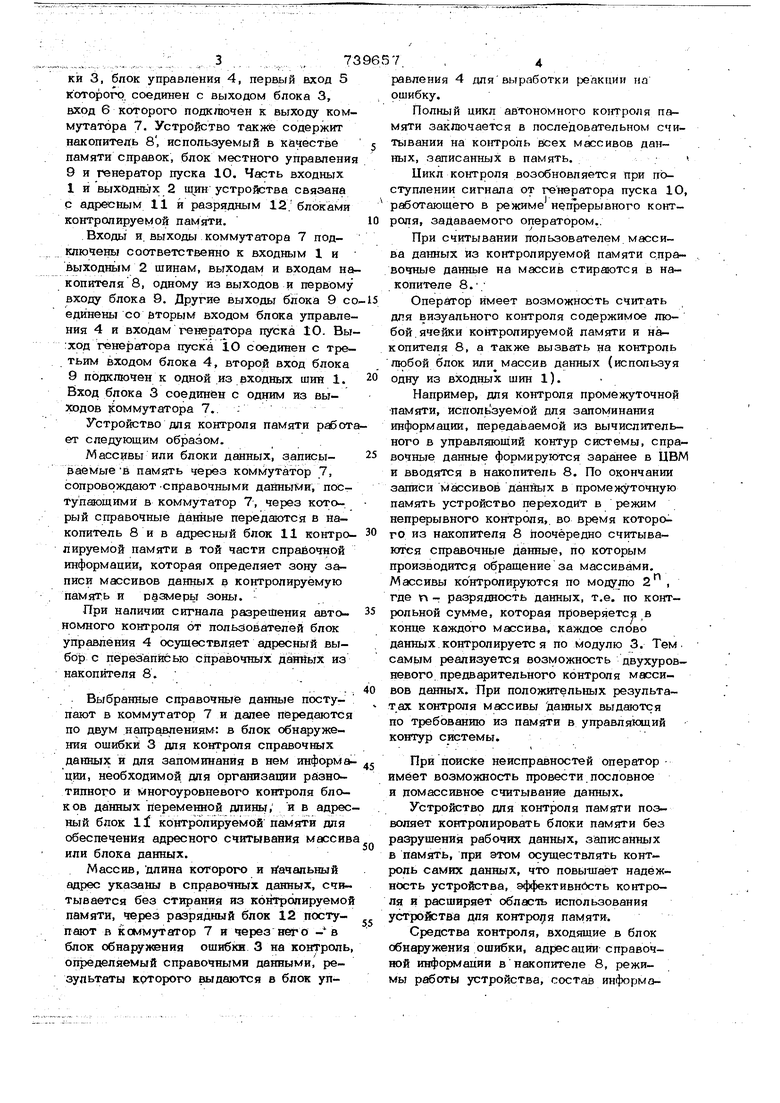

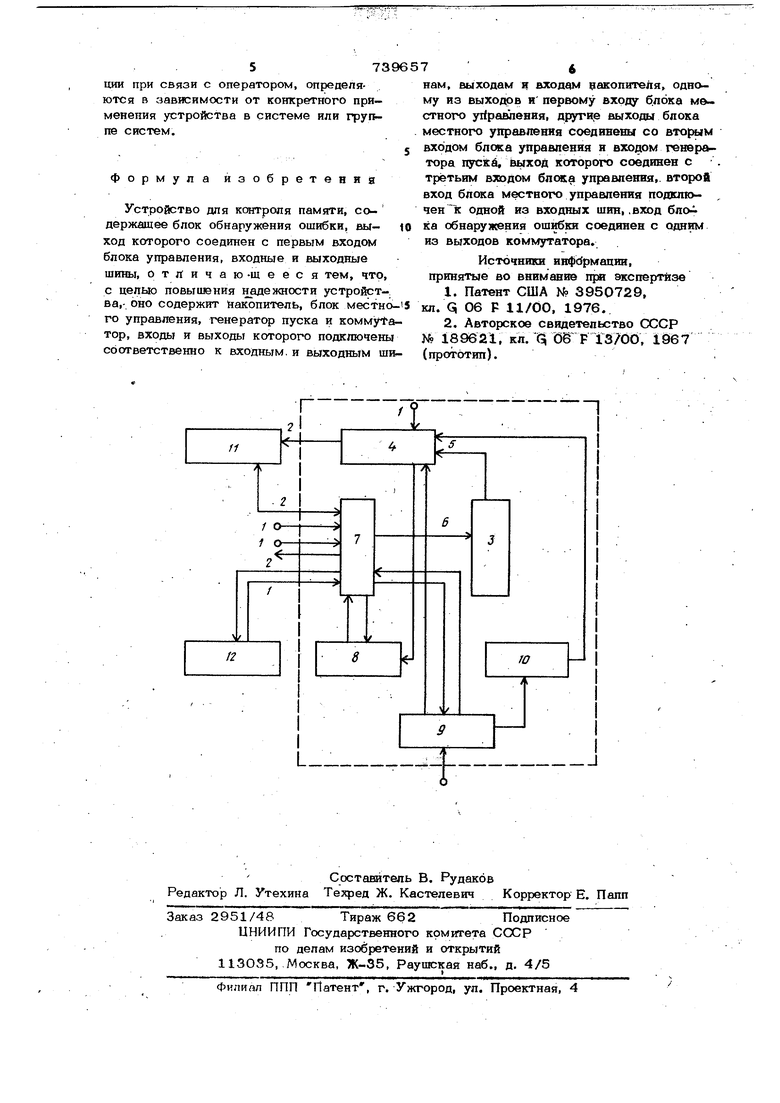

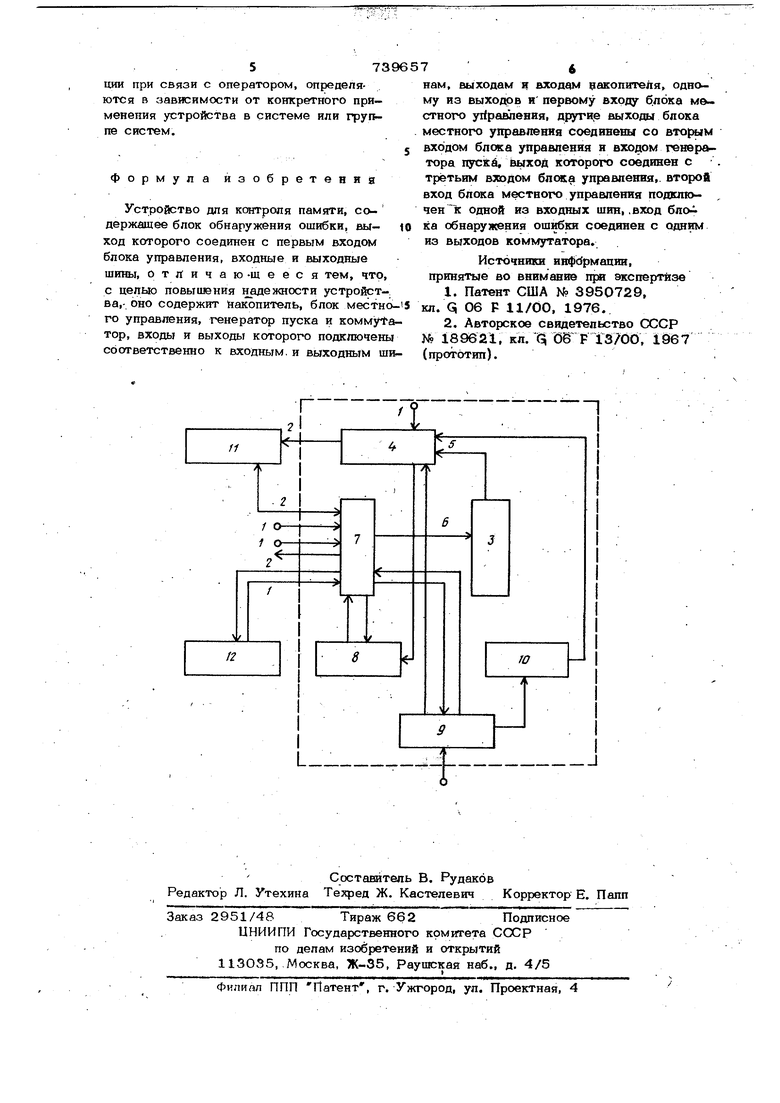

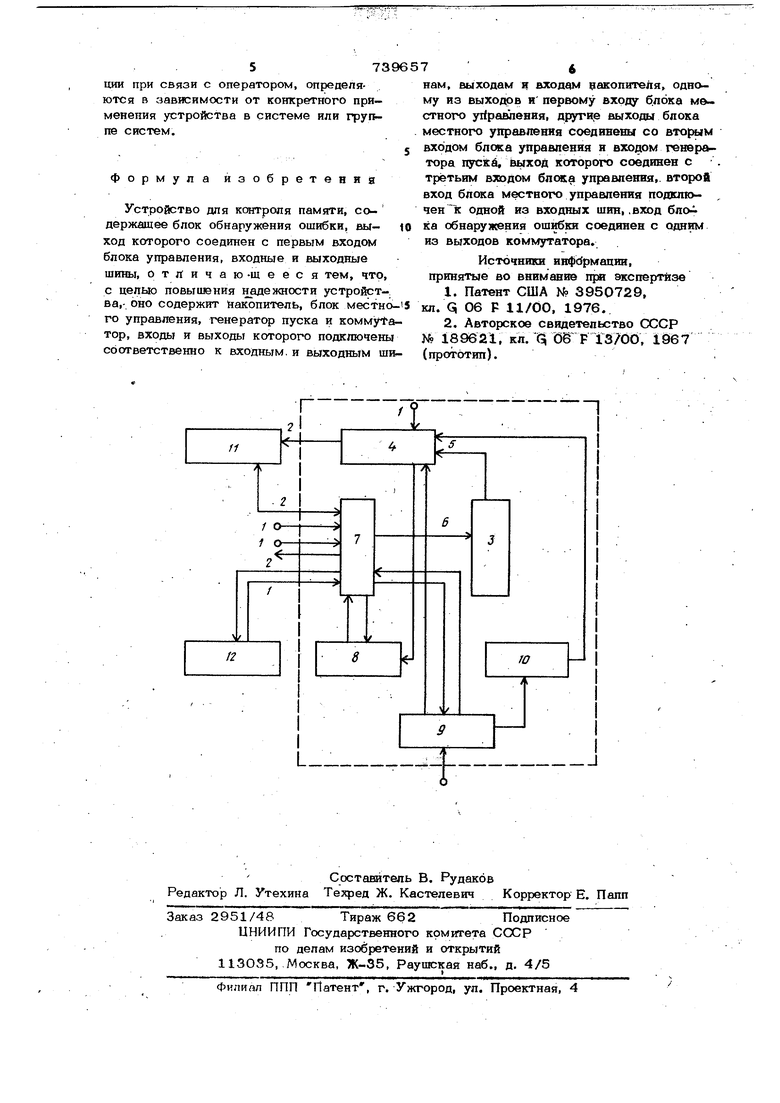

. ; Изобретение ртйосится к области зап«. мянйюших усттэойста. Известное устройство для контрояй Памяти, осушествпяет как текушиб конгфоль данвых, передаваемых между па мятыо и пользователями, так и дяагностихеский койтроль памйги методом записисчитывания коетрол эной информации из памяти в те периоды.когда память не зат ружена данными Щ ..Однако это устройство вв позволяет ; проводить предварич тельнь|й контроль данных, записанных в naMsiTb. Из известных устройств наиболее близким по технической сущности к изобретению явйяется устройство для контроля.пвмягги, содержащее блок обн эружения ри1иб кя, Bbixoji которого соединен с первым входом блока управления, входные и выходные щвнц и регистр числа 22} . Это , устройство не позволяет обнаружить ошибку в коде; записанном в память, иошибки, возншсающие в кодах в результате обоев или разрушения данных при дпитедьном хранении, что снижает его надеясность. Целью изобретения является повышение надежности устройства. Эта цель достигается тем, что предложенное устройство содержит накопитель, блок местного управления, генератор пуска и коммутатор, входы и выходь которого подключены соответственно к входным и выходным шинам, выходам и входам накопителя, одному из выходов и первому входу блока местного управления. Другие выходы блока местного управления соединены со вторым входом блока управления н входом генерапгора пуска, выход которо- ГО соединен----с третьим входом бпока управления. Второй вход блока местнотч) управления подключен к одной из входных шин, а вход блока обн ужения ошибки к одному выходу коммутатора. На чертеже изображена структурная схема предложенного устройства. Устройство содержит входные 1 и выходные 2 шины, блок обнаружения ошиб. ,:,. .3 . . ,. .,„. ,7 ки 3, блок управления 4, первый вход 5 которого, соединен с выходом блока 3, вход 6 которого подключен к выходу коммутатора 7- Устройство также содержит накопитель 8, используемый в качестве памяти справок, блок местного управлени 9 и генератор пуска 10, Часть входных I и выходнь1Х 2 шин устройства связана С адресным 11 и разрядным 12; блоками контролируемой памяти. Входь и. выходы коммутатора 7 подключены соответственно к входным 1 и выходньтм 2 шинам, выходам и входам на копителя 8, одному из выходов и первому входу блока 9. Другие выходы блока 9 с единены со вторым входом блока управления 4 и входам генератора пуска 10. Вы :ход генератора пуска 10 соединен с третьим входом блока 4, второй вход блока 9 подключен к одной из входных шин 1. Вход блока 3 соединен с одним из выходов lioMMyTBTOpa 7.. : Устройство для контроля памяти работ ет следующим образом. Массивы или блоки данных, записываемые в память через коммутатор 7, сопровождают-справочными дайныМи, поступающими в коммутатор 7, через который справочные данные передаются в накопитель 8 и в адресный блок 11 контролируемой памяти в той части спрайочной информации, которая определяет зону записи массивов данных в контролируемую память и размеры зоны. При наличии сигнала разрешения авто.. номного контроля от пользователей блок управления 4 осуществляет адресный выбор с перезаписью справочных данных из накопителя 8. Выбранные справочные данные поступают в коммутатор 7 и далее передаются по двум направлениям: в блок обнаружения ошибки 3 для контроля справочных данных и для запоминания в нем информа ции, необходимой для организации разнотипного и Многоуровневого контроля блоков данных переменной длины, и в адрес ный блок ll контролируемой памяти для обеспечения адресного считывания массив или блока данных. Массив, длина которого и начальный адрес указаны в справочных данных, считывается без стирания из контролируемой памяти, через разрядный блок 12 поступают в коммутатор 7 и через него - в блок обнарузкения ошибки 3 на контроль определяемый справочными данными, результаты которого выдаются в блок уп7равления 4 для выработки реакции но ошибку. Полный цикл автономного контроля памяти заключается в последовательном считывании на контроль всех массивов данных, записанных в память. Цикл контроля возобновляется при поступлении сигнала от генератора пуска 10, работающего в режиме непрерывного контроля, задаваемого оператором.. При считывании пользователем, массива данных Из контролируемой памяти справочные данные на массив стираются в накопителе 8.. Операггор имеет возможность считать для визуального контроля содержимое любой, ячейки контролируемой памяти и накопителя 8, а также вызвать на контроль любой блок или массив данных (используя одну из входных шин 1). Например, для контроля промежуточной памяти, используемой для запоминания информации, передаваемой из вычислительного в управляющий контур системы, справочные данные формируются заранее в ЦВМ и вводятся в накопитель 8. По окончании записи Массивов данйых в промежуточную память устройство переходит в режим непрерывного контроля,, во время которого из накопителя 8 поочередно считываются справочные данные, по которым производится обращение за массивами. Массивы контролируются по модулю 2 где п - разрядность данных, т.е. по контрольной сумме, которая проверяется в конце каждого массива каждое слово данных контролируете я по модулю 3. Тем самым реализуется возможность двухуровневого предварительного контроля массивов данных. При положительных результатах контроля массивы данных выдаются по требованию из памяти в управляющий контур системы. При поисйе неисправностей оператор имеет возможность провести пословное и помассивное считывание данных. Устройство для контроля памяти позволяет контролировать блоки памяти без разрушения рабочих данных, записанных в память, при этом осуществлять контроль самих данных, что повышает надёжность устройства, эффективнбсть контроля и расширяет область использования устройства для контро; я памяти. Средства контроля, входящие в блок обнаружения ошибки, адресации справочной информации в накопителе 8, режимы работы устройства, состав инф(зрма573ции при связи с оператором, определяются в зависимости от конкретного применения устройства в системе или группе систем. формула изобретения Устройство для контроля памяти, содержащее блок обнаружения ошибки, выход которого соединен с первым входом блока управления, входные и выходные шины, отличаю-щееся тем, что, с целью повышения надежности устройства,- оно содержит йакопитель, блок местно го управления, генератор пуска и коммута тор, входы и выходы которого подключены соответственно к входным, и выходным ш 7 выходам и входом накопителя, однонам, му из выходов и первому входу блока местного управления, другце выходы блока местного управления соедивены со вторым входом блока управления и входом генератора пуски, выход которого соединен с третьим входом блсжа1 управпення,. второй вход блока местного управления подклю- , ченк одной из входных шин, .вход блока обнаружения ошибки соединен с одним из выходов коммутатора. Источники информации, принятые во внимание щж экспертизе 1.Патент США N° 3950729, кл. Q 06 F 11/00, 1976. 2.Авторское свидетельство СССР № 189621, кл. ( ОёР 13706, 1967 (прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Запоминающее устройство | 1979 |

|

SU826423A1 |

| Устройство для контроля программ | 1983 |

|

SU1136172A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Запоминающее устройство с исправлением ошибок | 1989 |

|

SU1667156A1 |

..

I

Авторы

Даты

1980-06-05—Публикация

1977-10-05—Подача