(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Интегратор азимутных импульсов | 1977 |

|

SU691877A2 |

| Универсальный цифровой прибор | 1981 |

|

SU998964A1 |

| Адаптивный умножитель частоты | 1989 |

|

SU1793538A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

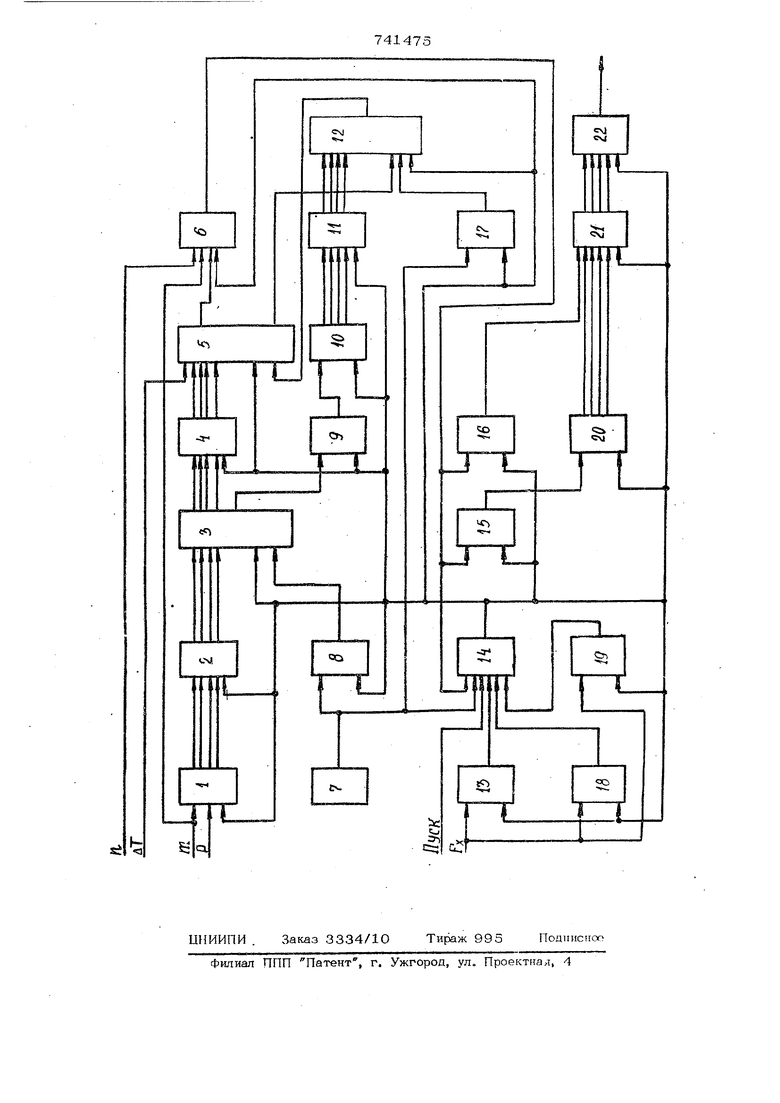

Изобретение предназначено для исполь зования в радиоэлектронных установках различного назначения, в частности в электроизмерительной технике. Известны умножители частоты| содержащие два цифровых дифференцирующих устройства, которые генерируют импульс на переднем и заднем фронтах входного импульса, удваивая частоту выходных импульсов. Данный умножитель имеет фикси рованный коэффициент умножения, равный двум Щ . Недостатком известных умножителей является недостаточная точность и надежность работы. Известен также умножитель частоты, содержащий перемножитель, два saioaa которого соединены с шинами управления, а выходы через первый блок логических элементов И соединены со входами делителя частоты, один из выходов которого соединен с первым входом одного ключа, выход которого соединен со входом счет чика импульсов, а другие выходы делитеЛЯ частоты через второй блок логических элементов И соединены с соответствующими входами блока коррекции, выход которого соединен с первым входом второго делителя частоты, выход которого соеди нен первым входом блока управления, второй вход которого соединен с выходом генератора тактовой частоты и первым входом второго ключа, выход которого со- единен со входом первого делителя частоты, третий вход блока управления соединен с шиной пуска, а выходы счетчика импульсов через третий логический блок элементов И соединены со входами третьего делителя частоты, выход которого соединен со входом блока коррекции, дополнительный вькод которого соединен с одним из входов третьего делителя частоты, причем второй вход блока коррекции соединен с шиной управления, а выходы управления упомянутых перемножителя блоков логических элементов И, делителей частоты, ключей, счетчика импульсов и блока коррекции соединены с. выходом блока управления, а четвертый вход второго делителя частоты соединен с четвертой шиной управления Г21, Недостатком этого умножителя частоты является узкий диапазон, изменения 1соэффи циентов умножения, невысокая точность и несоответствие формы вьрсодного сигнала форме входного сигнала. Цель изобретения - улучшение соответ ствия формы выходного сигнала форме входного сигнала. Поставленная цель достигается тем, что в умножитель частоты, содержащий перемножитель, два входа которого соединены с шинами управления, а выходы через блок логических элементов И соединень со входами делителя частоты, один из выходов которого соединен с первым входом одного ключа, вьпсод которого соединен со входом счетчика импульсов, а другие вькоды делителя частоты через второй блок логических элементов И соединены с соответствующими входами бло- ка коррекции, выход которого соеди.нен с первым входом второго, делителя частоты, выход которого соединен с первым входом блока управления, второй вход которого соед1шен с выходом генератора тактовой частоты, и первым входом второго ключа, выход которого соединен со входом первого делителя частоты, третий вход блока управления соединен с шиной пуска, а выходы счетчика импульсов через третий логический блок элементов И соединены со входами третьего делителя частоты, выход которого соединен со входом блока коррек ции, дополнительный выход которого соеди нен с одним из входов третьего делителя частоты, причем второй вход блока коррек ции соединен с шиной-управления, авходы управления упомя11утых перемножителя блоков логических элементов И, делителей частотЫ} ключей, счетчика импульсов и .блока коррекции соединены, с выходом блока управления, а четвертый вход второго делителя чистоты соединен с четвертой шиной управления, введены три дополнительных ключа, блок памяти, преобра зователи код-напряжение и напряжениекод, анализатор формы и анализатор периода входного сигнала и формирователь им пульсов, один вход которого соединен со входной шиной и первыми входами анализатора формы и анализатора периода входного сигнала, вторые входы которых подрлючены к выходу бйока управления и ко входам управления формирователя импуль. сов дополнительных ключей, преобраоователей напряжение-код и код-напряжение, блока памяти, а выходами анализатора формы и анализатора периода соединены с дополнительными входами блока управления, первый вход которого соединен со вторым ходом двух дополнительных ключей, выходы которых соответственно соединены со входами преобразователя напряжение-код и блока памяти, информационные входы которого соединены с выходами .преобразователя напряжение-код, а выходы - со входами преобразователя код-напряжение, при этом второй вход третьего дополнительного ключа соединен с выходом генератора тактовой частоты, а выход - с дополни-, тельным входом третьего делителя частоты, . На чертеже приведена структурная электрическая схема умножителя частоты. Умножитель частоты содержит перемножитель 1, первый блок 2 логических элементов И, первый делитель 3 частоты, второй блок 4 логических элементов И, блок 5 коррекции, второй {целитель 6 частоты. генератор 7 тактовых импульсов, ключи 8 и 9, счетчик 10 импульсов, третий блок И логических элементов И, третий делитель 12 частоты, формирователь 13 импульсов, блок 14 управления, ключи 15, 1 и 17, анализатор 18 формы входного сигнала, анализатор 19 периода входного сигнала, преобразователь 2О напряжениекод, блок 21 памяти и преобразователь 22 код-напряжение. Умножитель частоты работает следующим образом. В исходном состоянии все делители частоты, счетчики импульсов и блок памяти очищены, ключи 8, 9, 15, 16 и 17 закрыты. Переключателю 1 задаются код числителя m коэфф1щиента умножения и код числа дискрет р гш период входного сигнала. Делитепю 6 частоты задаются коды числителя m и знаменателя п коэффт ициента умножения . Блоку коррекции задается код допустимой погрешности дТ периода выходного сигнала умножителя. Пусковой сигнал подается на вход блока 14 управления, по сигналам .которого перемножителем 1 перемножаются коды тир, результат умножения заносится через блок 2 логических, элементов И в делитель 3 частоты (коэффициент деления делителя 3 частоты устанавливается равным тр) и запускается формирователь 13 импульсов, который измеряет длительност периода входного сирнапа и выдает в бло 14 управления импульсы с периодом следования, равным периоду Ту входного си нала. По первому выходному импульсу формирователя13 импульсов блоком 14 управления открываются ключи 8 и 9, через к торые в течение периода времени Т в управляющий счетчик 10 импульсов будет введено число , равное целой части чисQ -ti П+ гдеМ-- оТ - чисHmp-Ч гпр ло импульсов генератора 7 тактовой частоты{Q за период Ту., Л N - остаток импульсов, накопленный в делителе 3 часто ты к моменту выработки второго вьйодно го импу-льса формирователя 13 импульсов По второму выходному импульсу формирователя 13 импульсов блоком 14 управления закрываются ключи 8 и Q, содержимое счетчика Ю импульсов через блок 11 логических элементов И заносится Б делитель 12 частоты (коэффициент деления этого делителя устанавливается равным ), содержимое делителя 3 частоты через блок 4 логических элементов И заносится в блок 5 коррекции, открываются ключи 1й и 17, запускается преоб- разователь 2 О напряжение-код. Через открытый ключ 17 импульсы генератора 7 тактовой частоты f Q поступают в делитель 12 частоты, на выходе которого формируется последовательность импульсов с периодом следования ,/-f . подающаяся в блок 5 коррекции. Последнее осуществляет временной задержкой и изменением коэффициента деления делителя 12 частоты на единицу коррекцию временного положения выходных импульсов делителя 12 частоты так, чтобы погрещность момента появления кЪждого импульса не превышала допустимую погрешность Д Т периода выходного сигнала умножителя. Таким образом, импульсы на выходе блока S коррекции имеют с необходимой точностью период следования 1д-Я,Дс5 , С выхода делителя б частоты на выход которого по даются выходные импульсы корректирующего блока 5 коррекции снимается импульсная последовательность частоты i f mp/mN |э/Тк pF , где F - частота входного сигнала. Преобразователь 20 напряжение-код осуществляет дискретизацию входного сигнала Р в моменты времени, задаваемые вькодными импульсами .делителя б частоты. Коды дискрет входногосигнала фиксируются в блоке 21 памяти. По третьему выходному импульсу формирователя 13 импульсов, к моменту выработки которого в блоке 21 памяти зафиксировано Р дискрет входного сигнала, блоком 14 управления вырабатываются сигналы, по которым прекращают работу преобразователь 20 напряжение-код, очищается делитель 6 частоты и его коэффициент деления устанавливается равным Г закрывается ключ 14 и открывается ключ 16. Через открытый ключ 16 выходными импульсами делителя б, частота следования которых з. осуществляется циклическое считывание кодов- дискрет входного сигнала из блока 21 памяти, Коды дискрет входного сигнала поступают из блока 21 памяти в преобразователь 22 код-напряжение, на выходе которого формируется сигнал частоты форма которого повторяет форму входного сигнала. При изменении формы входного сигналй или длительности его периода, соответственно анализатором 18 формы входного сигнала или анализатором 19 периода входного сигнала вырабатывается сигнал, по которому блок 14 управления устанавливает все элементы умножителя в исходное состояние, и затем умножитель частоты .автоматически начинает работу сигнала. . Настоящий умножитель частоты позволяет сохранить форму сигнала при умноже- ИИ его частоты, при этом погрешность ериода выходного сигнала умножителя не превышает заданной допустимой погрешости. Формула изобретения Умножитель частоты, содержащий пеемнох итель} два входа которого соединены с шинами управления, а выходы через ервый блок логических элементов И соеинены со входами, делителя частоты, один з выходов Которого соединен с первым ходом одного ключа, выход которого соеинен со входом счетчика импульсов, а ругие выходы дели еля частоты через вто-

рой блок логических элементов И соединеJibi с соответствующими входами блока коррекции, Bbsxoa которого соединен с первым входом второго делителя частоты, выход которого соединен с, первым входом блока управления, второй вход которого соединен с выходом генератора тактовой частоты и первым входом второго ключа, выход которого соединен со входом первого делителя частоты, третий вход блока управления соединен с шиной пуска, а выходы счетчика импульсов чер.ез третий блок логических элементов И соединены со входами третьего делителя частоты, выход которого соединен со входом блока коррекции, дополнительный выход которого соединен с одним иэ входов третьего делителя частоты,причем, второй вход блока корреииш соединен с шиной управления и входы управления упомянутых перемножителя блоков логических элементоё И, делителей частоты, ключей, счетчика импульсов и блока коррекции соединены с выходом блока управления, а четвертый вход второго делителя частоты соединен с четвертой шиной управления, о т л и ч а .ю щ и и с я тем, что, с целью улуч шения соответств1-ш формы выходного сйг нала форме входного сигнала, в него введены три дополнительных ключа блок па мяти, преобразователи код-напряжение и напряжение-код, анализатор формы и анализатор периода входного сигнала и форнмирователь импульсов, один вход которого соединен со входной шиной и первыми входами анализатора формы и анализатора периода входного сигналве вторые входы ко торых подключены к выходу блока управления и ко входам управления формирователя импульсов дополнительных ключей, преобразователей напряжение-код и код-напряж.ение, блока памяти, а выходами анализатора формы и анализатора периода соединены с дополнительными входами блока управления, первый вход которого соединен со вторым входом двух дополнительlibK ключей, выходы которых соответственно соединены со входами преобразователя напряжение-код и блока памяти, информационные входы которого соединены с выходами преобразователя напряжение-код, а выходы - со входами преобразователя код-напряжение, при этом второй вход третьего дополнительного ключа соединен с выходом генератора тактовой частоты, а выход - с дополнитефным входом третьего делителя частоты.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-06-15—Публикация

1977-10-06—Подача