Изобретение относится к вычислительг ной тахнике и может быть использовано в цифровых вычислительных машинах, в устройствах ввода-вьшода, в устройствах управления к в устройствах обработки информации. Известны запоминающие устройства, построенные на интегральных микросхемах ОЗУ с использованием биполярных и МОП-транзисторов Ш. Известно запоминающее устройство, Каждое число в котором образовано набором ft микросхем ОЗУ, параллельно объединенных по адресным шинам и по шинам управления, и содержащие накопитель, первые выходы которого соединены с одними из входов коммутаторов,. деши4 ратор, входы которого соединены с вторы ми выходами накопителя, а выходы дешифратора связаны с другими входами коммутаторов. L27 Наиболее близким техническим решением к данному является устройство, сен держащее микросхему ОЗУ (где Л разрядность слов, выбираемых из запоминающего устройства, причем, предполагается, что в каждой микросхеме ОЗУ хранятся только одноразрядные слова), при этом каждая микросхема ОЗУ состоит из матрицы элементов памяти, адресные шины которой подключены к адресным шинам микросхемы ОЗУ через дешифратор адреса, информационные шины устройства соединены через один элемент И с вьпсодными информационными шинами, а через другой элемент И с выходными информационными шинами микросхемы ОЗУ, управляющие входы элементов И соединены через блок управления с управляющими шинами мйкро схемы ОЗУ, Входы дешифраторов адреса всех микросхем ОЗУ подключены параллельнок вькодам регистраадреса, входы которого подключены к адресным входам запоминающего устройства. Входы блоков управления всех микросхем ОЗУ связаны с управляющими входами запоминающего устройства. Информационные

входы запоминающего устройства подключены ко входам элементов И соответствующих микросхем ОЗУ, а информалдионные вьтходы запоминающего устройства связаны со входами элементов И соответствующих) микросхем ОЗУГЗ

Недостатком этого устройства HBnfletся то, что в многопрограммных ЦВМ универсального типа и в ОЗУ одновреме{-гно размещается несколько рабочих программ/которые выполняются в прикятой последоватепьности. В этом -случае ошибка при формировании адреса приводит к считыванию или записи и информацин в

ОЗУ по этому ошибочному адресу, который может принадлежать даже другой, не выполняемой, программе, -что приводит к искажению предлагаемой информации и к снижению надежности работы запоми нающего устройства.

Цель изобретения - повышение надежности работы запошшающего устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содер жащее регистр адреса, подключенный через дешифраторы к матричным накопн телям, выходы которых подключены че рез элементы И к информационным вхо-дам и выходам устройства, и блоки управ , ления, введены дополнительный элемент И, коммутатор, элементы ИЛИ и дополнительный дешифратор, входы которого соединеЕШ с выходами регистра адреса, а выходы через соответствующие эле-

менты ИЛ1 - с входами коммутатора, выход которого подк.лючен к одному из входов дополнительного элемента И, дру гой вход доподнительного элемента И подключен к шине записиц а выход к соответствующим входам блоков управле™

НИЯо

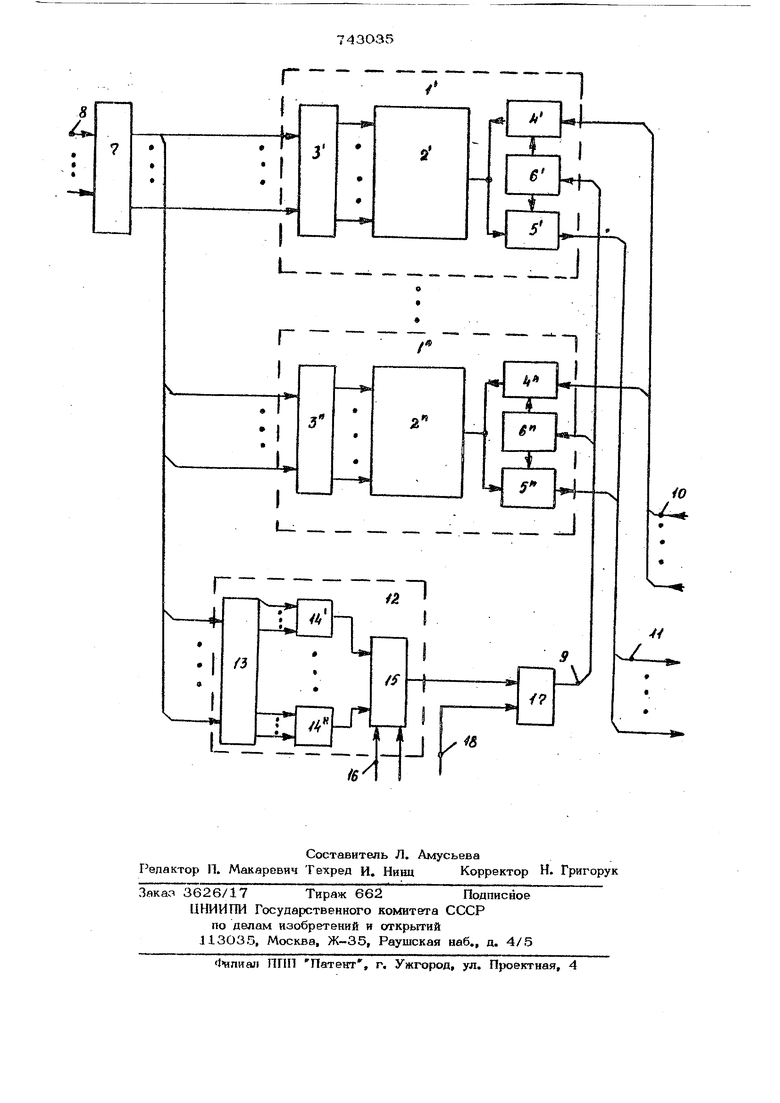

На чертеже представлена блок-схема устройства.

Устройство содержит микросхемы

1 ОЗУ (где гь - разрядность слов, выбираемых из запоминающего устройства, причем предполагается, что в каждой микросхеме ОЗУ. .хранятся только одноразрядные слова), каждая микросхема 1 ОЗУ состоит из матричного на.копителя 2, адресные щины которого подключены к адресным аганам микросхемы 1 ОЗУ через дешифратор 3 адреса, информадионные шины устройства 2 соединены через элемент 4 И с в.ходными информационными щинами, а через элемент 5 И с выходными информационными шинами микросхемы 1 ОЗУу управляющие входы

элементов 4 и 5 И соединены через блок 6 управления с управляющими шинами микросхемы 1 ОЗУ. Входы дешифраторов 3 адреса всех микросхем 1 03J подключены параллельно к .выходам регистра 7 адреса, в.ходы которого под1тючены к адресным входам 8 запоминающего устройства. Входы блоков б управления всех микросхем 1 ОЗУ соединены с управляющим входом 9. Информационные входы 10 запоминающего устройства подключены ко входам элементов 4 И соответствующих микросхем 1 ОЗУ, а информационные выходы Л. 1 запоминающего устройства соединены со входами Элементов 5 И соответствующи.х микросхем 1 ОЗУ. Селектор 12 адресов состоит из дешифратора 13, выходы которого соединены через К многов.ходовых элементов 14 ИЛИ с соответствующими в.ходами коммутатора 15 (где К - количество используемых программ в ОЗУ). При этом управляющие в.хо.ды 16 коммутатора 15 соединены с внешним устройством управления, а-выход коммутатора 15 подключен ко входу элемента 17 И, другой вход 18 которой также соединен с вийшним устройством управления, а вы.ход элемента 17 И подключен ко входу 9. Входы дешифратора 13 подключены к выходам регистра 7 адреса.

Устройство работает следующим образом.

Перед началом работы на один из входов 16 подается .напряжение из внешнего устройства управления. При этом к выходу селектора 12 адресов подключается только один из мвогов.ходовых элементов 14 ИЛИ, обеспечивающий выборку адресов только для заданной программы и обеспечивающий блокировку выборки адресов из други.х, не заданных, программ, записанных в матрицы элементов 2 памяти микросхем 1 ОЗУ. Далее, при поступлении сигналов записи на входы 18 запоминающего устройства и приема кода адреса со в.ходов 8 в регистр 7 адреса осуществляется запись информации, поступающей со входов 10, по одному и тому же разрешенному адресу во все П. микросхем 1 ОЗУ, причем каждый в.ход 10 соединен со вхо дом элемента 4 И только одной микрос-хемы 1 ОЗУ. При поступлении сигналов считьшания на входы 18 запоминающего устройства и приема кода адреса со в.ходом 8 в регистр 7 адреса осуществляется считывание информации по одному и тому же разрешенному адресу во всах И/-микросхемах 1 ОЗУ. На вькоде каждой микросхемы 1 ОЗУ появится выход ной информационный сигнал, совокупнос таких сигналов, появляющихся на выхо дах 10 запоминающего устройства соот ветствует одному разрядному слову, запоминающего устройства. Запоминающее устройство, в отличие от известного позволяет повысить наде ность работы его за счет: исключения возможности ошибочных обращений к не заданным программам, записанным в матричньк накопителях микросхем ОЗУ исключения возможности искажения информации, записанной в матричных на копителях Микросхем O3yj обеспечения возможности обходить неисправные ячейки памяти как ;;в процессе эксплуатации, так и при изготовлении запоминающего устройства. Формула зобретени Запоминающее устройство, содерж&щее регистр адреса, подключенный ч&рез дешифраторы к матричным накопите лям, выходы которых подключены через 56 элементы И к информационным аходам и выходам устройства, и блоки управления, подключенные к элементам И, отличающееся тем, что, с целью повышения надежности устройства, оно. содержит дополнительный элемент И, коммутатор, элементы ИЛИ и дополнительный дешифратор, входы которого соединены с выходами регистра адреса, а. выходы через соответствующие элементы ИЛИ - с входами коммутатора, выход которого подключен к одному из В.ХОДОВ дополнительного элемента И, другой вход дополнительного элемента И подключен к щине записи, а выход к соответствующим входам блоков управления. Источники информации, принятые во внимание при экспертизе 1. Старов Ф. Г, и др. Полупроводний:Ьвые интегральные запоминающие устройства fЭнергия, Ленинградское отделение, 1973, с. 62-77, рис. 4-3,45,4-6 и 4-10. 2.Преснухин Л, Н, и др. Цифровые вычислительные машины, М., Высшая школа , 1974, с. 214-216, рис. 4.51. 3.Преснухин Л. И, и др. Цифровые ычислительные машины. М., Высшая кола, 1974, рис. 4.51 а (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство оперативной связи с управляющими программами | 1981 |

|

SU970351A1 |

| Устройство для контроля полупроводниковой памяти | 1981 |

|

SU945904A1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Запоминающее устройство с многоформатным доступом к данным | 1983 |

|

SU1108507A1 |

| Многоканальное устройство для сопряжения двух ЭВМ | 1985 |

|

SU1312585A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1993 |

|

RU2069018C1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Микропрограммное устройство управления | 1981 |

|

SU995091A1 |

| Устройство записи-воспроизведения многоканальной цифровой информации на магнитный носитель | 1991 |

|

SU1777176A1 |

Авторы

Даты

1980-06-25—Публикация

1978-03-31—Подача