Изобретение относится к запоминающим устройствам.

Известно устройство для контроля полупроводниковой памяти, которое содержит блоки сопряжения, блок управления , генераторы импульсов и блок формирования временной диаграммы tl.

Недостатком этого устройства является низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля полупроводниковой памяти, содержащее блок управления, блок формирования данных и блок формирования адреса, состоящий из регистра текущего адреса, вспомогательного регистра,, регистра начального адреса, регистра конечного адреса и устройства для сравнения адресов С23.

Недостатком этого устройства является низкое быстродействие, т.е. для изменения значений начального и конечного адресов проверяемого массива требуется дополнительное время для перепрограммирования.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для контроля полупроводниковой памяти, содержащее блок управления, входы и один из выходов которого подключены соответ10ственно к одним из выходов и входов первого и второго блоков сопряжения, блока формирования данных и первого блока формирования адреса, введены второй блок формирования адреса и коммутаторы, один из входов

15 которых соединены с одними из выходов второго блока формирования адреса, один из входов которого подключены к другим выходам первого блока

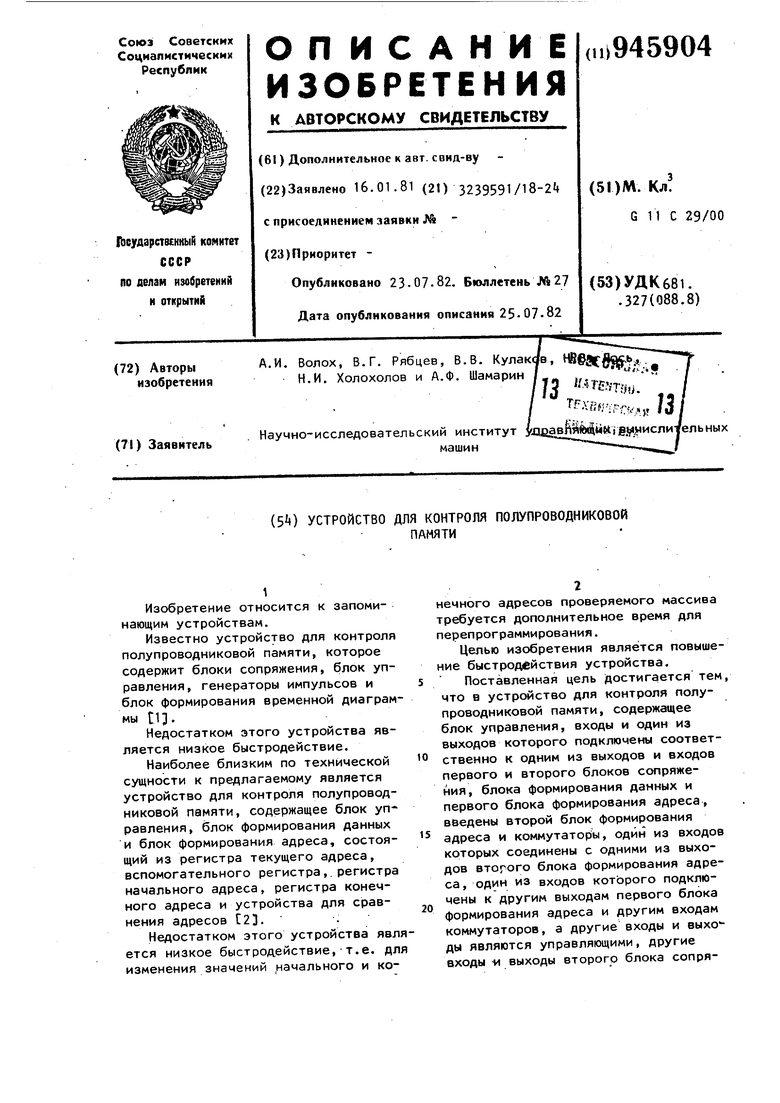

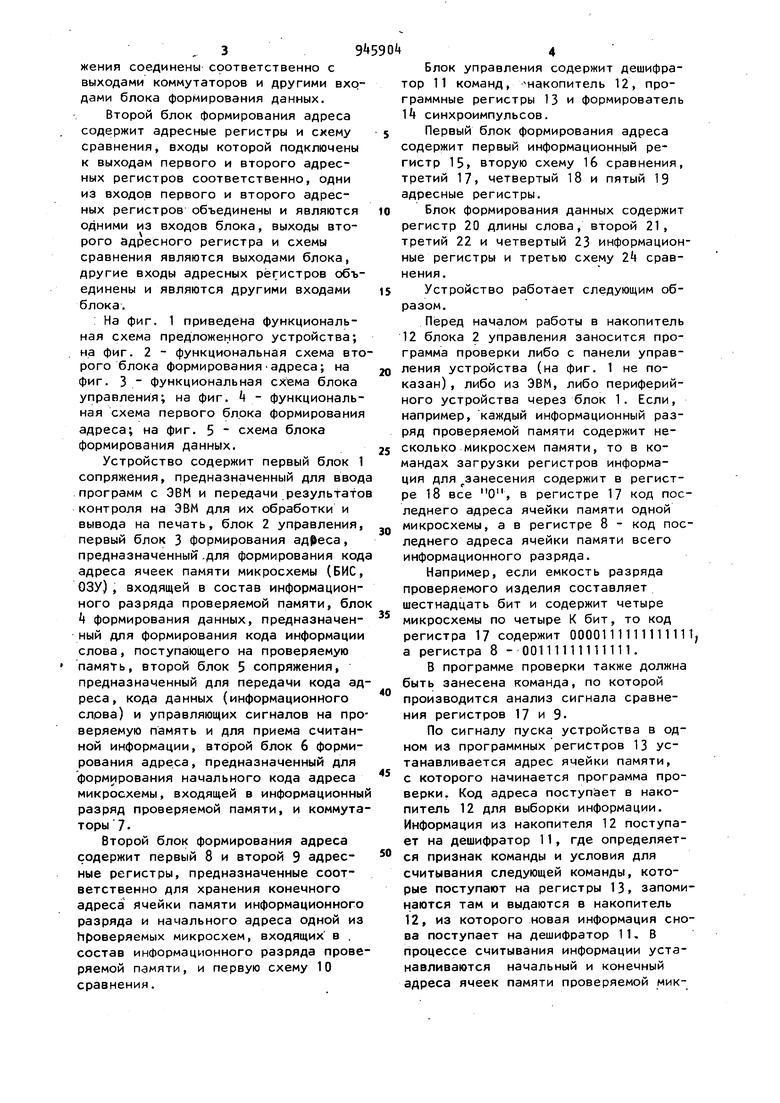

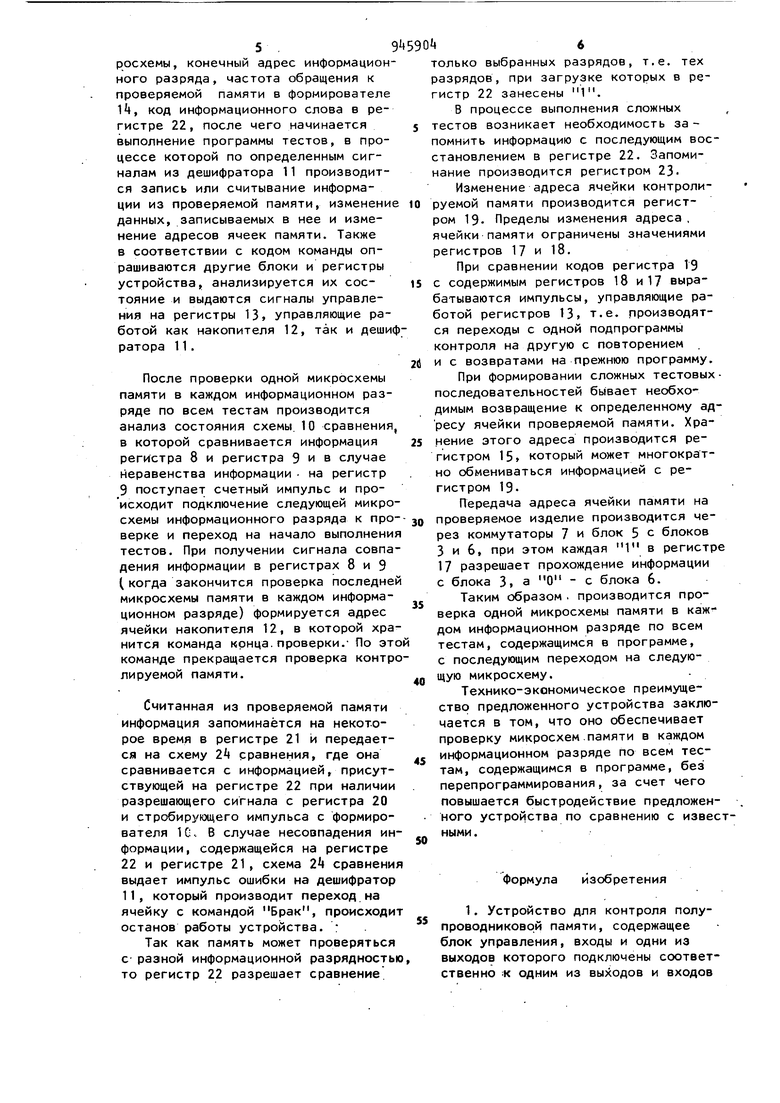

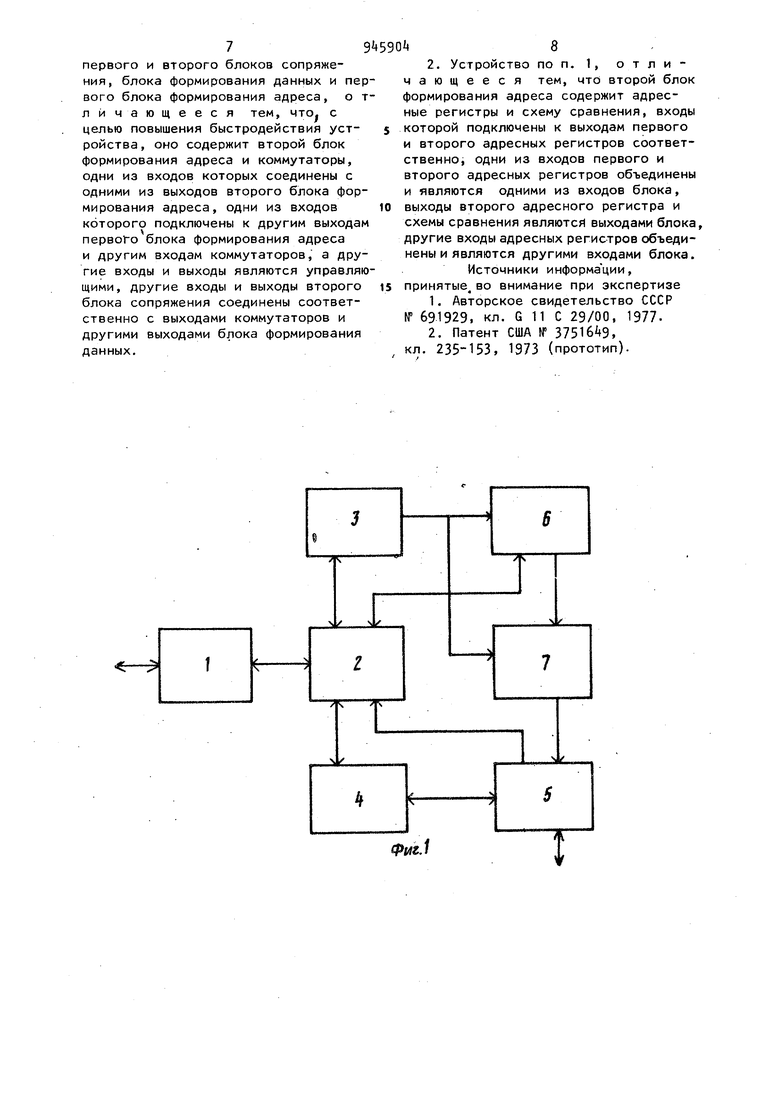

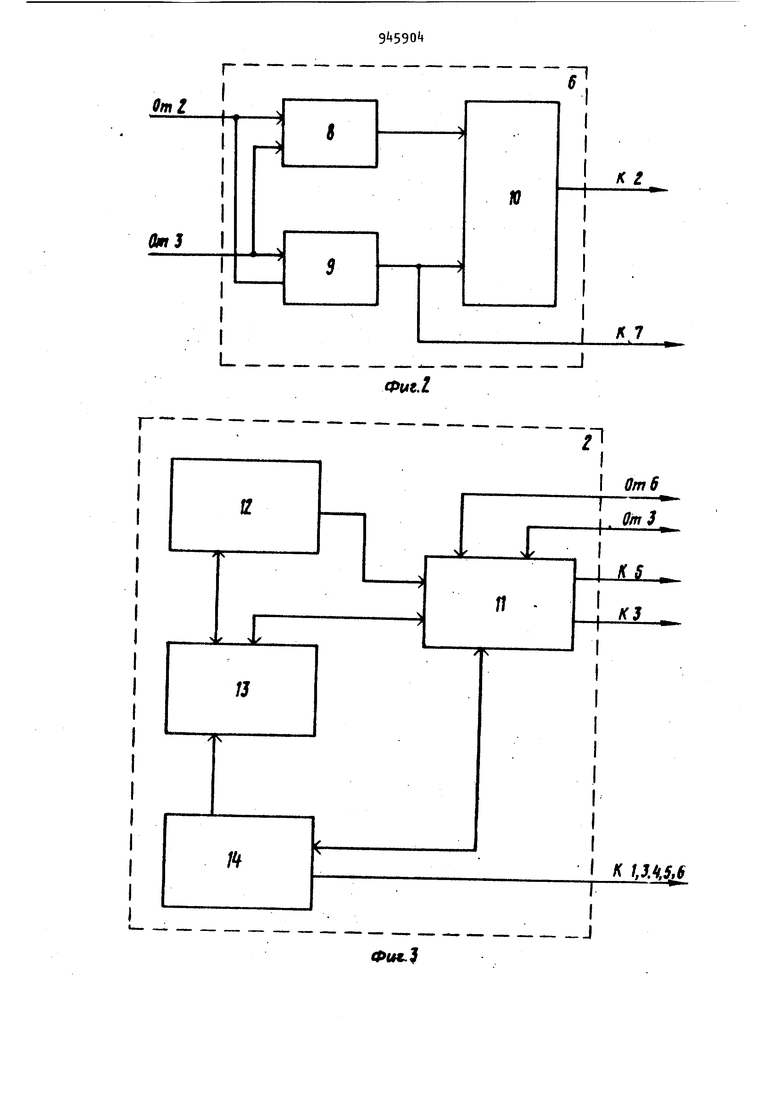

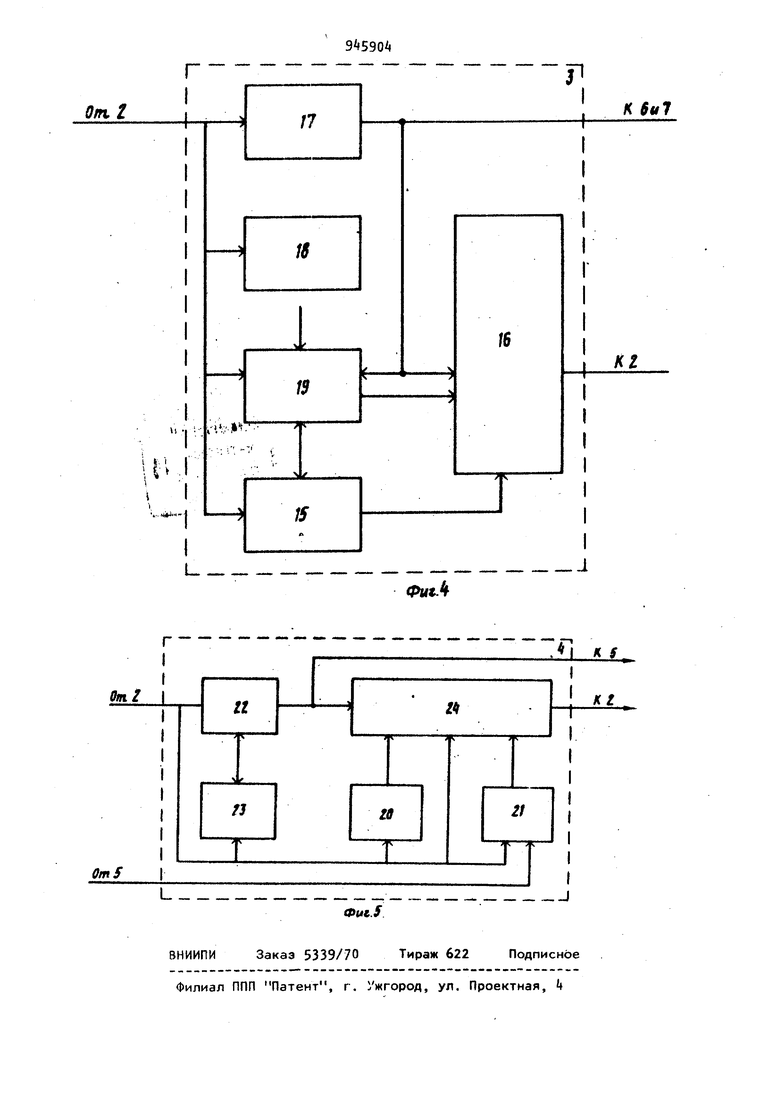

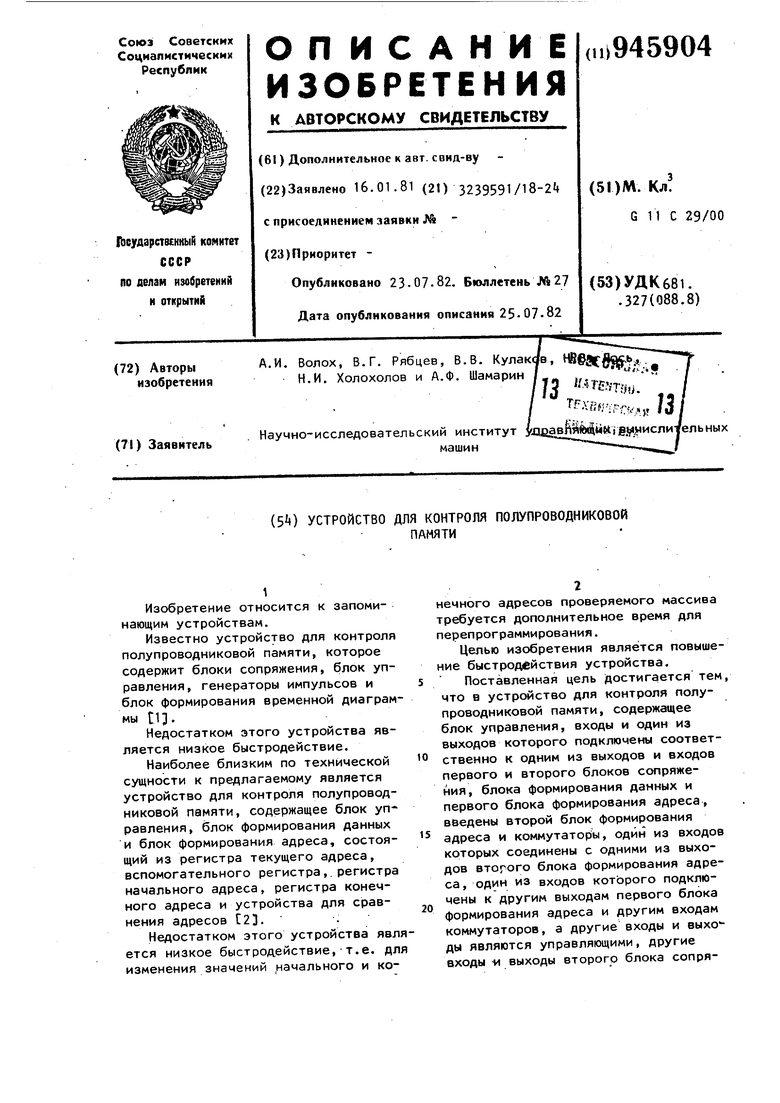

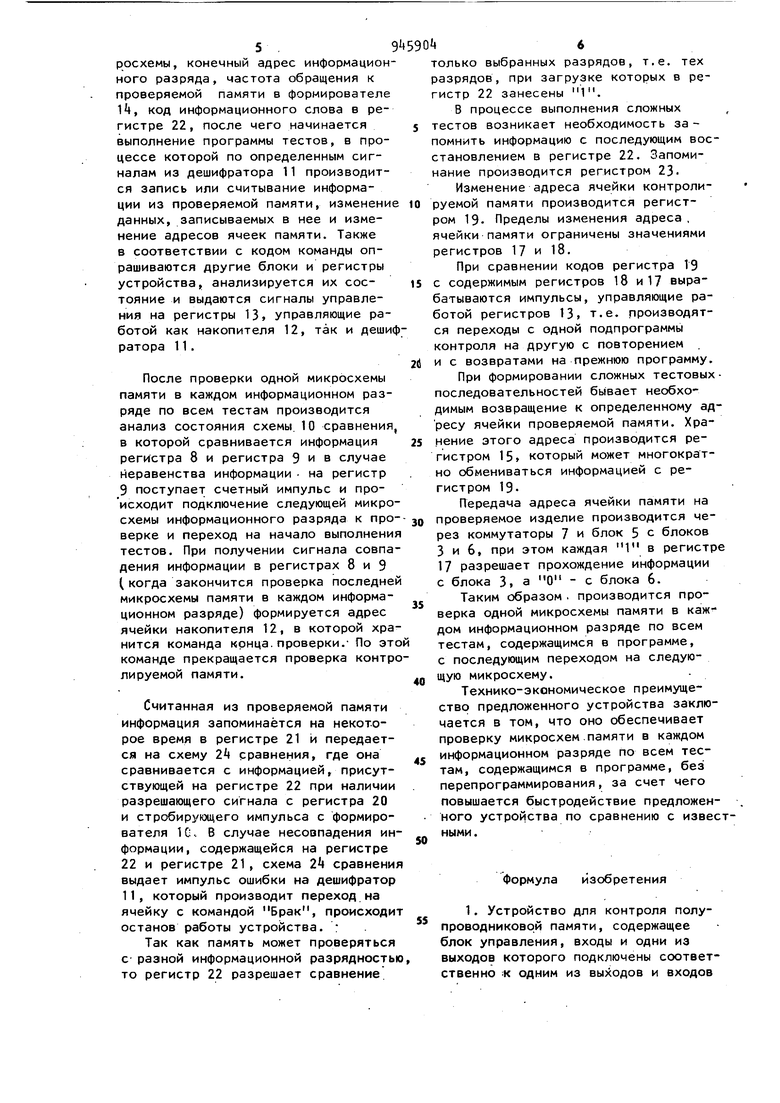

20 формирования адреса и другим входам коммутаторов, а другие входы и выхо ды являются управляющими, другие входы и выходы второго блока сопря.39 жения соединены соответственно с выходами коммутаторов и другими входами блока формирования данных. Второй блок формирования адреса содержит адресные регистры и схему сравнения, входы которой подключены к выходам первого и второго адресных регистров соответственно, одни из входов первого и второго адресных регистров объединены и являются одними из входов блока, выходы второго адресного регистра и схемы сравнения являются выходами блока, другие входы адресных регистров объединены и являются другими входами блока, На фиг, 1 приведена функциональная схема предложенного устройства; на фиг. 2 - функциональная схема вто рого блока формированияадреса; на фиг. 3 функциональная схема блока управления; на фиг. Ц - функциональная схема первого блока формирования адреса; на фиг. 5 схема блока формирования данных, Устройство содержит первый блок 1 сопряжения, предназначенный для ввод программ с ЭВМ и передачи результато контроля на ЭВМ для их обработки и вывода на печать, блок 2 управления, первый блок 3 формирования адреса, предназначенный .для формирования код адреса ячеек памяти микросхемы (БИС, ОЗУ), входящей в состав информационного разряда проверяемой памяти, бло k формирования данных, предназначенный для формирования кода информации слова, поступающего на проверяемую память, второй блок 5 сопряжения, предназначенный для передачи кода ад реса, кода данных (информационного слрва) и управляющих сигналов на про веряемую память и для приема считанной информации, второй блок 6 формирования адреса, предназначенный для формирования начального кода адреса микросхемы, входящей в информационны разряд проверяемой памяти, и коммута торы 7второй блок формирования адреса содержит первый 8 и второй 9 адресные регистры, предназначенные соответственно для хранения конечного адреса ячейки памяти информационного разряда и начального адреса одной из Проверяемых микросхем, входящих в . состав информационного разряда прове ряемой памяти, и первую схему 10 сравнения. Блок управления содержит дешифратор 11 команд, накопитель 12, программные регистры 13 и формирователь 1 синхроимпульсов. Первый блок формирования адреса содержит первый информационный регистр 15 вторую схему 16 сравнения, третий 17, четвертый 18 и пятый 19 адресные регистры. Блок формирования данных содержит регистр 20 длины слова, второй 21, третий 22 и четвертый 23 информационные регистры и третью схему сравнения. Устройство работает следующим образом. Перед началом работы в накопитель 12 блока 2 управления заносится программа проверки либо с панели управления устройства (на фиг. 1 не показан) , либо из ЭВМ, либо периферийного устройства через блок 1. Если, например, каждый информационный разряд проверяемой памяти содержит несколько микросхем памяти, то в командах загрузки регистров информация для занесения содержит в регистре 18 все О, в регистре 17 код последнего адреса ячейки памяти одной микросхемы, а в регистре 8 - код последнего адреса ячейки памяти всего информационного разряда. Например, если емкость разряда проверяемого изделия составляет шестнадцать бит и содержит четыре микросхемы по четыре К бит, то код регистра 17 содержит 0000111111111111, а регистра 8 -00111111111111. В программе проверки также должна быть занесена команда, по которой производится анализ сигнала сравнения регистров 17 и 9По сигналу пуска устройства в одном из программных регистров 13 устанавливается адрес ячейки памяти, с которого начинается программа проверки. Код адреса поступает в накопитель 12 для выборки информации. Информация из накопителя 12 поступает на дешифратор 11, где определяется признак команды и условия для считывания следующей команды, которые поступают на регистры 13, запоминаются там и выдаются в накопитель 12, из которого новая информация снова поступает на дешифратор 11. В процессе считывания информации устанавливаются начальный и конечный адреса ячеек памяти проверяемой микросхемы, конечный адрес информацион ного разряда, частота обращения к проверяемой памяти в формирователе Ш, код информационного слова в регистре 22, после чего начинается выполнение программы тестов, в процессе которой по определенным сигналам из дешифратора 11 производится запись или считывание информации из проверяемой памяти, изменени данных, записываемых в нее и изменение адресов ячеек памяти. Также в соответствии с кодом команды опрашиваются другие блоки и регистры устройства, анализируется их состояние и выдаются сигналы управления на регистры 13, управляющие работой как накопителя 12, так и деши ратора 11 . После проверки одной микросхемы памяти в каждом информационном разряде по всем тестам производится анализ состояния схемы. 10 сравнения в которой сравнивается информация регистра 8 и регистра 9 и в случае неравенства информации на регистр 9 поступает счетный импульс и происходит подключение следующей микро схемы информационного разряда к про верке и переход на начало выполнени тестов. При получении сигнала совпа дения информации в регистрах 8 и 9 (когда закончится проверка последне микросхемы памяти в каждом информационном разряде) формируется адрес ячейки накопителя 12, в которой хра нится команда конца, проверки.- По эт команде прекращается проверка контр лируемой памяти. Считанная из проверяемой памяти информация запоминается на некоторое время в регистре 21 и передается на схему 2k сравнения, где она сравнивается с информацией, присутствующей на регистре 22 при наличии разрешающего сигнала с регистра 20 и стробирующего импульса с формирователя 1G., В случае несовпадения ин формации, содержащейся на регистре 22 и регистре 21, схема 2 сравнени выдает импульс ошибки на дешифратор 11, который производит переход на ячейку с командой Брак, происходи останов работы устройства. : Так как память может проверяться с разной информационной разрядность то регистр 22 разрешает сравнение только выбранных разрядов, т.е. тех разрядов, при загрузке которых в регистр 22 занесены 1. В процессе выполнения сложных тестов возникает необходимость за помнить информацию с последующим восстановлением в регистре 22. Запоминание производится регистром 23Изменение адреса ячейки контролируемой памяти производится регистром 19- Пределы изменения адреса , ячейки памяти ограничены значениями регистров 17 и 18. При сравнении кодов регистра 19 с содержимым регистров 18 и 17 вырабатываются импульсы, управляющие работой регистров 13 т.е. производятся переходы с одной подпрограммы контроля на другую с повторением и с возвратами на прежнюю программу. При формировании сложных тестовых последовательностей бывает необходимым возвращение к определенному адресу ячейки проверяемой памяти. Хранение этого адреса производится регистром 15 который может многократно обмениваться информацией с регистром 19. Передача адреса ячейки памяти на проверяемое изделие производится через коммутаторы 7 и блок 5 с блоков 3 и 6, при этом каждая 1 в регистре 17 разрешает прохождение информации с блока 3. а О - с блока 6. Таким образом , производится проверка одной микросхемы памяти в каж дом информационном разряде по всем тестам, содержащимся в программе, с последующим переходом на следующую микросхему. Технико-экономическое преимущество предложенного устройства заключается в том, что оно обеспечивает проверку микросхем.памяти в каждом информационном разряде по всем тестам, содержащимся в программе, без перепрограммирования, за счет чего повышается быстродействие предложенного устройства по сравнению с известными. Формула изобретения 1. Устройство для контроля полупроводниковой памяти, содержащее блок управления, входы и одни из выходов которого подключены соответственно к одним из выходов и входов

первого и второго блоков сопряжения, блока формирования данных и первого блока формирования адреса, о тл и чающееся тем, что. с целью повышения быстродействия устройства , оно содержит второй блок формирования адреса и коммутаторы, одни из входов которых соединены с одними из выходов второго блока формирования адреса, одни из входов которого подключены к другим выходам первого блока формирования адреса и другим входам коммутаторов, а другие входы и выходы являются управляющими, другие входы и выходы второго блока сопряжения соединены соответственно с выходами коммутаторов и другими выходами блока формирования данных.

2. Устройство по п. 1, отличающееся тем, что второй блок формирования адреса содержит адресные регистры и схему сравнения, входы

которой подключены к выходам первого и второго адресных регистров соответственно, одни из входов первого и второго адресных регистров объединены и являются одними из входов блока,

выходы второго адресного регистра и схемы сравнения являются1 выходами блока, другие входы адресных регистров объединены и являются другими входами блока. Источники информации,

принятые во внимание при экспертизе

1,Авторское свидетельство СССР № 691929. кл. G 11 С 29/00, 19772.Патент США № 3751649,

кл. 235-153, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для контроля блоков постоянной памяти | 1991 |

|

SU1830548A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Устройство для программного управления | 1990 |

|

SU1716482A1 |

| Устройство сопряжения процессора с памятью | 1986 |

|

SU1322296A1 |

| Устройство для контроля больших интегральных схем памяти | 1984 |

|

SU1179375A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство для контроля программ | 1983 |

|

SU1136172A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

Фиг.1

0Vt.l

Фиг.

L

I

ФигЛ

Авторы

Даты

1982-07-23—Публикация

1981-01-16—Подача