Изобретение относится к вычислительной технике и может найти примененге в вычислительных системах для сопряжения дву.х ЭВМ с различным представлением данных.

Целью изобретения является расширение области применения путем обеспечения обмена информацией между ЭВМ по носледова- ге,:;,:.п,1м и параллельным каналам Е водаBI)MU),;:.

При этом повышается быстродействие устройства за счет сокращения времени преобразования при формировании последовательных кодов для каналов ввода-вывода.

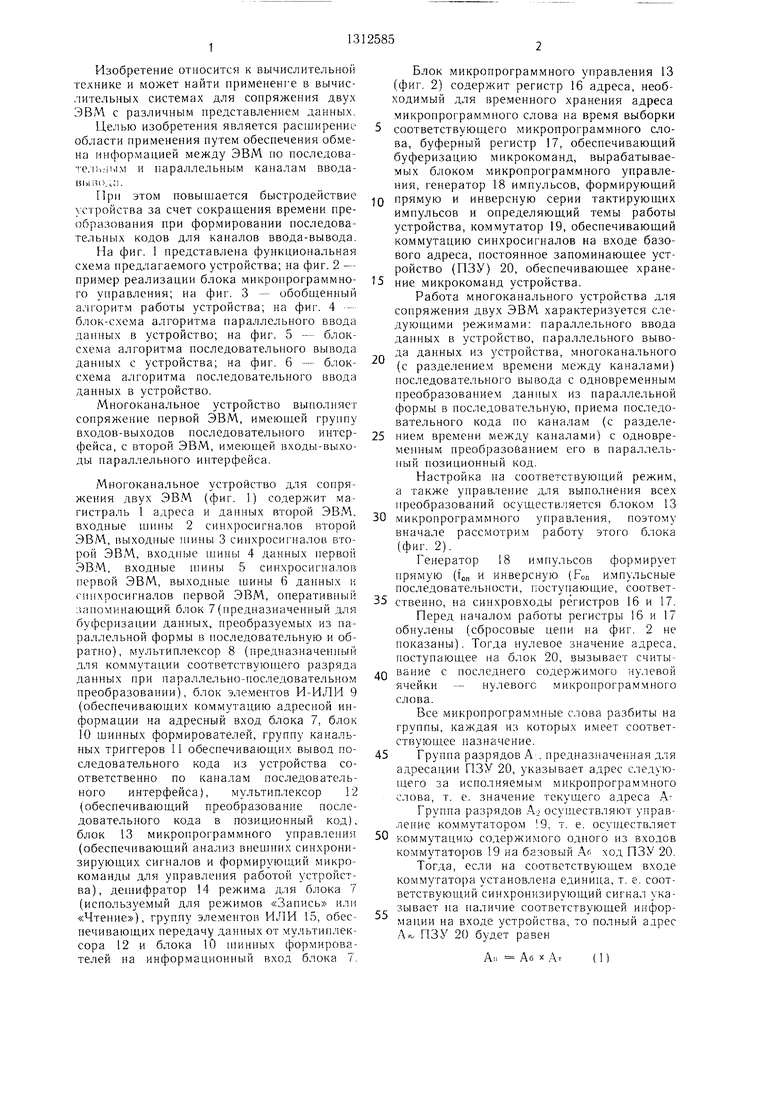

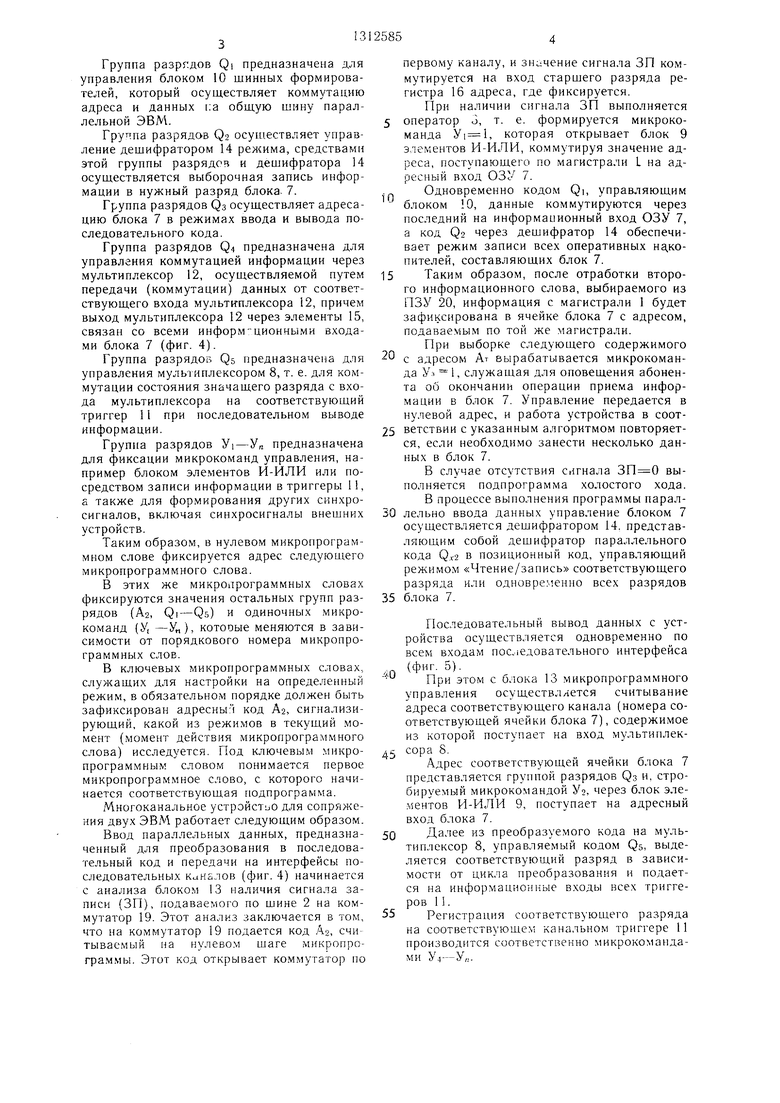

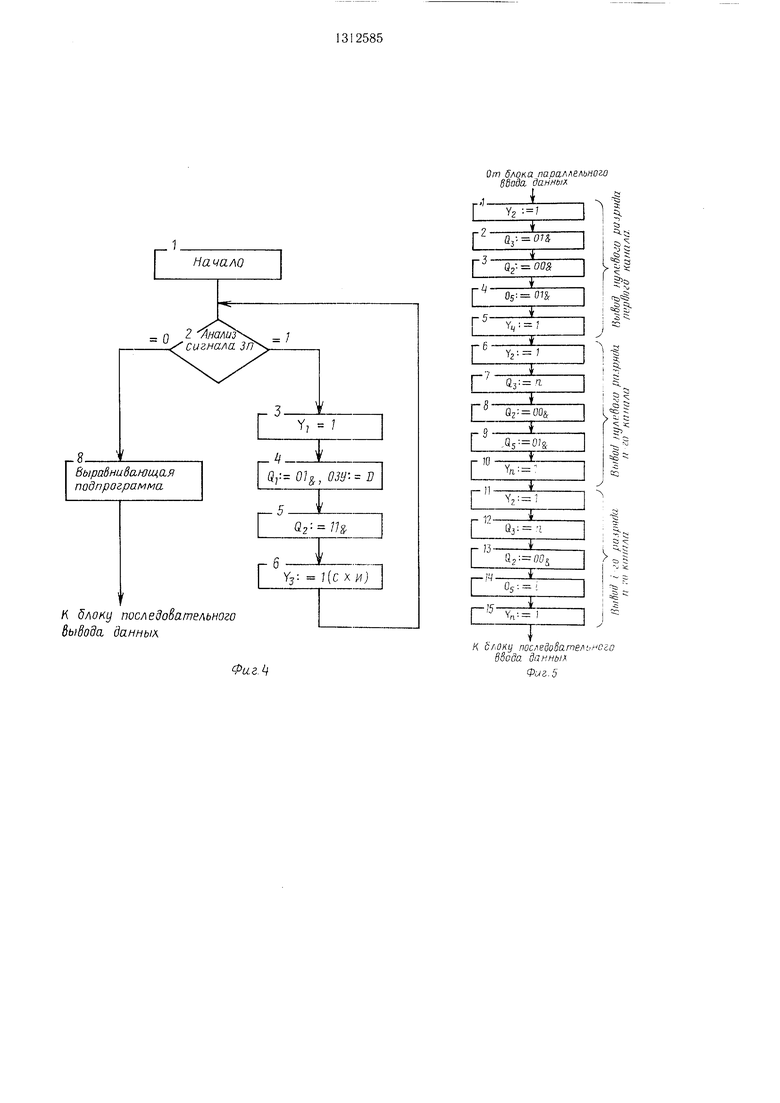

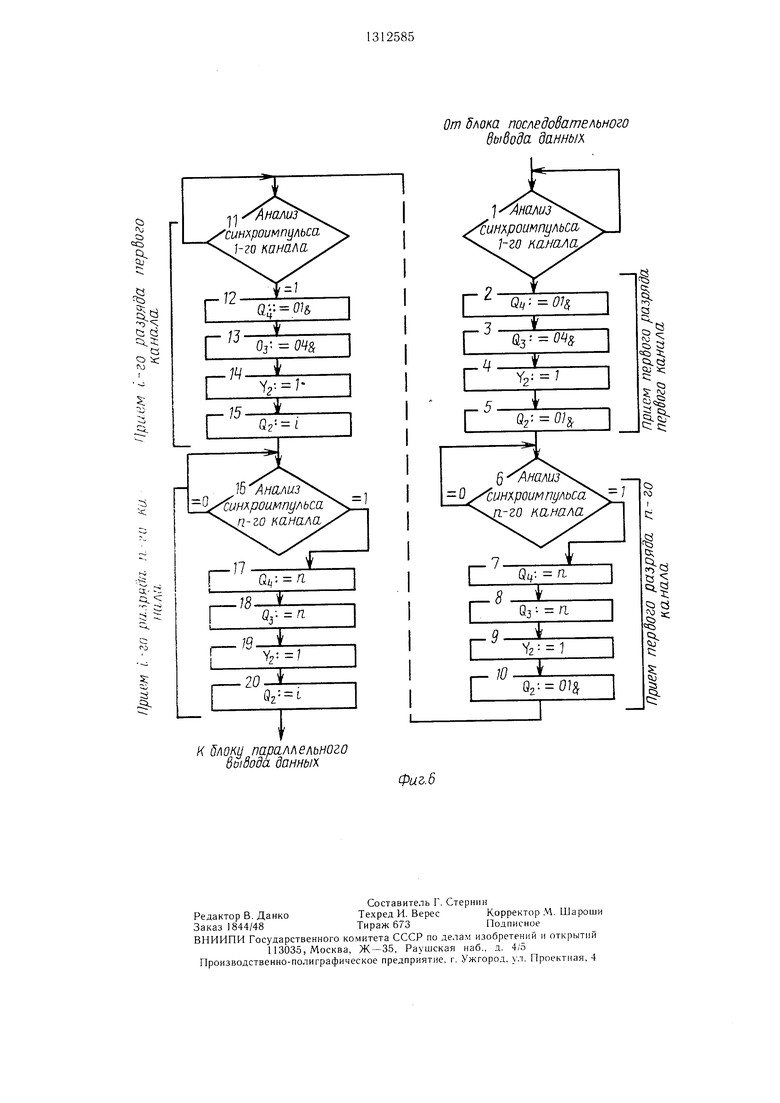

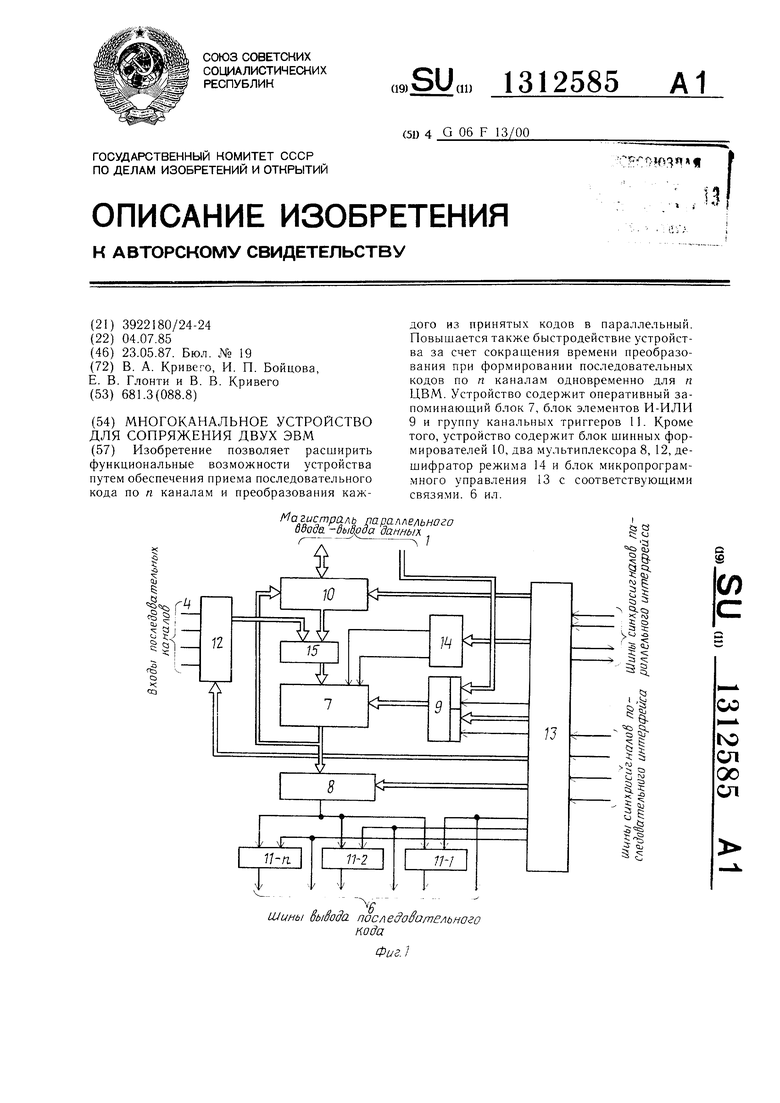

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - пример реализации блока микропрограммного управления; на фиг. 3 - обобнденный а„ и 0ритм работы устройства; на фиг. 4 - блок-схема алгоритма параллельного ввода данных в устройство; на фиг. 5 - блок- схема алгоритма последовательного вывода данных с устройства; на фиг. б - блок- схема алгоритма последовательного ввода данных в устройство.

Д1ногоканальное устройство выполняет сопрян енпе первой ЭВМ, имеюнлей группу входов-выходов последовательного интерфейса, с второй ЭВМ, имеющей входы-выходы параллельного интерфейса.

Многоканальное устройство для сопряжения двух ЭВМ (фиг. 1) содержит магистраль 1 адреса и данных второй ЭВМ. входные 1НПНЫ 2 синхросигналов второй ЭВМ, выходные Н1ины 3 синхросигналов второй ЭВМ, входные 1пины 4 данных nepBoii ЭВМ, входные п.1ины 5 синхросигналов первой ЭВМ, выходные шины 6 данных и синхросигналов первой ЭВМ, оперативный запоминающий блок /(предназначенный для буферизации данных, преобразуемых из параллельной формы в последовательную и обратно), мультиплексор 8 (предназначенный для коммутации соответствуюнлего разряда данных при параллельно-последовательном преобразовании), блок элементов И-ИЛИ 9 (обеспечивающих коммутацию адрес}шй ин- фор.мации на адресный вход блока 7. блок 10 щинных формирователей, группу канальных триггеров 11 обеспечивавощих вывод последовательного кода из устройства соответственно по каналам последовательного интерфейса), мультиплексор 12 (обеспечивающий преобразование последовательного кода в позиционный код), блок 13 микропрограммного управления (обеспечивающий анализ внешних синхронизирующих сигналов и формирующий микрокоманды для управления работой устройства), дещифратор 14 режима д.тя блока 7 (используемый для режимов «Запись или «Чтение), группу элементов ИЛИ 15, обеспечивающих передачу данных от мультиплексора 12 и блока 10 Н1ИННЫХ формирователей на информационный вход блока 7.

0

Блок микропрограммного управления 13 (фиг. 2) содержит регистр 16 адреса, необходимый для временного хранения адреса микропрограммного слова на время выборки соответствуюп 1его микропрограммного слова, буферный регистр 17, обеспечивающий буферизацию микрокоманд, вырабатываемых блоком микропрограммного управления, генератор 18 импульсов, формирующий 0 прямую и инверсную серии тактирующих импульсов и определяющий темы работы устройства, коммутатор 19, обеспечивающий коммутацию синхросигналов на входе базового адреса, постоянное запоминающее устройство (ПЗУ) 20, обеспечивающее хране- 5 ние микрокоманд устройства.

Работа многоканального устройства для сопряжения двух ЭВМ характеризуется следующими режимами: параллельного ввода данных в устройство, параллельного вывода данных из устройства, многоканального (с разделением времени между каналами) последовательного вывода с одновременным преобразованием данных из параллельной формы в последовательную, приема последовательного кода по каналам (с разделе- 5 нием времени между каналами) с одновременным преобразованием его в параллельный позиционный код.

Настройка на соответствующий режим, а также управление для выполнения всех преобразований осуществ.чяется блоком 13 0 микропрограммного управления, поэтому вначале рассмотрим работу этого блока (фиг. 2).

Генератор 18 импульсов формирует

прямую (ton и инверсную (Fon импульсные

последовательности, поступающие, соответ5 ственно, на синхровходы регистров 16 и 17.

Неред началом работы регистры 16 и 17 обнулены (сбросовые цени на фиг. 2 не показаны). Тогда нулевое значение адреса, поступающее на блок 20, вызывает считы- д вание с последнего содержимого нулевой ячейки - нулевого микропрограммного слова.

Все микропрограммные слова разбиты на группы, каждая из которых имеет соответствующее назначение.

5 Группа разрядов А . предназначенная для адресации ПЗУ 20, указывает адрес следую- ндего за исполняемым микропрограммного слова, т. е. значение текущего адреса АГруппа разрядов Aj осупгествляют управление коммутатором 19, т. е. осунхествляет

0

коммутацию содержимого одрюго из входов

коммутаторов 19 на базовый .f ход ПЗУ 20. Тогда, если на соответствующем входе коммутатора установлена единица, т. е. соответствующий синхронизирующий сигнал указывает па наличие соответствующей информации на входе устройства, то полный адрес ПЗУ 20 будет равен

Ап Аб X AT

(1)

Группа разрг.дов Qi предназначена для управления блоком 10 шинных формирователей, который осуществляет коммутацию адреса и данных ка общую шину параллельной ЭВМ.

Группа разрядов Q2 осуществляет управление дешифратором 14 режима, средствами этой группы разрядов и дешифратора 14 осуществляется выборочная запись информации в нужный разряд блока. 7.

Группа разрядов Qa осуществляет адресацию блока 7 в режимах ввода и вывода последовательного кода.

Группа разрядов Q4 предназначена для управления коммутацией информации через мультиплексор 12, осуществляемой путем передачи (коммутации) данных от соответствующего входа мульти-плексора 12, причем выход мультиплексора 12 через элементы 15, связан со всеми информ ционными входами блока 7 (фиг. 4).

Группа разрядов Qs предназначена для управления мулыиплексором 8, т. е. для коммутации состояния значащего разряда с входа мультиплексора на соответствующий триггер 11 при последовательном выводе информации.

Группа разрядов предназначена для фиксации микрокоманд управлени-я, например блоком элементов И-ИЛИ или посредством записи информации в триггеры 1, а также для формирования других синхросигналов, включая синхросигналы внешних устройств.

Таким образом, в нулевом микропрограммном слове фиксируется адрес следующего микропрограммного слова.

В этих же микропрограммных словах фиксируются значения остальных групп разрядов (А2, QI-Q.5) и одиночных микрокоманд (У, -У„), KOTODbie меняются в зависимости от порядкового номера микропрограммных слов.

В ключевых микропрограммных словах, служащих для настройки на определенный режим, в обязательном порядке должен быть зафиксирован адресный код А2, сигнализирующий, какой из режимов в текущий момент (момент действия микропрограммного слова) исследуется. Под ключевы.м микропрограммным словом понимается первое микропрограммное слово, с которого начинается соответствующая подпрограмма.

Многоканальное устройство для сопряжения двух ЭВМ работает следующим образом.

Ввод параллельных данных, предназначенный для преобразования в последовательный код и передачи на интерфейсы последовательных Каналов (фиг. 4) начинается с анализа блоком 13 наличия сигнала записи (ЗП), подаваемого по шине 2 на коммутатор 19. Этот анализ заключается в том, что на коммутатор 19 подается код ., счи тываемый на нулевом шаге гущкропро- граммы. Этот код открывает коммутатор по

первому каналу, и зн ;чение сигнала ЗП коммутируется на вход старшего разряда регистра 16 адреса, где фиксируется.

Г1ри наличии сигнала ЗП выполняется

оператор о, т. е. формируется микрокоманда У , которая открывает блок 9 элементов И-ИЛИ, коммутируя значение адреса, поступающего по магистрали L на адресный вход ОЗУ 7.

Одновременно кодом Qi, управляющим блоком 0, данные коммутируются через последний на информапионный вход ОЗУ 7, а код Qo через дешифратор 14 обеспечивает режим записи всех оперативных на,ко- пителей, составляющих блок 7.

5 Таким образом, после отработки второго информационного слова, выбираемого из ПЗУ 20, информация с магистрали 1 будет зафиксирована в ячейке блока 7 с адресом, подаваемым по той же магистрали.

При выборке следующего содержимого

0 с адресом Ат вырабатывается микрокоманда УЗ - 1, служащая для оповещения абонента об окончании операции приема информации в блок 7. Управление передается в нулевой адрес, и работа устройства в соот5 ветствии с указанным алгоритмом повторяется, если необходимо занести несколько данных в блок 7.

В случае отсутствия сигнала выполняется подпрограмма холостого хода. В процессе выполнения программы парал0 лельно ввода данных управление блоком 7 осуществляется дешифратором 14. представляющим собой дешифратор параллельного кода Qx2 в позиционный код, управляющий режимом «Чтение/запись соответствующего разряда или одновременно всех разрядов

5 блока 7.

Последовательный вывод данных с устройства осуществляется одновременно по всем входам последовательного интерфейса

„ (фиг. 5).

При этом с блока 13 микропрограммного управления осуществляется считывание адреса соответствующего канала (номера соответствующей ячейки блока 7), содержимое из которой поступает на вход мультиплек5 сора 8.

Адрес соответствующей ячейки блока 7 представляется группой разрядов Qs и, стро- бируемый микрокомандой Уз, через блок эле- .ментов И-ИЛИ 9, поступает на адресный вход блока 7.

0 Далее из преобразуемого кода на мультиплексор 8, управляемый кодом Qs, выделяется соответствующий разряд в зависимости от цикла преобразования и подается на информационные входы всех триггеров 11.

5 Регистрация соответствующего разряда на соответствующем канальном триггере 11 производится соответственно микрокомандами У 4У„.

При -п ом сама микрокоманда является синхроимпульсом, оповещающим о наличии соответствующей информации по соответст- BvioHieMv каналу.

Таким оброзом, устройство осуществляет преобразование параллельной информации, заносимой 8 блок 7 на этапе нараллель- ного ее ввода, в последовательный код одно- иремснно но каналам последовательного интерфейса за заданное число циклов.

При этом на каждом цикле формируется один разряд но всем каналам.

При последовательном вводе данных настройка устройства (фиг. 6) также осуществляется блоком 13 микропрограммного управления при выборке (реализации) микро- нрограммного слова с адресом Ат

Причем с буферного регистра 17 считывается группа разрядов А2, управляюн;ая коммутатором 19.

На вход коммутатора 19 подсоединена щина синхроимпульса СИ 1 (5), которая обес- нечивает синхронизацию ноступающего на устройство последовательного кода но нерво- му каналу ввода данных.

Наличие СИ 1 на соответствующем входе коммутатора 19 означает, что информационный разряд по этому каналу подан на устройство, т. е. на первый вход мультиплексора 12.

Таким образом, первый разряд lepBoro последовательного канала будет занесен на нервый разряд блока 7 в соответствующую ячейку, адрес которой онределяется группой разрядов Q.-j, поступающих на адресный вход блока 7 через блок 9 элементов И-ИЛИ, стробируемую микрокомандой У2.

Прием, дешифрация соответствующих разрядов последовательных кодов, поступающих на устройство но другим каналам, осуществляется аналогично рассмотренному циклу с той лишь разницей, что меняются значения управляющих кодов: онределяюи е- го запись информации в соответствующий разряд блока 7, определяющего запись информации в соответствующую ячейку блока 7, онределяющего номер канала, по которому нодается соответствуюния информация.

Формула изобретения Многоканальное устройство для сопряжения двух ЭВМ, содержащее оперативный за- поминаю1ций блок, грунну элементов ИЛИ, блок элементов И-ИЛИ и группу канальных триггеров, выходы которых являются выходами устройства для подключения к информационным тинам первой ЭВМ, выхо

ды элементов ИЛИ группы соединены -н- формационными входами оперативного .;:i:io- минающего блока, адресные входы которого соединены с выходами б.юка элементов И- ИЛИ, отличающееся тем. что, с целью расширения области гфимс} сния, в устройство введены блок Н1инных формирователей, два мультинлексора, дешифратор режима и блок микронрограммного управления, приче.м первая группа информационных входов блока элементов И-ИЛИ является группой входов устройства для подключения к адрееным шинам второй ЭВМ, первые входы элементов ИЛИ группы соединены с информационными выходами блока шинных формирователей, магистральные входы-выходы которых являются входами-выходами устройства для подключения к информационным шинам второй ЭВМ, выходы оперативного запоминающего блока соединены с информационными входами блока шинных формирователей и с информационными входами первого мультиплексора, выход которого подключен к информационным входа.м канальных триггеров группы, а информационные входы второго мультиплексора являются входами устройства для юдключения к информационным шинам первой ЭВМ, выход второго мультиплексора подключен к вторым входам элементов ИЛИ группы, первый и второй выходы дешифратора режима соединены с входами записи-чтения оперативного запоминающего блока, первая, вторая, третья, четвертая и пятая группы выходов блока .микропрограммного управления соединены соответственно с входами дешифратора режима, второй группой информационных входов блока элементов И-ИЛИ, с управляющими входами первого, второго мультиплексоров и блока шинных формирователей, первый и второй выходы блока микропрограммного управления соединены соответственно с первым и вторым стробирующими входами блока элементов И-ИЛИ, а первая и вторая группы синхровходов блока микропрограммного управления являются соответственно входами устройства для подключения к выходным шинам синхронизации второй и первой ЭВМ, шестая группа выходов блока микропрограммного управления соединена с синхронизирующими входами канальных триггеров группы и является группой выходов устройства для подключения к входным ншнам синхронизации первой ЭВМ, седьмая группа выходов блока микропрограммного управления является группой выходов устройства для подключения к входным щинам синхронизации второй ЭВМ.

J/7

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство для ввода информации | 1986 |

|

SU1352479A1 |

| Устройство для отладки программ | 1988 |

|

SU1661771A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1287155A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1305681A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

Изобретение позволяет расширить функциональные возможности устройства путем обеспечения приема последовательного кода по п каналам и преобразования /7отл/1е/1бшг(7 Ooocfa -Obwaa данные / X: I I с§| - 1ч §s - ТЭ о од V Шцнш Мода последовательного кода Фиг. I дого из принятых кодов в параллельный. Повышается также быстродействие устройства за счет сокраш.ения времени преобразования при формировании последовательных кодов по п каналам одновременно для п ЦВМ. Устройство содержит оперативный за- поминаюший блок 7, блок элементов И-ИЛИ 9 и группу канальных триггеров 11. Кроме того, устройство содержит блок шинных формирователей 10, два мультиплексора 8, 12, дешифратор режима 14 и блок микропрограммного управления 13 с соответствующими связями. 6 ил. шг(7 / I з а t; CJ o S 1 сг. - rsj 5 о 5 з 5- :§§ 1 35. с (Л сз I ,Ц 8| §& 11 fX) ::: |i й- § И -€ i § 35 ОО го ел СХ) ел

Блок параллельного бВода 8аннь 31

параллельного дан- нын одновременно по л наналам

Блок. послЕдобательного SSoda дa данные, одновременно по п каналам,

Блек параллельного данные

От SAOKU параллельного BEaSa, данные

к 5мку последоВатмьного быВода данные

Фаг.

к ёлоку nocAedoSameflii- czc ввода даннь/х

Фиг. 5

От 5мка последовательного вывода данные

о

CCi

§с§

§.ti ;

Й -, «

Г О

5:

1

I

cd

1

IS

§ с;

К параллельного данные

Авторы

Даты

1987-05-23—Публикация

1985-07-04—Подача