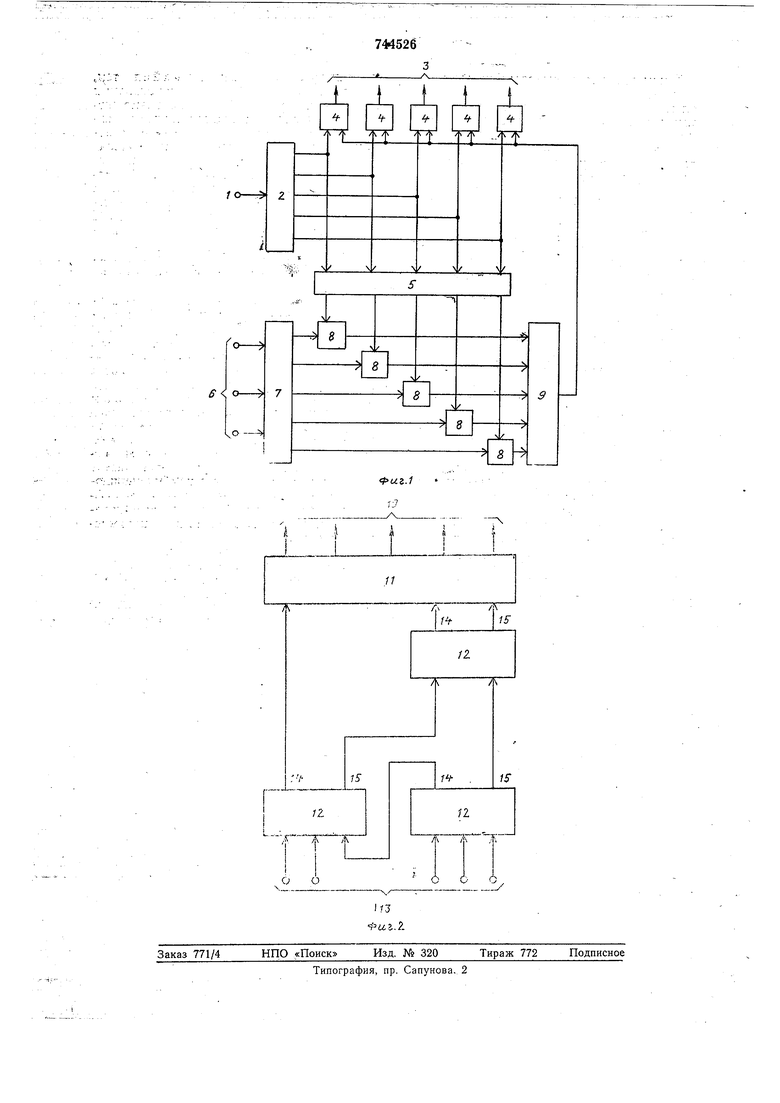

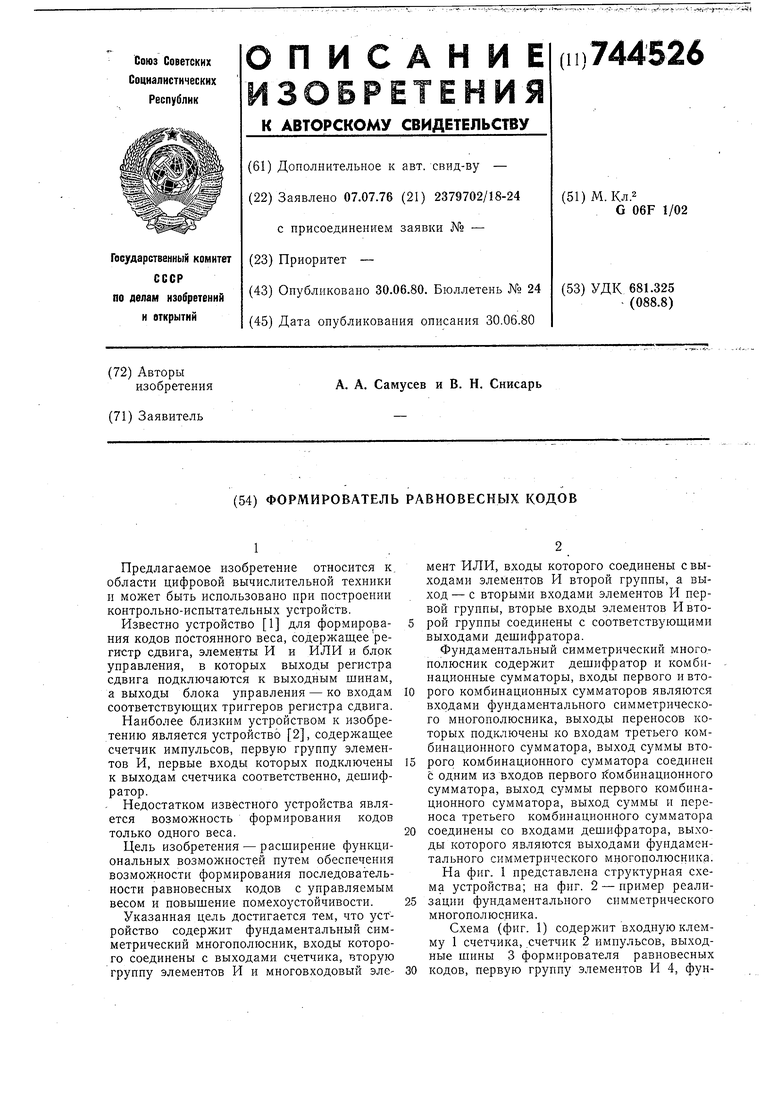

даментальный симметрический многополюсник 5, входные клеммы 6 управления, дешифратор 7, вторую группу элементов И 8, многовходовый элемент ИЛИ 9.

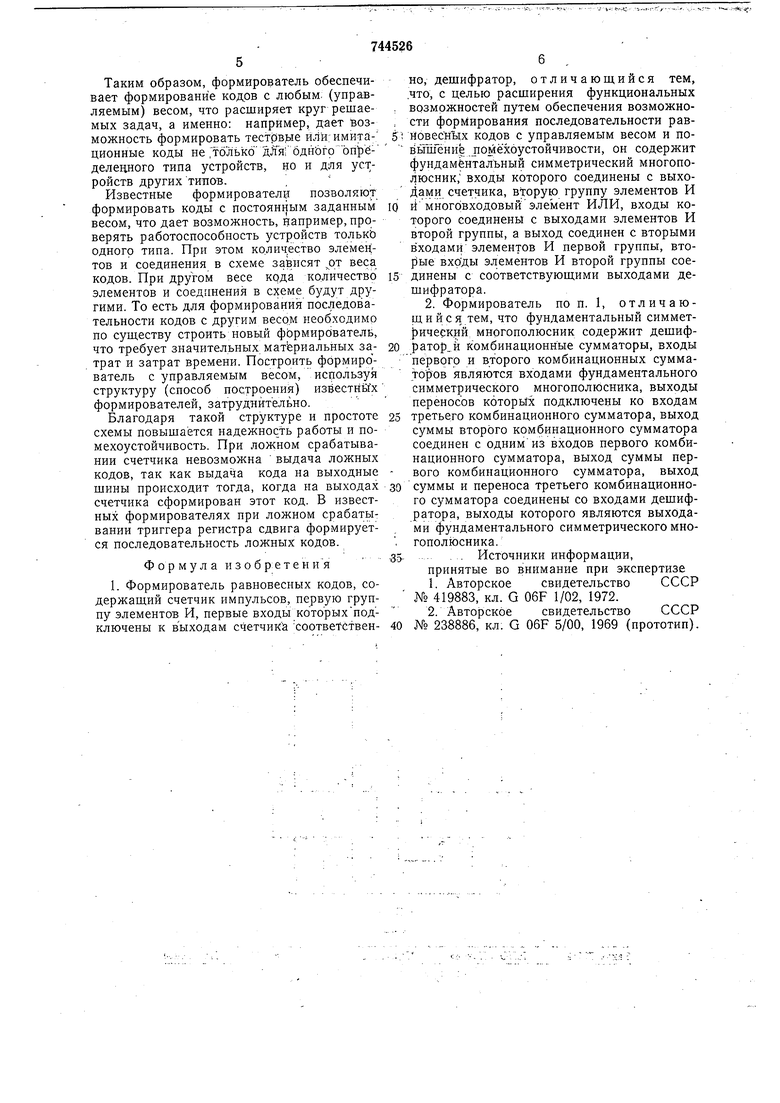

Схема на фиг. 2 содержит выходы 10, дешифратор И, комбинационные сумматоры 12, входы 13 фундаментального симметрического многополюсника, выходы 14 суммы комбинационных сумматоров, выходы 15 переноса комбинационных сумматоров.

Фундаментальный симметрический многополюсник 5 для л переменных имеет в качестве своих выходных функций все фундаментальные симметрические фуикции п переменных.

Фундаментальная симметрическая функция принимает значение, равное единице, на всех тех и только тех наборах аргументов, которые содержат определенное число единиц.

Такнм образом, на соответстЕуюш,ем выходе фундаментального симметрического многополюсника и только на нем устанавливается высокий уровень напряжения только при тех входных кодах, которые содержат определенное количество единиц.

Ко входам элементов И 8 подключены выходы многонолюсника 5 и дешифратора 7, на которых устанавливаются единичные уровни напряжения только при установках на входах многополюсника кодов, содержащих определенное количество единиц, а на входах дешифратора - двоичиого числа, выражающего это количество единиц.

Формирователь работает следующим образом.

Предварительно на входных клеммах 6 управления устанавливается двоичное число, равное весу равновесных кодов, последовательность которых предполагается формнровать. Прн этом на соответствующем выходе дешифратора установится высокий уровень напряжения, который поступает также на второй вход одного из элементов И 8 второй группы.

На входную клемму 1 подаются тактовые импульсы. Счетчик 2 считает тактовые импульсы. При этом на выходах счетчика и на входах многонолюсннка 5 и элементов И 4 первой группы формируется полная последовательность двончных кодов.

На соответствующем выходе многополюсника 5 будет появляться высокий уровень напряжения всякий раз, когда на его входах будет сформирован двоичный код, содержащий оиределеннЪе количество единиц. При этом высокий уровень напряжения подается на первый вход одного из элементов И 8 второй группы. Высокий уровень напряжения с выхода открытого элемента И 8 через многовходовый элемент ИЛИ открывает элементы И 4 первой группы, разрешая прохождение кода с онределенным заданным количеством единиц (весом), сформ;;рованным на выходах счетчика 2, на вьгходные шины 3. Выходы дешифратора 11 являются выходами 10 многополюсника, а входы соединены с выходами комбииациониых сумматоров 12, соединением которых собой обеснечивают параллельный счет количества единиц, подаииых на входы 13 многонолюсника. При этом выход 14 суммы второго сумматора соединен с одним из входовнервого сумматора, выход 15 иеренсса которого вместе с выходом переноса второго сумматора связан со входами третьего сумматора, выход суммы и нереиоса которого вместе с выходом суммы первого сумматора соединены со входами дешифратора 11. Свободные входы первого и второго сумматоров соединены со входами 13 многополюсника.

Фундаментальный симметрический многбполю,сник 5 работает следующим образом.

На входы 13 подается произвольное двоичное число, напрнмер 10100. На выходе 14 суммы второго и, следовательно, на входе первого сумматора установится логическая единица. Так как на входах первого сумматора будет уже две логические единицы, то на его выходе 15 переноса и на одном из входов третьего сумматора устаиовится логическая единица, благодаря которой на выходе 14 третьего сумматора установится тоже логическая единица. На входах же дешифратора II установится двоичное число 010. Такое двоичное число будет появляться на входах дешифратора каждый раз, когда в двоичном числе, подаваемом на входы 13, содержатся только две логические единицы (как в приведенном примере - 10100) независимо от расположения логических единиц и, следовательно, только на одной и той же выходиой шине дешифратора и на одном н томже выходе ,10 многонолюсннка каледый раз будет появляться высокий уровень напряжения (логическая единица).

Формирователь может быть построен для формирования кодов любой разрядности. Для построения формирователя кодов с постоянным весом схема существенно упрощается. В этом случае выходной функцией фундаментального симметрического многополюсника должна быть только одна фундаментальная симметрическая функция п неременных, принимающая значение, равное единице на всех тех наборах аргументов, которые содержат число едиииц, равное весу кода. Вместо фундаментального симметрического многополюсника в этом случае можио использовать пороговую схему или, в простейшем случае, пороговый элемент, реализующий ту же функцию. При этом выход пороговой схемы можно соединить, минуя элементы 8 и 9, с первыми входами элементов И 4. Дешифратор, элементы И 8 н элемент ИЛИ 9 можно не использовать,

Таким образом, формирователь обеспечивает формирование кодов с любым: (управляемым) весом, что расширяет круг решаемых задач, а именно: например, дает возможность формировать Tect( или; имитационные коды не .только дляГбднЬгоопрёделенного типа устройств, но и для устройств других типов.

Известные формирователи позволяют формировать коды с постоянным заданным весом, что дает возможность, например, проверять работоспособность устройств толькЬ одного типа. При этом колич.ество элементов и соединения в схеме зависят от веса кодов. При другом весе кода количество элементов и соединения в схеме будут другими. То есть для формирования последовательности кодов с другим весом необходимо по суш,еству строить новый фЬрмирователь, что требует значительных материальных затрат и затрат времени. Построить формирователь с управляемым весом, используя структуру (способ построения) известных формирователей, затруднительно.

Благодаря такой структуре и простоте схемы повышается надежность работы и помехоустойчивость. При ложном срабатывании счетчика невозможна выдача ложных кодов, так как выдача кода на выходные шины происходит тогда, когда на выходах счетчика сформирован этот код. В известных формирователях при ложном срабатьь вании триггера регистра сдвига формируется последовательность ложных кодов.

Ф о р м у л а и 3 о б р е т е н и я

1. Формирователь равновесных кодов, содержащий счетчик импульсов, первую группу элементов И, первые входы которыхподключены к выходам сЧетчика соответственно, дешифратор, отличающийся тем, .что, с целью расширения функциональных возможностей путем обеспечения возможности формирования последовательности равНовеснь1х кодов с управляемым весом и повыпГёние помехоустойчивости, он содержит фундаментальный симметрический многополюсник; входы которого соединены с выходами счетчика, вторую группу элементов И

ймноговходовыйэлемент ИЛИ, входы которого соединены с выходами элементов И второй группы, а выход соединен с вторыми входами элементов И первой группы, вторые э.лементов И второй группы соединены с соответствующими выходами дешифратора.

2. Формирователь по п. 1, отличающийся тем, что фундаментальный симметрический многополюсник содержит дешифратор й комбинационные сумматоры, входы первого и второго комбинационных сумматоров являются входами фундаментального симметрического многополюсника, выходы переносов которых подключены ко входам

третьего комбинационного сумматора, выход суммы второго комбинационного сумматора соединен с одним из входов первого комбинационного сумматора, выход суммы первого комбинационного сумматора, выход

суммы и переноса третьего комбинационного сумматора соединены со входами дешифратора, выходы которого являются выходами фундаментального симметрического многополюсника.

. Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 419883, кл. G 06F 1/02, 1972.

2.Авторское свидетельство СССР № 238886, кл. G 06F 5/00, 1969 (прототип).

±, JL L JL t

i лГ / ГЖ / Л / /TV

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| ИМПУЛЬСНЫЙ КОДОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2248607C1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Процессор для определения координат частиц в координатной пропорциональной камере | 1979 |

|

SU875408A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU690474A1 |

, N

о

Авторы

Даты

1980-06-30—Публикация

1976-07-07—Подача