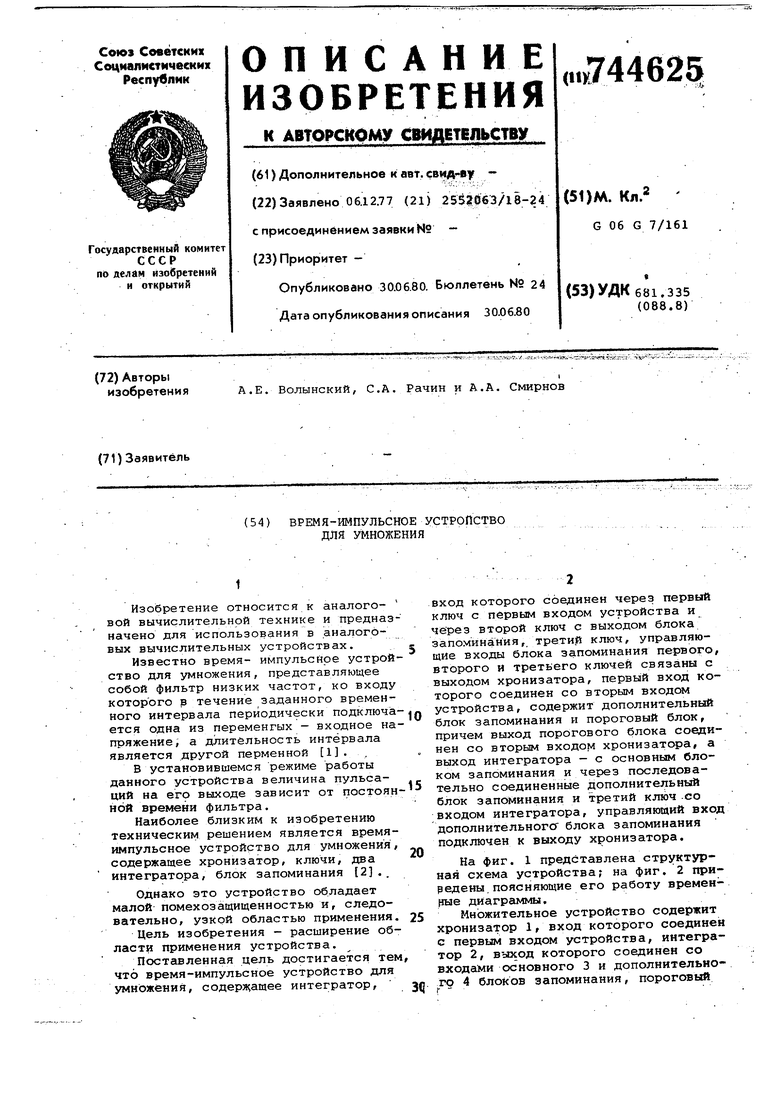

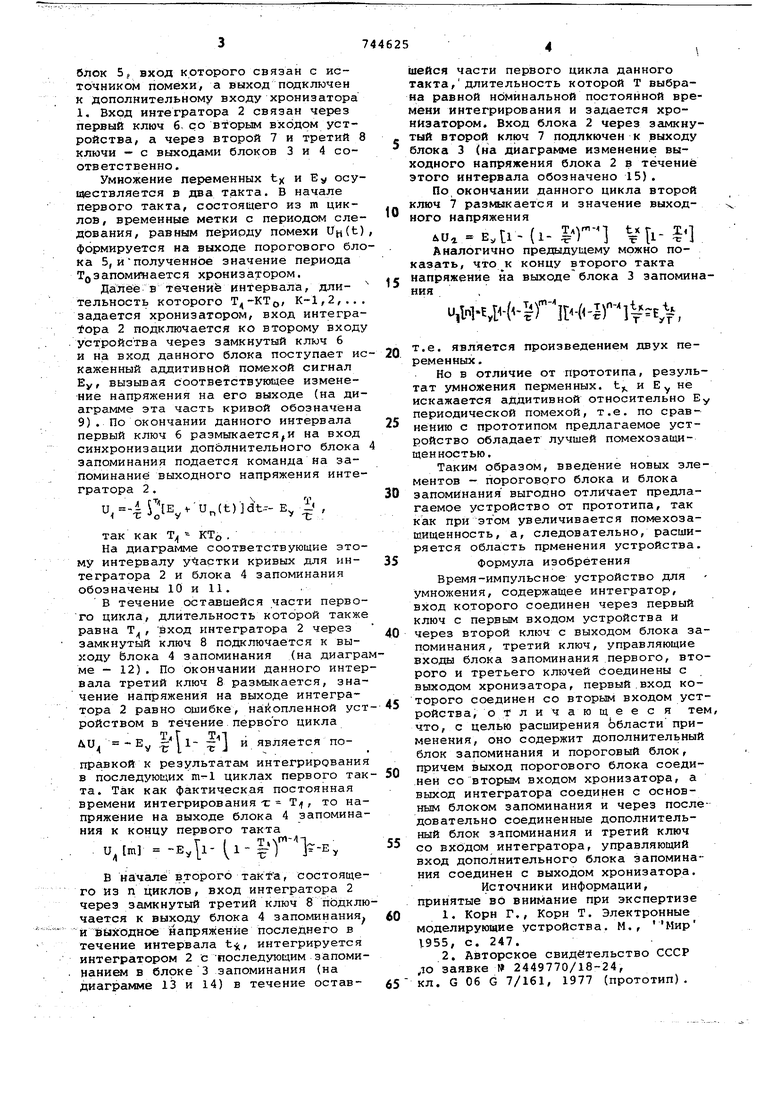

Изобретение относится к аналоговой вычислительной технике и предназ начено для использования в ана.лог6вых вычислительных устройствах. Известно время- импульсное устрой ство для умножения, представляющее собой фильтр низких частот, ко входу которого р течение заданного временного интервала периодически подключа ется одна из переменгых - входное на пряжение, а длительность интервала является другой перменной 1. . В установившемся режиме работы данного устройства величина пульсаций на его выходе зависит от постоян ной времени фильтра. Наиболее близким к изобретению техническим решением является время импульсное устройство для умножения содержащее хронизатор, ключи, два интегратора, блок запоминания 2.. Однако это устройство обладает малой- помехозащищенностью и, следовательно, узкой областью применения Цель изобретения - расширение об ласти применения устройства. Постёшленная цель достигается те что время-импульсное устройство для умножения, содержащее интегратор, вход которого соединен через первый ключ с первым входом устройства и через второй ключ с выходом блока запоминания,, трети.й ключ, управляющие входы блока запоминания первого, второго и третьего ключей связаны с выходом хронизатора, первый вход которого соединен со вторым входом устройства, содержит дополнительный блок запоминания и пороговый блок, причем выход порогового блока соединен со вторым входом хронизатора, а выход интегратора - с основным блоком запоминания и через последовательно соединенные дополнительный блок запоминания и третий ключ .со входом интегратора, управляющий вход дополнительного блока запоминания подключен к выходу хронизатора. На фиг. 1 представлена структурная схема устройства; на фиг. 2 приредены.поясняющие его работу временfnae диаграммы. Множительное устройство содержит хронизатор 1, вход которого соединен с первым входом устройства, интегратор 2, выход которого соединен со входами основного 3 и дополнительного 4 блоков запоминания, пороговый блок 5, вход которого связан с источником помехи, а выход подключен к дополнительному входу хрониэатора 1, Вход интегратора 2 связан через первый ключ б, со вторым входом устройства, а через второй 7 и третий ключи - с выходами блоков 3 и 4 соответственно. Умножение переменных tx и Е осу ществляется в два такта. В начале первого такта, состоящего из m циклов, временные метки с периодом сле Д1эвания, равным периоду помехи формируется на выходе порогового бл ка 5, иполученное значение периода TO запоминаетея хронизатором. Даттёе в течение интервала, длительность которого , К-1,2,.. задается хронизатором, вход интегра тора 2 подключается ко второму вход .устройства через замкнутый ключ 6 и на вход данного блока поступает и каженный аддитивной помехой сигнал Еу, вызывая соответствующее изменение напряжения на его выходе (на ди аграмме эта часть кривой обозначена 9). По окончании данного интервала первый ключ 6 размыкаетсяfи на вход синхронизации допблнительного блока запоминания подается команда на запоминание выходного напряжения инте гратора 2. (t)dt--E 1«, так как Т - КТ, . На диаграмме соответствующие это му интервалу участки кривых для интегратора 2 и блока 4 запоминания обозначены 10 и 11. В течение оставшейся части первого цикла, длительность которой также равна Т , ВХОД интегратора 2 через замкнутый ключ 8 подключается к выходу Ьлока 4 запоминания (на диагра ме - 12). По окончании данного интер вала третий ключ 8 размыкается, значение напряжения на выходе интегратора 2 равно ошибке, накопленной уст ройством в течение первого цикла Т Г Т т Ли - Еу .1- и является поправкой к результатам интегрирования в последующих циклах первого так та. Так как фактическая постоянная времени интегрирования т Т, то напряжение на выходе блока 4 запомина ния к концу первого такта (l) F-i в начале второго такта, состоящего из п циклов, вход интегратора 2 через замкнутый третий ключ 8 подклю чается к выходу блока 4 запоминания и выходное 1Йапряженйе последнего в течение интервала t., интегрируется интегратором 2 с последующим запоминанием в блрке 3 запоминания (на диаграмме 13 и 14) в течение оставшейся части первого цикла данного такта, длительность которой Т выбрана равной номинальной постоянной времени интегрирования и задается хронизатором. Вход блока 2 через замкнутый второй ключ 7 подлкючен к выходу блока 3 (на диаграмме изменение выходного напряжения блока 2 в течение этого интервала обозначено 15). По окончании данного цикла второй ключ 7 размыкается и значение выходного напряжения ли. ЕЛ1-(1- 1Г-1 Vli-il Аналогично предыдущему можно показать, что к концу второго такта напряжение на выходе блока 3 запоминания,1 Ну1Ч - Г -04Г1 Е., т.е. является произведением двух переменных . Но в отличие от прототипа, результат умножения перменных. искажается аддитивной относительно Еу периодической помехой, т.е. по сравнению с прототипом предлагаемое устройство обладает лучшей помехозащищенностью. Таким образом, введение новых элементов - порогового блока и блока запоминания выгодно отличает предлагаемое устройство от прототипа, так как при этом увеличивается помехозащищенность, а, следовательно, расширяется область прменения устройства. Формула изобретения Время-импульсное устройство для умножения, содержащее интегратор, вход которого соединен через первый ключ с первым входом устройства и через второй ключ с выходом блока запоминания, третий ключ, управляющие входы блока запоминания первого, второго и третьего ключей соединены с выходом хронизатора, первый .вход которого соединен со вторым входом устройства, отличающееся тем, что, с целью расширения области применения, оно содержит дополнительный блок запоминания и пороговый блок, причем выход порогового блока соединен со вторым входом хронизатора, а выход интегратора соединен с основным блоком запоминания и через последовательно соединенные дополнительный блок запоминания и третий ключ со входом интегратора, управляющий вход дополнительного блока запоминания соединен с выходом хронизатора. Источники информации, принятые во внимание при экспертизе 1.Корн Г., Корн Т. Электронные моделирующие устройства. М., Мир 1.955, с. 247. 2.Авторское свидетельство СССР ,10 заявке № 2449770/18-24, кл. G Об G 7/161, 1977 (прототип).

У Уп(ФВу

длллтшштпягг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

| Преобразователь среднего значения напряжения | 1980 |

|

SU892322A1 |

| Время-импульсное устройство для умножения | 1977 |

|

SU619927A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| ЦИФРОВОЙ ИНТЕГРИРУЮЩИЙ ВОЛЬТАМПЕРМЕТР | 1972 |

|

SU347909A1 |

| Измерительный преобразователь напряжения | 1981 |

|

SU1075083A1 |

| Масштабный преобразователь напряжения и его варианты | 1980 |

|

SU922780A1 |

| Множительно-делительное устройство | 1980 |

|

SU934494A1 |

| ПРИЕМНОЕ УСТРОЙСТВО СО СТАБИЛИЗАЦИЕЙ УРОВНЯ ЛОЖНЫХ ТРЕВОГ | 1990 |

|

RU2226703C2 |

| Цифровой феррозондовый магнитометр | 1977 |

|

SU721783A1 |

Авторы

Даты

1980-06-30—Публикация

1977-12-06—Подача