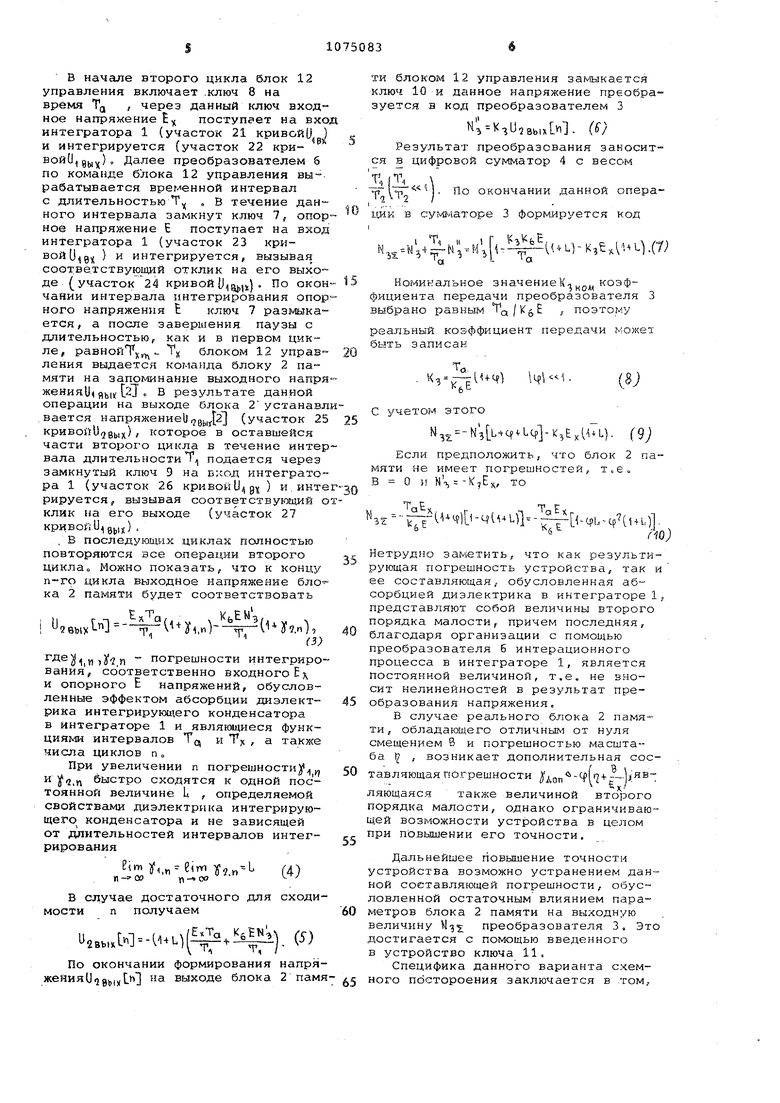

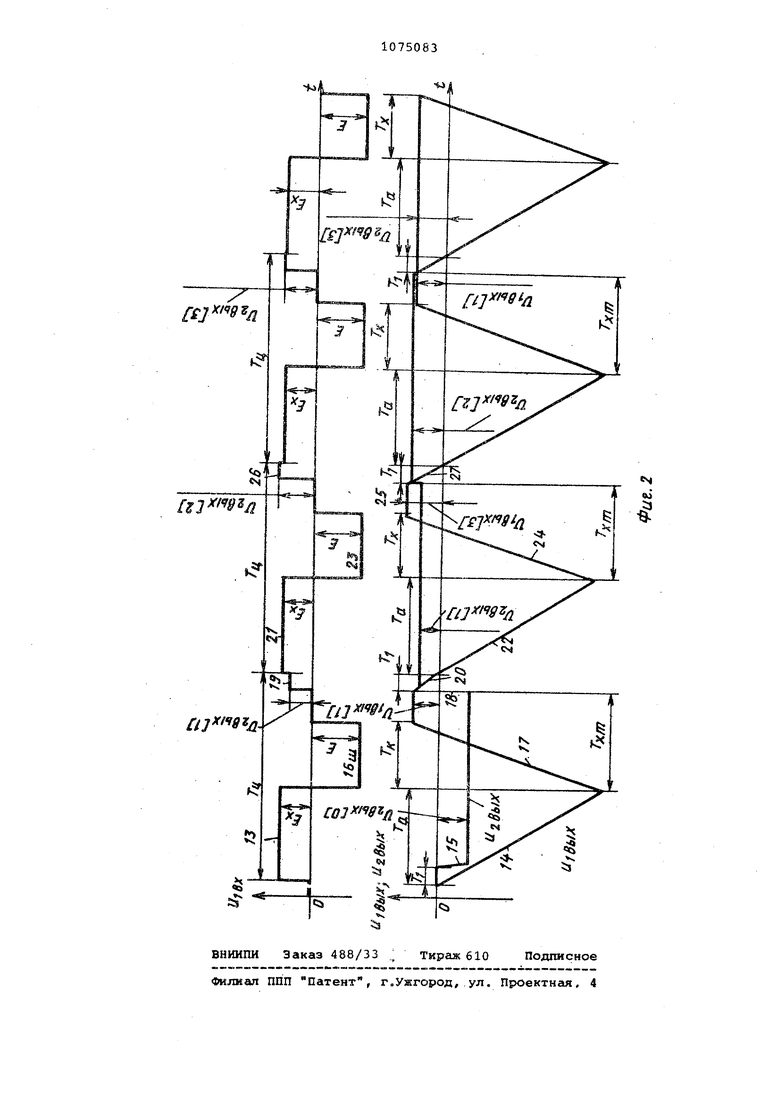

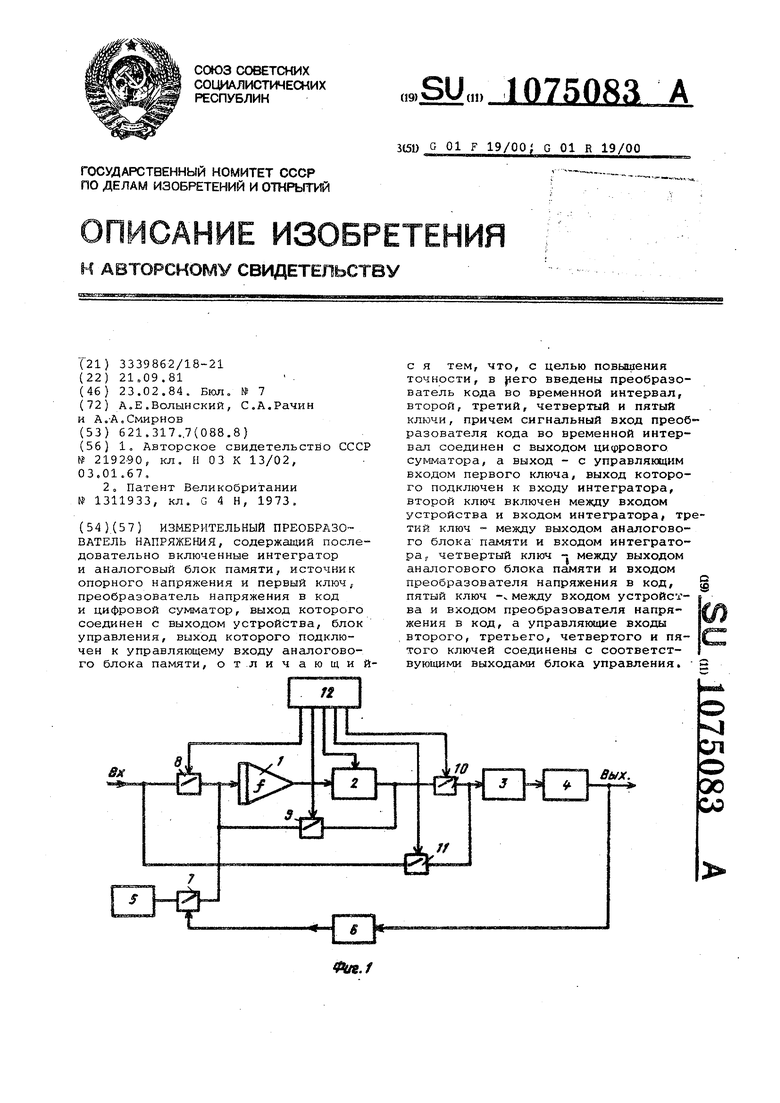

Изобретение относится к электроизмерительной технике и предназначе но для использования в электротехни ческих установках различного назначения, к которым предъявляются повышенные требования в отношении точ ности преобразования и измерения аналоговых сигналов. Известен измерительный преобразо ватель напряжения, реалнзующий IlTeрационно-вычислительный процесс к содержащий, в частности, элемент ИЛ один из входов которого соединен со входом устройства, другой вход с выходом обратного преобразователя кода в напряжение,, а выход - с зхо дом прямого преобразователя напряжения в коДг вычислительный бхюк с памятью, вход которого подключен к выходу преобразователя напряжения в код, один из выходов. к входу преобразователя кода з напряжение, а другой выход - к выходу устройст-ва 1 / Недостаток этого устройства заключается в низкой точности, огракиченной метрологическими характеристикагли обратного преобразователя кода в напряжение, число разрядов которого должно соответствовать числу разрядов результата измерения Наиболее близким по технической сущности к изобретению является измерительный преобразователь напряже нИЯг содержащий последовательно включенные аналоговый блок вычитания,, интегратор, аналоговый блок памяти,, преобразователь напряжения в код, цифровой сумг/.атор,,. источник опорного напряжения,- выход которого .через ключ соединен с одним из входов блока вычитания, другой вход ко торого подключен к входу устройства компаратор с внутренними элементами задания верхнего и нижнего порогов, вход которого соединен с выходом интегратора, а выход - с управляющим входом ключа, преобразователь временного .интервала в код, сигналь ный вход которого подключен к выходу компаратора, а выход к соответст вующему входу цифрового сумматора, блок управления, выходы которого соединены с управляющими входами аналогового блока памяти и преобргазователя временного интервала в код Указанное устройство работает в два такта, результаты преобразова ния которых суммируются в цифровом сумматоре. Во время первого такта, дпительность которого постоянна, пр образуемый сигнал Е постоянно присутствует на первом входе аналогового блока вычитания, к второму вхо ду которого периодически подводится опорные напряжение Ео Дпительность подведения величины Е определяется компаратором, В момент достижения выходным напряжением интегратора верхнего порога компаратора замыкается соответствующий ключ, и выходное напряжение интегратора начинает убывать со скоростью, пропорциональной Е,,. - Е, а при достижении нижнего порога компаратора ключ разкгыкается; и выходное напряжение интегратсра начинает расти со скоростью, пропорциональной Е;, . Суммарная длительность пребывания ключа в з а 1кнутог4 состоянии преобразуется в код преобразователем временного интервала в код и записывается в цифровой су /матор в качестве первого (приближенного) резу.пьтата преобразования. По окончании первого такта блок управления выдает ксмакду ана.пс-гоЕому блоку памяти на запоминание остаточного выходного напряжения интегратора, преобразователь напряжени-я в код преобразует его в соответствующую цифровую величину,- которая, являясь результатом второго такта,заносится в цифровой cyrviMaTOp з качестве поправки к полученно1.1у ранее приближенноЕ у результату поеобразсвания 2 о Недостаток известного устройства также прггявляется з невысокой точности из-за налич.ия погрешности ,обусловленной абсорбц.ией диэлектрика интегрирующего конденсатора в интеграторе., Эта погрешность не может быть учтена предварительной- кал.ибровкой . поскоЛ7 ку нелинейно зависит от длительностей интервалов интегрирования входного и опорного напряжений, которые, в свою очередь, зависят от входного напряжени.я преобразователя. Целью изобретения является повышение точности измерительного устройства. Поставленная цель достигается тем, что в измерительный преобразователь Напряжения, содержаищй последовательно включенные интегратор и аналоговы-й 6.ЛОК памяти, источник опорного напряжения и первый ключ, преобразователь напряжения з код и цифровой сумматор, выход которого соединен с выходом устройства,- блок управления, выход которого подключен к управляющему вхсду аналогового блока памяти,, введены преобразователь кода во временной интервал, второй, третий, четвертый и пятый ключи, причем сигнальный вход преобразователя кода во временной интервал соединен с выходом цифрового сумматора, а выход - с управлякицим входом первого ключа, выход которого подключен к входу интегратора, .второй ключ включен у.ежр.у входом устройства, и входом интегратора, третий ключ - между выходом аналогового блока памяти и входом интегратора, четвертый ключ - между выходом аналогового блока памяти и входом преобразователя напряжения в код, пятый ключ - ме;кду входо устройства и входом преобразователя напряжения в код, а управляю1дие входы второго, третьего, четвертого и пятого ключей соединены с соответ ствующими выходами блока управления На фиг, 1 представлена функциональная схема предлагаемого измерительного преобразователя напряжения на фиг. 2 временные диаграммы сигналов, иллюстрирующие работу уст ройства „ Устройство содержит интегратор 1 (фиг. 1) с номинальной постоянной аналоговый блок 2 памят времени преобразователь 3 напряжения в код цифровой сумматор 4, источник 5 опо ного напряжения,, преобразователь б кода во временной интервал, ключи 7-11, блок 12 управления. Основной измерительный тракт составляют последовательно включенные между входом и выходом устройства ключ 8 интегратор 1, аналоговый блок 2 памяти, ключ 10, преобразователь 3 напряжения в код, цифровой cyrvMaтор 4. Выход источника 5 опорного напряжения через ключ 7 подключен к входу интегратора 1, сигнальный вход преобразователя 6 кода во временной интервал соединен с выходом цифрового сумматора 4, а выход с управляющим входом ключа 7 ключ включен между выходом аналогового блока 2 памяти и входом интегратора 1, ключ 11 включен между входом устройства и входом преобразователя 3 напряжения в код, управляющие входы ключей 8-11 соединены с соответствующими выходами блока 12 управ ления. Работа устройства происходит цик лически. Ее удобно проанализировать с помощью временных диаграмм на фиг где U(gj( i i6bix входное и выходное напряжения интегратора l,U/jg - выхо ное .напряжение аналогового блока 2 памяти. Пусть в одном из вариантов практ ческого использования устройства ключ 11 постоянно разомкнут. В нача ле первого цикла блок 12 управления вьодает команду на замыкание ключа 8 в течение интервала времени постоян ной длительност1 Т., ъ V, . При этом входное напряженней (участок 13 кривой Uigx ) в течение данного интервала поступает на вход интегратора 1 и интегрируется (участок 14 кривойУ ьи) - Выходной сигнал и, gijij интегратора 1 изменяется во времени по закону, определяемому абсорбцион ными свойствами интегрирующего конденсатора , В момент времени t Tj блоком 12 управления вырабатывается команда блоку 2 памяти на запоминание выходного напряжения U( giji интегратора 1„ Напряжение на выходе блока 2 в данной части цикла соответствует участку 15 кривой и по ее окончании с некоторой ошибкой представляет величинуи,,,До -ЕДиг.).ь . где (7 - поправка, учитывающая отключение коэффициента передачи блока 2 от единичного значения, ъ - сдвиг нулевого уровня блока 2 памяти Далее блок 12 управления замыкает ключ 101 и напряжениеи.г9(, на выходе блока 2 памяти преобразуется в код преобразователем 3 с коэффициентом k передачи N; ,.to, (2) после чего полученный код заносится в цр фровой су.к«у1атор 4, В момент времениt TQ,соответствующий окончанию в интеграторе 1 ин терзала интегрирования входного напряжения 11 блоком 12 управления размыкается ключ 8, а преобразователем б с коэффициентом Х передачи вырабатывается интервал для управлеЕ5ия ключом 7 с длительностью Т К N . Во время данного интервала источник 5 опорного напряжения под лючен к входу интегратора 1, и спорное напряжение Е с полярностью., противоположной полярности Е , подается через замкнутый ключ 7 во входную цепь интегратора 1. Изменение входного и выходного сигналов интегратора 1 в данной части цикла соответствуют участкам 16 и 17 кривых и, 0JC и Ui 6i,,xПо окончании интервала интегрирования опорного напряжения ключ 7 размыкается, а после завершения паузы с длительностью, рав.нойТ.-Т, гдеТ mavVx блоком 12 управления вновь вьщается команда блоку 2 памяти на запоминание выходного напряжения Ilj Изменение выходного напряжения блока 2 в данной части цикла соответствует участку 18 кривойио йьк . В оставшейся части цикла блок 12 управления замыкает ключ 9 на время i . В результате на вход нтегратора 1 юдается выходное напряжение и, g(,, блока 2 памяти (участок 19 кривойи,д|.ц) , которое вызывает соответствупищЯ отклик на его выходе (участок 20 кривой),. концу первого цикла ключ 9 размыкается, и на выходе интегратора 1 стается напряжение U, д.,, (Т), гдеГц лительность цикла. В начале второго цикла блок 12 управления включает .ключ 8 на время Тд , через данный ключ вхоД кое напряжение Е поступает на вхо интегратора 1 (участок 21 крив&йи,„ и интегрируется (участок 22 криBottU,g(), Далее преобразователем б по команде блока 12 управления вырабатывается временной интервал с длительностью Т , В течение данного интервала замкнут ключ 7, опор ное напряжение Е поступает на вход интегратора 1 (участок 23 кривой j,g ) и интегрируется, вызывая соответствующий отклик на его выходе -( участок 24 кривой ,,),) . По окон чании интервала интегрирования опор ного напряжения Е ключ 7 размыкается, а после завершения паузы с длительностью, как и в первом цикле, paBHofiTj - Tj( блоком 12 управления выдается команда блоку 2 памяти на запоминание выходного напря женияи йЬ1К И В результате данной операции на выходе блока 2 устанавл .Бается напряжение) (участок 2 кривойО выц) I которое в оставшейся части второго в течение интер вала длительности Т;, подается через замкнутый ключ 9 на вход интеграто ра 1 (участок 26 кривони дх ) и, инт рируется р вызывая соответствующий клик на его выходе (участок 27 KpHBoiiU g ij) , , В последующих циклах полностью повторяются все операции второго цикла о Можно показать, что к концу п-го дикла выходное напряжение блО ка 2 памяти будет соответствовать I и,,,)-(иу,„), ,,у,2п погрешности интегриро вания, соответственно входного Ejs, и опорного Е напряжений, обусловленные эффектом абсорбции диэлектрика интегрирующего конденсатора в интеграторе 1 и являющиеся функция ш интервалов Т и Т, а также числа циклов п„ При увеличении п погрешностиJf „ и f,j, быстро сходятся к одной постоянной величине 1 , определяемой свойствами диэлектрика интегрирующего конденсатора и не зависящей от длительностей интервалов интегрирования1 Jf. 5.п--1- Г4) в случае достаточного для сходи мости п получаем Ua.b,.W 4uL)(.ffii). W По окончании формирования напря жейияиов1,1у1ч1 а выходе блока 2 пам ти блоком 12 управления замыкается ключ 10 и данное напряжение преобразуется в код преобразователем 3 N K Ujgbi W. (S) Результат преобразования заносится в Цифровой сумматор 4 с весом П4 л окончании данной операujdK в суг Ф1аторе 3 формируется код ,--N,4 H;- MUi--4 u t -K,AULi.(t; Номинальное значение К коэффициента передачи преобразователя 3 выбрано равным fg/KgE , поэтому реальный коэффициент передачи может быть записан 1НЦ| . с учетом этого N, -N,,). (9; Если: предположить, что блок 2 памяти не име€;Т погрешностей, т.е. В О I. , то Tot )1-q(.L)-;,(Ul,)l. гг--и Е f-r, tА. Нетрудно заметить, что как результирующая погрешность устройства, так и ее составляющая, обусловленная абсорбцией диэлектрика в интеграторе 1, представляют собой величины второго порядка малости, причем последняя, благодаря организации с помощью преобразователя 6 интерационного процесса в интеграторе 1, является постоянной величиной, т.е. не вносит нелинейностей в результат преобразования напряжения, В случае реального блока 2 памяти, обладаюш,его отличным от нуля смещением В и погрешностью масштаба 1 ,- возникает дополнительная сосCfh |1ЯВтавляющая погрешности Д( ляющаяся также величиной второго порядка малости, однако ограничивающей возможности устройства в целом при повышении его точности. Дальнейшее повышение точности устройства возможно устранением данной составляющей погрешности, обусловленной остаточным влиянием параметров блока 2 памяти на выходную величину УЗХ преобразователя 3. Это достигается с помощью введенного в устройство ключа 11, Специфика данного варианта схемного постороения заключается в .том.

что формируемый в первом цикле код Nj не является результатом преобразования в код выходного напряжения блока 2 памяти, а образуется с помощью преобразователя 3 как результат непосредственного кодирования входного напряжения Е ц . Вследствие этого в данном варианте исключены запоминание блоком j памяти выходного сигнала интегратора 1 (участок 15 кривойи,2в1) и последуюкее замыкание ключа 10 для подачи напряжения и 2 ftbix на вход преобразователя 3 в первом цикле, а вместо указанных операций блоком 12 управления в начале цикла замешкается ключ 11 на время, достаточное для преобразования в код преобразователя 3 входного напряжения Е к . Результат данного преобразования записывается в сумматор 4 с обратным знаком с весом , в дальнейшем код последнего используется, как и ранее, для формирования преобразователем б временного интервала длительности

В последнем случае С х что для устройства с постоянно разомкнутым ключом 11 эквивалентно испол зованию в первом цикле идеального блока 2 памяти с 1 ОиВ 0. В связи с этим в рассматриваемом варианте устройства обеспечивается преобразование в соответствии с выражением (Ю) , т.е. функционирование ключа 11 обеспечивает устранение дополнительной составляющей погрешности, обусловленной наличием неидеального блока 2 памяти.

Таким образом, в предложенном измерительном преобразователе напряжения благодаря примененной итерационной процедуре сравнения сигналов в аналоговой форме достигнуто значительное повьлление линейности преобразования.. Предложенная структура построения преобразователя позволяет устранить влияние абсорбции диэлектрика интегрирующего конденсатора на линейность проходной характеристики и, кроме того, снизить погрешность от неидеальности частотIных свойств интегратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

| Масштабный преобразователь напряжения и его варианты | 1980 |

|

SU922780A1 |

| Множительно-делительное устройство | 1980 |

|

SU934494A1 |

| Источник калиброванных напряжений | 1980 |

|

SU943672A1 |

| Источник калиброванных напряжений | 1979 |

|

SU860021A2 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2011 |

|

RU2449470C1 |

| Устройство для аналого-цифрового преобразования | 1982 |

|

SU1027813A2 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ШИРОТНО-ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2552147C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2496228C1 |

ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ, содержащий последовательно включенные интегратор и аналоговый блок памяти, источник опорного напряжения и первый ключ, преобразователь напряжения в код и цифровой сумматор, выход которого соединен с выходом устройства, блок управления, выход которого подключен к управляющему входу аналогового блока памяти, отличающийс я тем, что, с целью повьанения точности, в jiero введены преобразователь кода во временной интервал, второй, третий, четвертый и пятый ключи, причем сигнальный вход преобразователя кода во временной интервал соединен с выходом цифрового сумматора, а выход - с управляющим входом первого ключа, выход которого подключен к входу интегратора, второй ключ включен между входом устройства и входом интегратора, третий ключ между выходом аналогового блока памяти и входом интегратора,, четвертый ключ между выходом аналогового блока памяти и входом преобразователя напряжения в код, « пятый ключ -. между входом устройства и входом преобразователя напряжения в код, а управляющие входы второго, третьего, четвертого и пятого ключей соединены с соответствующими выходами блока управления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Разрядная трубка | 1924 |

|

SU2192A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-02-23—Публикация

1981-09-21—Подача