(54) ПРЕОБРАЗОВАТЕЛЬ СРЕДНЕГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Масштабный преобразователь напряжения и его варианты | 1980 |

|

SU922780A1 |

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

| Множительно-делительное устройство | 1980 |

|

SU934494A1 |

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ ПРОИЗВОЛЬНОЙ ФОРМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2034302C1 |

| СПОСОБ ДВУХТАКТНОГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕГРИРУЮЩЕГО ТИПА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2564909C1 |

| Источник калиброванных напряжений | 1980 |

|

SU943672A1 |

| Измерительный преобразователь напряжения | 1981 |

|

SU1075083A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ МАГНИТНЫХ ПОЛЕЙ | 1997 |

|

RU2118831C1 |

| Аналого-цифровой преобразователь для тензометрических устройств | 1980 |

|

SU997246A1 |

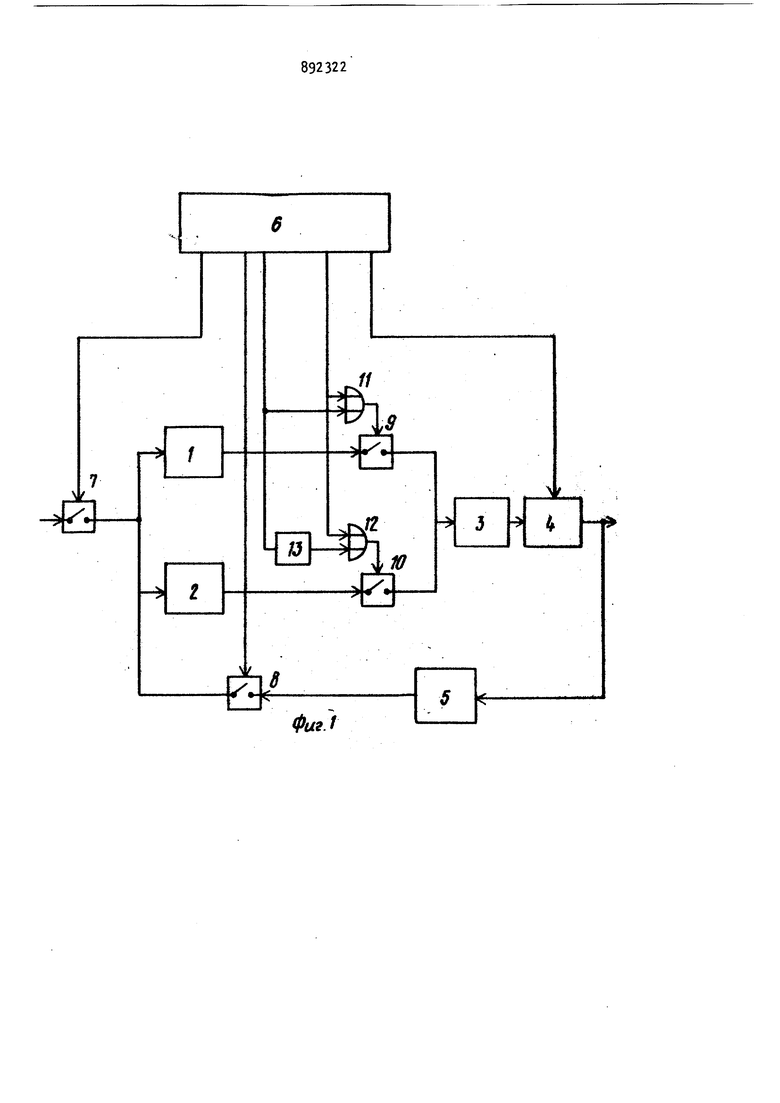

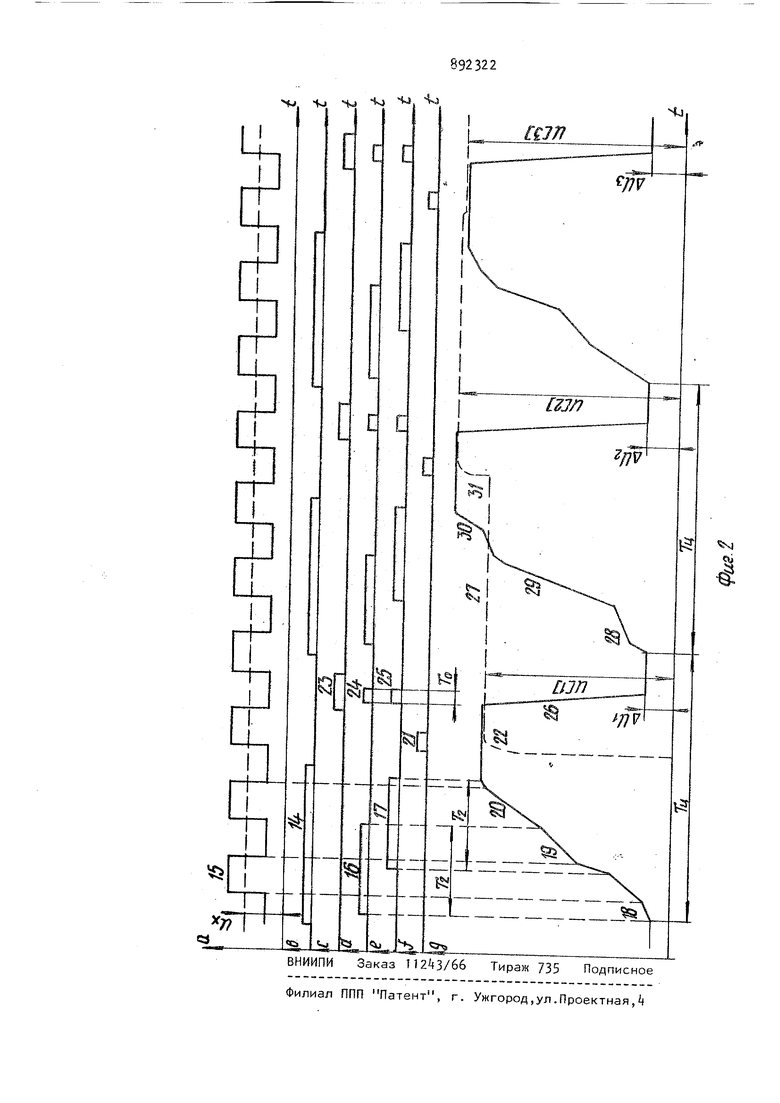

; Изобретение относится к преобразб|вателям среднего значения напряжения и может быть использовано в электротехнических установках различного назначения . Известен преобразователь среднего значения напряжения, представляющий собой фильтр низких частот, ко входу которого в течение заданного временно го интервала периодически подключается входное напряжение, а длительность данного интервала пропорциональна тре буемому значению масштабного коэффициента устройства fij. Недостатком этого устройства является то, что в установившемся режиме работы величина пульсаций.на его выходе зависит от постоянной времени фильтра. Наиболее близким техническим решением к изобретению является преобразователь среднего значения напряжения, содержащий преобразователь на пряжения в ток, последовательно включенные интегратор, аналоговый запоминающий блок и масштабный преобразователь, например делитель напряжения, блок управления и три ключа, в котором вход преобразователя напряжения в ток через первый ключ связан со входом устройства, а через второй ключ - с выходом масштабного преобразователя, выход преобразователя напряжения в ток через третий ключ связан со входом интегратора, выход аналогового запоминающего блока является выходом устройства, а управляющие входы ключей и вход синхронизации аналогового запоминающего блока соединены с соответствующими выходами блока, управления 2. Недостатком известного устройства является прямопропорциональная зависимость между дополнительной погрешностью преобразования и показателем расстройки текущего значения периода помехи, что ограничивает область применения устройства. Цель изобретения - увеличение помехозащищенности . Поставленная цель достигается тем, что в преобразователь среднего значения напряжения, содержащий преобразователь напряжения в ток, последовательно включенные интегратор, запоминающий блок и масштабный преобразователь, блок управления и три ключа, вход преобразователя напряжения в ток через первый ключ соединен с входной клеммой устройства, а через второй ключ - .с выходом масштабного преобразователя, выход преобразователя напряжения в ток через третий ключ вклю Мен на вход интегратора, выход которо го соединен с выходной клеммой устройства, а управляющие входы первого и второго ключей и вход синхронизации запоминающего блока соединены с соответствующими выходами блока управ ления, введены дополнительный преобра зователь напряжения в ток, ключ, два логических элемента ИЛИ и блок задерж ки, причем вход дополнительного преобразователя напряжения в ток соединен с входом преобразователя напряжения в ток, а выход через четвертый ключ соединен со входом интегратора, управляющие входы третьего и четвертого ключей соединены соответственно с выходами первого и второго логических элементов ИЛИ, первые входы которых подключены к первому дополнительному выходу блока управления, а второ дополнительный выход блока управления соединен со вторым входом первого лог ческого элемента ИЛИ и через блок задержки - со вторым входом второго логического элемента ИЛИ. На фиг. 1 приведена структурная схема устройства; на фиг, 2 - поясняю щие его работу временные диаграммы: изменения входного сигнала и помехи показаны на диаграмме а, работа первого, второго, третьего и четвертого ключей поясняется соответствующими диаграммами Ь, с, d и е сигналы управления (синхронизации) запоминающего блока показаны на диаграмме f, а изменения выходных напряжений интегратора и запоминающего блока - на диаграмме д. Преобразователь среднего значения напряжения содержит первый и второй преобразователи 1 и 2 напряжения в TQK, последовательно включенные интегратор 3 запоминающий блок и мас24штабный преобразователь 5 блок 6 управления, первый, второй, третий и четвертый ключи 7 и 8, 9 и 10, соответственно, первый и второй логические элементы ИЛИ 11 и 12 и блок 13 задержки. Устройство работает следующим образом. В начале первого цикла блок 6 управления замыкает ключ 7 (замкнутое состояние ключа 7 обозначено на диаграмме кривой 1). В результате на входы преобразователей 1 и 2 напряжения в ток, подается входное напряжение UK , искаженное аддитивной периодической помехой Un(t) (на диаграмме изображен простейший вид помехи, имегаций форму меандра); алгебраическая сумма данных величин показана кривой 15. На выхо-/ дах преобразователей 1 и 2 напряжения, в ток коэффициенты преобразова-: ния которых соответственно S и S устанавливаются токи, пропорциональные текущему значению сигнала (кривая 15); по окончании переходных процессов в преобразователях 1 и 2 напряжения в ток блоком 6 управления выдается команда логическому элементу ИЛИ 11 на замыкание ключа 9 (замкнутому состоянию ключа 9 соответствует кривая 16). При этом длительность интервала замыкания ключа 9 Тл (2г+1) где г 0,1,2т.е. выбрана равной, как показано на диаграмме , номинальному периоду помехи или больше этой величины в нечетное число раз. Формируемой блоком 6 управления данный интервал поступает также на вход блока 13 задержю, в котором задерживается на время 0,5 и после задержки подается через логический элемент ИЛИ 12 на управляющий вход ключа 10, обеспечивая замыкание ключа 10 на время TQ (замкнутое состояние ключа 10 в этой части цикла показано на диаграмме кривой 17). В результате )гх операций выходные токи преобразователей 1 и 2 напряже- ния в ток поступают на вход интегратора 3 и интегрируются, вызывая соответствующее возрастание выходного напряжения на участках 18, 19 и 20, где кривая 18 соответствует реакции интегратора 3 на выходной сигнал преобразователя 1 напряжения в ток, кривая 19 соответствует изменению выходного напряжения интегратора в у результате интегрирования суммы выходных .токов преобразователей 1 и 2 напряжения в ток, а кривая 20 соответствует изменению выходного сигнала интегратора 3 во время интегрирования только выходного тока преобразователя 2 напряжения в ток. По окон чании данных частиц цикла выходное напряжение интегратора 2 достигает величины U,,.0,( (5,5,)тД озтхJ ,рДО)0,(.0),0)4Лд(0)1, К (5 5,ГГ7. V К L (0), где начальное выходное напряжение интегратора 3, (,5Т„цГчO Tn iTa 0) Jntt)3t. (.0 yn(t)dt-, lOjsJu Wa о0,5Тп„TI Далее блоком 6 управления размыка ется ключ 7 и вырабатывается управля щий интервал (на диаграмме кривая 21 во время которого подается команда запоминающему бдоку на запоминание выходного напряжения U,t1 интегратора 3 (изменение выходного напряжения запоминающего блока k показано н диаграмме участком прерывистой кривой 22). По окончании данного интервала блок 6 управления вырабатывает сигнал, по которому замыкается ключ 8 (на диаграмме - 23). При этом на входы преобразователей 1 и 2 напряжения поступает масштабированное мас штабным преобразователем 5 в m раз выходное напряжение запоминающего блока 4 и tn - и на выходах преобразователей 1 и 2 напряжения в ток устанавливаются токи, пропорциональные данному напряжению. По окончании переходных процессов в преобразователях 1 и 2 напряжения в ток блок 6 управления через логические элементы ИЛИ 11 и 12 выдает сигналы, по которым на время Т о замыкаются одновременно ключи 9 и 10 (на диаграмме соответственно 2k и 25) и сумма выходных токов преобразователе интегрируется интегратором 3 (соответствующее изменение выходного си1- нала интегратора 3 показано на диаграмме 26), Убывающий характер изменения выходного сигнала интегратора 3 в данной части цикла обеспечивается условием ( S) К (на диаграмме изображен частный случай, соответствующий m -1 и (S,+ S2)K 0), а длительность интервала интегрирования задана равной Тд ()SoKoml где SQ и KQ - номинальные значения коэффициентов передачи S, I 1,2 и К соответственно, причем К KO(H- . ), Sv So (l+af.) К концу данной завершающей части цикла выходное напряжение интегратора 3 достигает величины uU,--0 tl {l4mT,iVSu),,cr)4 (),которая характеризует накопленную устройством ошибку, при этом на выходе запоминающего блока Ц сохраняется заполненное ранее значение U }, которое является первым приближенным результатом преобразования. Нетрудно, аналогично первому циклу, показать, что к концу ri-го цикла работы устройства) ( кр uu)x . Анализ (3) намного упрощается, если ограничиться рассмотрением варианта устройства, в котором начало цикла привязано к начальной фазе помехи. В этом случае i.(i),io)Or(o)),СА) и тогда (,)) Подставив в полученное выражение значение X , после несложных преобразований получим :UM U 0 fl4nNToiS,S,)K} - l-5; l-{|;VV3.i w,.i4) i|i-p«n-T,lS,tSjtc j, r-(s7Wi величина Ул является дополнительной погрешностью преобразователя среднего значения, обусловленной воздействием периодической помехи нормального вида. С помощью простых математических выкладок можно показать, что « яв ляется по сравнению с соответствующей велич 1ной в известном устройстве величиной второго порядка малости K; d5-d ч в ;связи С ЭТИМ, предлагаемый преобразователь обладает более высокой помехозащищенностью, что позволяет использовать его для выделения и мас штабирования сигналов низкого уровня на фоне периодических помех, а это oбctoятeльcтвo дает возможность расш рить область возможного применения преобразователя среднего значения на пряжения . Формула изобретения Преобразователь среднего значения напряжения, содержащий преобразователь напряжения в ток, последователь но включенные интегратор, запоминающ блок и масштабный преобразователь, блок управления и три ключа, вход преобразователя напряжения в ток чер первый ключ соединен с входной клеммой устройства, через второй ключ с выходом масштабного преобразовател выход преобразователя напряжения в ток через третий ключ включен на вхо интегратора, выход которого соединен со входом запоминающего блока, выход которого соединен с выходной клеммой устройства, а управляющие входы первого и второго ключей и вход синхронизации запоминающего блока соединены с соответствующими выходами блока управления, отличающийс я тем, что, с целью увеличения помехозащищенности, в него введены дополнительный преобразователь напряжения в ток, ключ, два логических элемента ИЛИ и блок задержки, причем вход дополнительного преобразователя напряжения в ток соединен с входом преобразователя напряжения в ток, а выход через четвертый ключ соединен со входом интегратора, управляющие входы третьего и четвертого ключей соединены соответственно с выходами первого и второго логических элементов ИЛИ, первые входы которых подключены к первому дополнительному выходу блока управления, а второй дополнительный выход блока управления соединен со вторым входом первого логического элемента ИЛИ или через блок задержки со вторым входом второго логического элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3605002,кл.307-150, 1975. 2.K.Yamaguchi DC Standard Voltage Generator using PWM, журнал Yokogarfia Technical Report, v.T/, I 2, 1973 (прототип).

ч

L Д

w

X.

Фи. 1

Авторы

Даты

1981-12-23—Публикация

1980-04-17—Подача