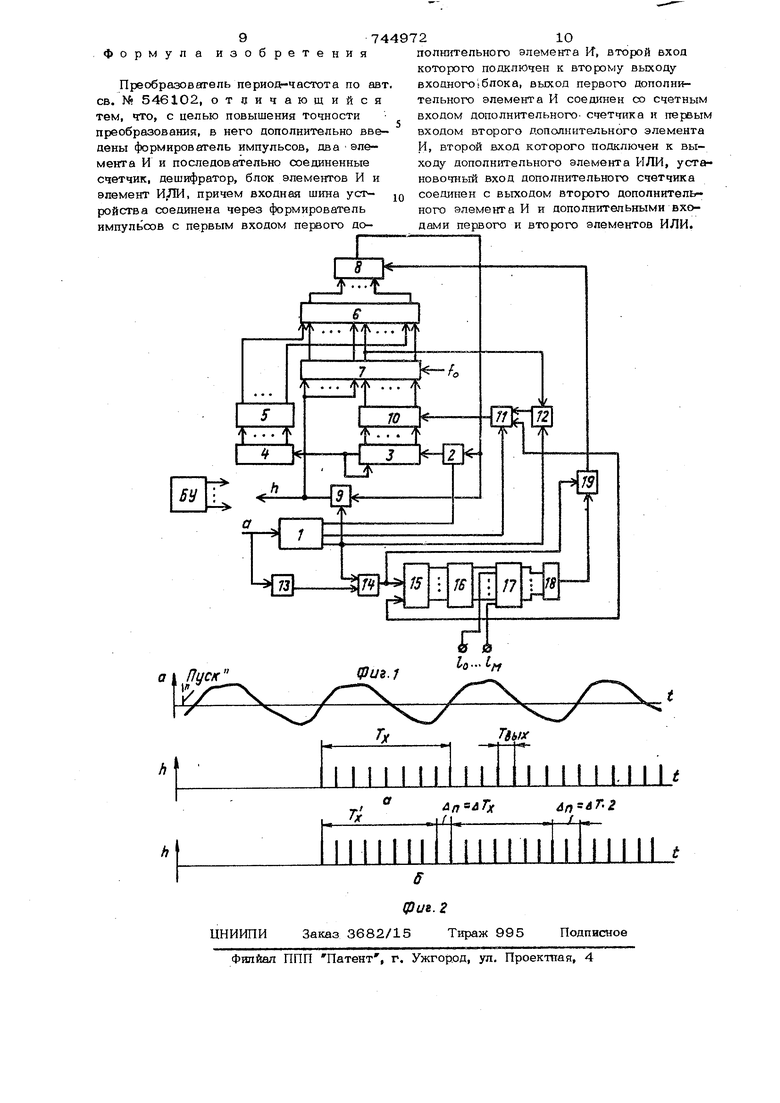

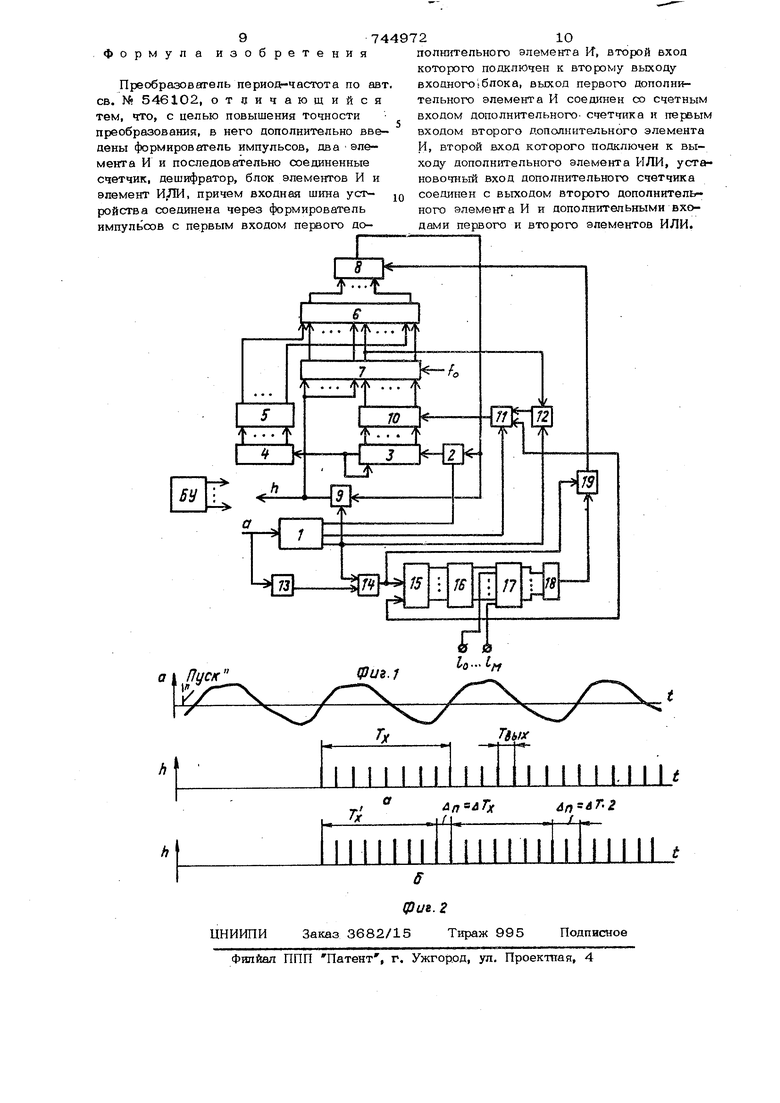

Изобретение относится к вычислительной и измерительной технике и может использоваться для управления специализированных устройств, занятых обработкой аналотх вых сигналов, а также а качестве измерите л ьнотх) прибора, позволяющего измерять период входных сигналов и вырабатьшать последовательность импульсов с частотой следования, обратно пропорциональной периоду входного сигнала. По основному авт. св. № 546102 известно устройство, содержащее последовательно включенные входной блок, первый элемент И, первый и второй счетчики, дешифратор, первый блок элементов И, вто- рыб входы которогч) подключены к выходам делителя, а выходы - к входам первого элемента ИЛИ, выход которого подключен к второму Bxocty первого элемента И, второй вход входного блока подключен к первому входу второго элемента И, вторюй вход которого подключен к выходу первого элемента ИЛИ, а выход является выхо дом устройства и подключен к нулевым входам старших триггеров делителя, установочные входы младших триггеров кото- . рогхэ подключены к выходам второго блока элементов И, информациоинью входы которого подключены к выходам первого счетчика, а управляющий вход - к Bbixoziy второго элемента ИЛИ, первый вход которого подключен к третьему входу входного блока, второй выход которого подключен к первому входу третьего элемента И, выход которого подключен к второму входу второго элемента ИЛИ, а второй вход - к выходу триггера делителя, номер которого равен номеру старшего триггера в первом счетчике. Недостатком известного устройства является то, что в нем имеет место накопление ошибки положения (во времени) входных импульсов относительно начальных точек отсчета входного сигнала, величина которой с течением времени (при прохождении нескольких периодов входного сигнала) может превысить допустимое значение Л г,оп , ншрик ер, преобразоватепь период-частота в идеальном случае преобразовывает период входного сигнала в частоту следования импупьсов таким образом, что за время Т- следования одного (каждого) периода вход1г1ого сигнала возникает восемь импульсо1В, период следования которых Т,. В рэальны условиях ограниченной разрягшой сетки первого счетчика измерение периода входного сигнала происходит с некото рой погрешностью Т Ту,- Т ( Т -измеренное значение . Т ), При этом период следования выходных импульсов х- т.е. поло;«ение 8 каждого импульса во времени будет опре делено с некоторой ошибкой Л Таким образом, по истечении нескольких, например К , периодов входного сигнала последний (восьмой) импульс на К-м периоде будет находиться от первого выходного импульса по оси времени на раостоянии (К. -- ) а на ( TX К. - И ) это должно быть в идеальном случае. Таким образом, ошибка положения Д.р( последнего из каждого К -го периода . К . Ошибка i.f. в извес гньк преобразователях не учитывается, и поэтому в случае испольэова ния известных преобразова(гелей периодчастота (умножителей частоты) в качестве блока управления специализированных устройств, занятьк обработкой С1П налов, могут быть получены результаты с боль шой ошибкой Целью изобретения является повышени точности преобразования за счет повышения точности задания временного располо жения выходных импульсов. Цель достигается тем, что в преобразователи период-Частота, содержащий последовательно включенные входной блок, первый элемент И, первый и второй счет чики, дешифратор, первый блок элементов И, вторые входы которого подключены к выходам делителя, а выход - к входам первого элемента ИЛИ, выход которого подклкэчен к второму входу первого элемента И, второй и третий элементы И, второй блок элементов И и второй элемент ИЛИ, второй выход входного блока подключен к первому входу второго элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, а выход является выходом устройства и подключе к нулевым входам старших триггеров делителя, установочные входы младших триг геров которого подключены к вькодам второго блока элементов И, и)4к)рмационHbje входы которого подключены к выходам первого счетчика, управлякхций вход - к выходу второго элемента ИЛИ, первый вход которого подключен к третьему выходу входного блока, второй выход которого подключен к первому входу третьего элемента И, выход которого подключен к второму входу второго элемента ИЛИ, а второй вход - к выходу триггера делителя, номер которого равен номеру старшего триггера в первом счетчике, дополнительно введены формирователь импульсов, два элемента И и последовательно соединенные счетчик, дешифратор, блок элементов И и элемент ИЛИ, причем входная шина устройства соединена через формирователь импульсов с первым входом первого дополнительного элемента И, второй вход которого подключен к второму выходу входного блока, выход первого дополнительного элемента И соеш«1ен со счетным входом дополнительного счетчика и nepBMNi входом второго дополнительного элемента И, второй вход которого подключен к выходу дополнительного элемента ИЛИ, установочный вход дополнительного счетчика соединен с выходом второго дополнительного элемента И и дополнительными входами первого и второго элементов ИЛИ, На фиг. 1 приведена структурная схема предлагеемого преобразователя периодчастота; на фит, 2, а,б - временные диаг раммы, поясняющие необходимость введе- корректирующей цепи, Преобразователь содержит последовательно включенные входной блок 1, первый элемент И 2, первый счетчик 3, второй счетчик 4, дешифратор 5, первый блок элементов И 6, вторые выходы которого подключены к выходам делителя 7 опорной частоты, а выходы - к входам первого элемента ИЛИ 8, выход которотлз подключен к второму входу первого элемента И. Второй выход входного блока подключен к первому входу второго элемента И 9, второй вход которого подключен к выходу первого элемента ИЛИ, а выход является выходом устройства в целом и подключен к щелевым входам старших триггеров делнтеля опорной частоты, установочные входы младших триггеров которого подключены к выходам второго блока элементов И 10, информационные входы которого подключены к выходам первого счетчика, а управляющий вход - к выходу второго элемента ИЛИ 11, первый вход которого подключен к третьему выходу входного блока, второй выход которотх) подключен к первому входу третьего элемента И 12, 574 выход которого подключен к второму входу второго элемента ИЛИ, а второй вход третьего элемента И подключен к выходу триггера из делителя, номер которого равен номеру старшего триггера в нервом счетчике. Вход входного блока подключен к входу формирователя импульсов 13, выход которого по1П{лючен к первому входу первого дополнительного элемента И 14, второй вход которого подключен к второму выходу входного блока 1, а выход - к счетному входу дополнительнотх) счетчика 15, выходы которого подключены к входам дополнительного дешифратора 16, выходы которого подключены к соответствующим первым входам каждого из элементов дополнительного блока элементов И 17, вторые входы которых подключены к соответствующим входным клеммам (6о , 1 , Ь 2 . N4 ). выходы дополнительного блока элементов И подключены к входам дополнительнотх) элемента ИЛИ 18, выход которого подключен к первому входу второго дополнительного элемента И 19, выход которого подключен к дополнительным входам первого и второго элементов И и (установочному) входу дополнительного счетчика, а второй вход - к первому входу дополнительного счетчика. Кроме того, устройство содержит блок управления БУ, обеспечивающий работу устройства. По существу положительный эффект заключается в том, что дополнительно введенные блоки (дапее для краткости цепь коррекции) обеспечивает определение величины Л.- лТх, -К и сравнение текущего значения величины ошибки положения Д.-лс ее допустимым значением Л( . При выполнении условия д ikn von цепь коррекции не влияет на работу собственно преобразователя период-частота. При /iin пд,оп цепь коррекции вырабатьшает сигнал, который устанавливает устройство в положение, исходное для генерирования (формирования выходньк импульсов. Устройство работает следующим образом. В исходном состоянии все счетчики находятся в нулевом положении, на вы- . ходах входного блока 1 - запрещающие по тенциалы, на одной из входных клемм разрещакяций потенциал. Номер i входной клеммы задается априорно из следующих соображений. Так как величина не должна быгь больше Л 2 вательно, , так как ,, Величина k., задается перед-решением задачи (конкретная в еличина дпя каждого конкретного случая). Величина й.Т-ц. определяется разрядностью счетчиков Э и 4, а поэтому для конкретного устройства постоянна и определена заранее. Поэтому для конкретной задачи модага заранее определить число К периодов входного сигнала, внутри которых ошибка положения выходных импульсов не превышает допустимую. Аппаратно задание величины АПЛ п предлагаемом устройстве реализовано следующим образом. Каждому значению К ставится в соответствие номер л входной клеммы . Счетчик 15 производит подсчет числа периодов выходного сигнала,начиная с момента формирования .вы- ходных импульсов. Де1лифратор 16 декадирует состояние счетчика 15 и последовательно (с увеличением кода в счетчике 15) открывает элементы И из блока элементов И 17. При достижении числа периодов величины соответствующий элемент И из блока 17 формирует корректирующий сигнал, который устанавливает устройство в положение, исходное для генерирования (формирования) выходных импульсов. По сигналу Пуск, вырабатываемому блоком управления (управляющие связи для упрощения чертежа не показаны), на вход делителя 7 поступают импульсы опорной частоты IQ выходов триггеров делителя 7 па вторые входы первого блока элементов- И 6 поступают импульсы частот 5р(,2, Q (4 , iajg,.-При первом после сттгнапа Пуск переходе значения входного сигнала через куль из отрицательных значений в положительные на первом выходе входного блока 1 появляется разрешающий потенциал, открывающий элемент И 2 по первому входу. В первый момент времени после сигнала Пуск, код во втором счетчике 4 нулевой. На вход формирователя 13 поступает входной сигнал, по окончании каждотчэ периода которого формируются сигналы, которые поступагот на первый вход элемента И 14. Дешифратор 5 подает разрешающий потенцишт на первый вход первого младшего элемента И из блока 6, а на остальные элементы И блока 6 - запрещающие потенциалы. Поэтому на первый элемент ИЛИ 8 будет посту пать caivjan высокая частота o|z из набора выходных частот делителя 7 опорной частоты о . С выхода первого элемента ИЛИ 8 через открытьгй элемент И 2 поо774гупают нмпупьсы на вход счетчика 3. При поступпенкк на вход счетчика 3 и импупь- СОЕ с частотой . выбкрается из уотовкя достижения необходимой точности измерения периодов в кшкдоь; поддиапазоне) происходит его переполвэниэ. При пераполнении счетчика 3 занос ггся + l в счетчик 4, а в счеинк 3 при этом заносится код, равный полови1 :е его емкости. Последнее необходимо дпя учета части измеряемого периода, равтюй по величине Н . При коде ОО„,01 а ;счетчике 4 на первом входе п-ерзоп;) ;(младшего) и во всех, кроме sTojooro, элементах И из блока 6 появляется аап;рещавдций потенциал, а на первом входе второго элемента И из блока б - разрешающий потенциал. Таким образом, счетчика 3 теперь поступают импу частота спедозания которых вдоое Ше прайьшущей очередном леоекопкеш;;; иШ1чк«с счетчике 4 увеличивается па единицу, а в /счетчик 3 заноситск код. равный ПОПОЕК: не его емкости Ч( при W 2 запоси ся единица в старший разряд), я частота импульсов, лаушлк на вход счет-дака 3 уменьшается в два раза. Так происходит до того момента времени.; когда входном сигнап второй раз перейдет через нуль из отрицательных значений Б положитпльнь-е, т.е. когда окончится перттод Т v измеряемого сигкапа. При этом на перво;-. выходе выходного блока появится запрещающий потенциал, закрг.твшощий влеь- ент И 2, На этом заканчивается цикл изм ;рейия, в результате которого т;а сц угакках 3 и 4 о1юрыирован код, пропорцпо-нальный периоду Ту exoanoix) сигната причем код Б счетчйке 4 показывает, в каком поддиапазоне лежит период i % , а код в счетчике 3 опроделгет 1 v вну1 ри поддиапазона, В этот же момйИ : вртмани на третьем вькоде блока 1 формируется управляющий сигнал, который через элемент ИЛИ 11 поступает и а управляющий вход блока элемйнтоз И л О,, Первые входы блока элементов И 10 чеиы к соответствующим входам тригг-еров счетчика 3. Таким oбpaзo, прэизводится запись дополнительного кода, кото рый содержится в счетчгже 3, в и младшие разряды делителя 7, На втором выходе блока 1 в это же врекЩ ноявляет разрешающий гютегодиап открывазощий эле мент И 9 и третий элемент И 12 по пер вьш входам, причем каждый импульс с бь хода второго эпемез-гга И 9 устап;,:зл1шает старшие разряды делителя 7 н гг/пеное со 2 триггера делителя 7 переписывает в Vi младшие разряды делителя 7 дополнительный код счетчика 3. Коэф4ициент пересчета младших триггеров делителя 7с учетом записанного в них дополнительного кода из счетчика 3 пропорцноиалеп содержимому счетчика 3, которое,, в свою очередь, пропориионально периоду Ту входного сигнала. Возбужденный выход дешифратора 5 однозначно определяет часахзтный поддиапазон фэрмируемой на выходе устройства импульсной последовательности (грубая шкала). Ко91|х|)ициеит пересчета Я младших Триггеров делителя 7 определяет требуемую частоту следования импульсов внутри поддиапазона (точная шкала). Разропдающий потении ал с второго выхода блока 1 (эткрывает элемент И 14, с вы-хода которого па первый вход счетщ1ка 15 поcTjmёйют а гнаяы об окончании каж.п.сго ло еле дующего периода входного сигнала., образом, счетчик 15 подсчитьша гг число периодов i .- , лрошедлшх с момента появления разрешающего потенанала на втором выходе бпока 1, Дешифратор 16 последоват-элгзно открывает тот из элемегггов И блока 17, номер которого соответствует коду в счетчике 15. При достртжонии HHCiia периодов величины соответс.гвующий элемент И из блока 17 сзармирует корректируюш.ий сигнал, который устекевливает устройство в положение, исходное лпп генерирования (формирования) ;зылопм-л импульсов, Если, например, на нулевчЮ P-Q из входных клемм (, ., ) парэд началом работы был подан разрешаялдкй погеициал, то нулевой (исходный ) код счетчика 15 открывает нулевой элемент И пз блока 17, а поэтому (чероз элемент ИЛИ 18) элемент И 19 открыт по nanDOMv входу в исходном состоянии. Тогда первый жо сигнал, аЬормированный формирова1 елем 13, пройдет по второму входу через элемеит И 19 и поступит на дополнительные входь элементов 8 и 11, а rfAKjKG ifu установочный вход счетчика 15, Устройство готово для дальнейшего (Ьормирозакия кмпульсов. Если в исходном состоянии .возбуждена первая входная клемма 6-, то корпзектируюодий сигнап вырабатьшаетсЕ в момеш пргосода второго импульсе с уюрмировшеля 13 и т.д. Таким образом, введение дополнительных функциональньк блоков и связей ПОВЬРшает точность функционирования преобразователя период-частота, а следовательиорасширяет и область его использования. формула изобретени Преобразоввггепь период-частота по авт св. hft 546102, отцичающийся тем, что, с целью повышения точности преобразования, в него дополнительно введены формирователь импульсов, два элемента И и последовательно соединенные счетчик, дешифратор, блок элементов И и элемент ИЛИ, причем входная шина устройства соединена через формирователь импульсов с первым входом первого до742 полшггельного элемента И, второй вход которого подключен к второму выходу входного (блока, выход первого ДОПОЛНР тельного элемента И соединен со счетным входом дополнительного- счетчика и первым входом второго дополнительного элемента И, второй вход которого подключен к выходу дополнительного элемента ИЛИ, установочный вход дополнительного счетчика соединен с выходом второго допопнитель ного элемента И и дополнительными входами первого и второго элементов ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь период-частота | 1975 |

|

SU546102A1 |

| Цифроаналоговый измеритель средней частоты | 1991 |

|

SU1775678A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Устройство для управления двухтактным преобразователем напряжения | 1987 |

|

SU1624635A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Преобразователь сдвига фаз в код | 1980 |

|

SU943599A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU875642A1 |

| Устройство для преобразования частоты | 1981 |

|

SU1008904A1 |

| Функциональный преобразователь | 1981 |

|

SU960838A1 |

| Функциональный генератор | 1983 |

|

SU1141427A1 |

Авторы

Даты

1980-06-30—Публикация

1977-12-01—Подача