(54) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1988 |

|

SU1562908A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2023302C1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1508272A1 |

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1987 |

|

SU1525726A1 |

| Преобразователь перемещения в код | 1983 |

|

SU1129635A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство для анализа формы непериодических импульсных и частотных сигналов | 1988 |

|

SU1649471A1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для функционального преобразования частотно-импульсных сигналов.

Известно устройство для функционального преобразования частотных и временных сигналов, состоящее из генератора импульсов, элемента И, ключа, пересчетной схемы, системы импульсно-пересчет- ных ключей, управляющего счетчика, основного счетчика и блока задания началЕз- ных условий аппроксимации, собранного по схеме дешифратора, выход генератора импульсов через ключ соединен с входом пересчетной схемы .

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее генератор импульсов, последовательно соединенные элемент И, один вход которого соединен с выходом генератора импульсов, а другой вход является входом устройства и пересчетный блок, разрядные выходы которого соединены с первыми входами группы элемен-

тов и, другие входы которых соединены с разр$щными выходами управляющего счетчика, а выходы подключены через последовательно соединенные элемент ИЛИ и .элемент И к входам счетчика резуль.- тата, выход которого соединен с входом блока задания граничных условий, разрядные выходы которого подключены к входам управляющего счетчика .2 .

Недостатком известных устройств явtoляется ограниченность класса воспроизводимых функциональных зависимостей и их частотного диапазона. В известных устройствах воспроизведение функциональных зависимостей реализуется путем кусочно линейной или кусочно-экспоненциальной аппроксимации. Невозможность изменения характера аппроксимации ограничивает класс восрроизводимых функциональных зависимостей. Частотный диапазон воспрогоизводимых функциональных зависимостей ограничен из-за того, что устройство не обеспечивает пропорциональности между частотой входного сигнала и частотой счет39608384

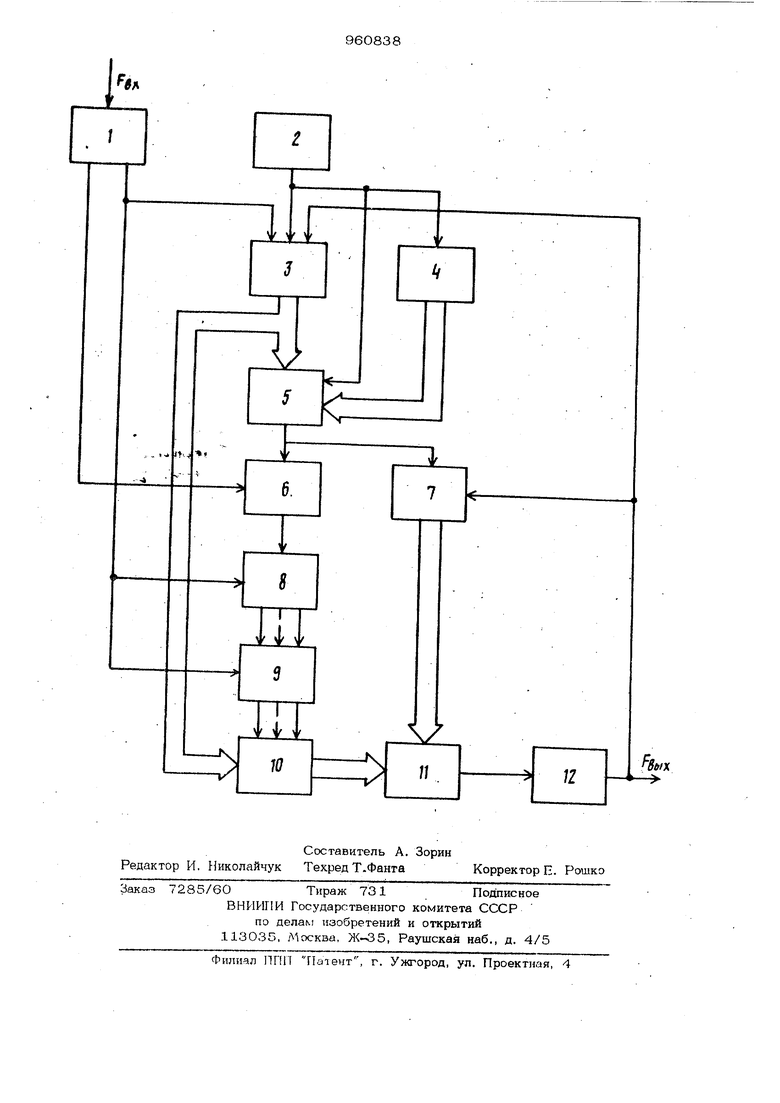

ных импупьсов (генератора) вследствие .Функциональный преобразователь содерпостоянства последней, что приводит кжит блок 1 синхронизации, генератор 2 автоматическому росту погрешности преобрйзования частотных сигналов минималь ной величины (нижней границы частотного диапазона), при преобразовании максималь ных 4acTOTHtix сигналов (верхней границы частотного диапазона) с заданной точностью,- . Иелью изобретения является расширёние класса решаемых задач за счет возможности изменения вида аппроксимирующей зависимости. Поставленная цель достигается тем, ; что в функциональный преобразователь, содержащий генератор импульсов, счетчик первый делитель частоты и элемент И, вы ход которого соединен со счетным входом .первого делителя частоты, дополнительно введены второй делитель частоты, формирователь импульсов, схема сравнения, блок памяти, регистр, коммутатор, преобразователь последовательного кода в параллельный и блок синхронизации, вход которого Соединен с входом преобразователя, первый выход блока синхронизации соединен с первым входом элемента И, второй вход которого соединен с выходом коммутатора и счетным входом счетчика, установочный вход которого соединен с выходом формирователя импульсов выходом преобразователя и установочным входом преобразователя последовательного кода в параллельный, управляющий и информационный вхЪды которого соединены соответственно с вторым выходом блока .синхронизации и выходом генератора импульсов, выход преобразователя последовательного кода в параллельный соединен с входом старших разрядов адреса блока памяти и управляющим входом коммутатора, информационный вход которого соединен с выходами генератора импульсов и второго делителя частоты, вход которого соединен с выходом генератора импульсов выход первого делителя частоты соединен с информационным входом регистра, управ ляющий вход которого соединен с вторым выходом блока синхронизации и управляющим входом первого делителя частоты, вы ход регистра соединен о входом младщих разрядов адреса блока памяти, выход которого соединен с первым входом схемы сравнения, второй вход и выход которой соединены соответственно с выходом счет чика и входом формирователя импульсов. На чертеже представлена блок-схема преобразователя. импульсов, преобразователь 3 последовательного кода в параллельный, делитель 4 частоты, коммутатор 5, элемент И 6, счетчик 7, делитель 8 частоты, регистр 9, блок 10 памяти, схему 11 сравнения и формирователь 12 импульсов. Устройство работает следующим образом. На вход блока 1 синхронизации посту„ают входные, импульсы частотой FBX , а с двух выходов снимаются противофазно сигналы в виде меандра, длительность положительного и отрицательного полупериода которого равна периоду входного р- . При разрешающем сигнала потенциале на, первом выходе блока 1 синхронизации открывается элемент И б .на время Т и импульсы частотой f р от генераторш 2.импульсов через делитель 4 частоты и коммутатор 5 поступают на счетный вход делителя 8. Частота счетных импульсов на выходе, коммутатора 5 опеределяется исходя из частотного диапазона входных сигналов (F - и заданной точности преобразования. Весь диапазон измерения входной частоты разбивается на И поддиапазонов, каждому из которых соответствует такая частота счетных импульсов, что сохраняются пропорции между этой частотой и частотой входного сигнала, определяемые точностными требованиями. Час.тота счетных импульсов для ( У) - 1)-го поддиапазона определяегся по формуле где И GN, N - множество натуральных чисел; {Q- частота генератора импульсов. Это осуществляется следующим обра- зом.; Делитель 4 частоты из частоты импульсов fo генератора 2 импульсов формирует ( У - 1)-импульсную ,Jlocлeдoвaтeльнocть с частотами ,, f o-Z . оу., орые совместно с частотой €(, генератора 2 поступают на информационный вход коммутатора 5. Выбор частоты счетных импульсов, соответствующих текущему поддиапазону входной частоты, происходит в коммутаторе 5,. на выход которого проходит сигнал с того информационного входа, номер которого соответствует коду на его управляющем входе. Управляюишй код формируется в преобразователе 3, состоящем из последовательно соединенных счетчика и регистра. Код формируется путем отсчета импульсов о , поступающих с генератора .1, счетчиком преобразователя 3 при разрещаюшем потенциале на втором выходе блока 1 синхронизации, т.е. в течение периода входного сигнала Т . В регистре преобразователя .3 запоминается состояние старших разрядов счетчика в конце периода Т . При разрешающем потенциале на втором выходе блока 1 синхронизации содержимое делителя 8 переписывается в регистр 9, а делитель 8 обнуляется. Таким образом, в делителе 8 формируется число N , которое является кодом входной частоты FeytВ ячейках блока 10 памяти записаны числа F , соответствующие N, которые являются кодами значений координат точек новой функш1ональной зависимости, т. е. выходной частоты вь|Х регистра 9 код соответствующей входной частоты поступает на младшие адресные входы блока 10 памяти. На старшие адресные входы бло- ка 10 памяти поступает код с преобразователя 3. Число N выбирается из блока 10 памяти и его код, являющийся коэффициентом деления счетчика 7, поступает на вход схемы 11 сравнения, на другой вход которой пост т1ает код со счетчика 7 соединенного счетным входом с выходом коммутатора 5. В схеме 11 сравнения код числа N поразрядно сравнивается с кодом со счетчика 7 и при условии равенства на вход формирователя 12 импульсов пост пает разрешающий сигнал. По этому сигналу в формирователе 12 импульсов формируется короткий импульс с длительностью , где 1Г - длительность импульса, который поступает на выход ., преобразователя и является сигналом обратной связи. Он обнуляет с четчик 7 и устанавливает в исходное состояние преобразователь 3. Начинается следующий .цикл отсчета импульсов счетчика 7, который также заканчивается формированием короткого импульса на выходе устройства и т. д. Таким образом, на выходе устройства формируется импульсный CHrHajj, частота которого соответствует значению координаты точки воспроизводимой функциональной зависимости. Устройство позволяет посредством смены информации в блоке 10 памяти реализовать произвольную функ циональную зависимость в расширенном диапазоне частот за счет сохранения пропор ций между частотой счетных импульсов и частотой входного сигнала, определяемых точностными требованиями. Формула изобретения Функциональный преобразователь, содержащий генератор импульсов, счетчик, первый делитель частоты и элемент И, выход которого соединен со счетным входом первого делителя частоты, отличающийся тем, что, с целью расширения класса решаемых задач за счет возможности изменения вида аппроксимирующей зависимости, в него введены второй делитель частоты, формирователь импульсов, схема сравнения, блок памяти, регистр, коммутатор, преобразователь последовательного кода в параллельный и . блок синхронизации, вход которого соединен с входом преобразователя, первый вь1ход блока синхронизации соединен с первым входом элемента И, второй вход которого соединен с выходом коммутатора и счетным, входом счетчика, установочный вход которого соединен с выходом формирователя импульсов, выходом преобразователя и установочным входом преобразователя последовательного-кода в параллельный,/ управляющий и информационный входы которого соединены соответственно с вторым выходом блока синхронизации и выходом генератора импульсов, выход преобразователя последовательного кода в параллельный соединен с входом старших разрядов адреса блока памяти и управляющим входом коммутатора, информационный вход которого соединен с выходами генератора импульсов и второго делителя частоты, вход которого соединен с выходом генератора импульсов, выход первого делителя частоты соединен с информационным входом регистра, управляющий вход которого соединен с вторым выходом блока синхронизации и управляющим входом первого делителя частоты, выход регистра соединен с входом младщих разрядов адреса блока памяти, выход которого соединен с первым входом схемы сравнения, второй вход и выход которой соединены соответственно с выходом счетчика и входом формирователя ИМПуЛЕзСОВ. Источники информащ1и, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 348994, кл. G 06 F 15/31, 1971. 2.Авторское свидетельство СССР № 561189, кл. G06 F 15/31., 1976 (прототип).

Авторы

Даты

1982-09-23—Публикация

1981-03-26—Подача