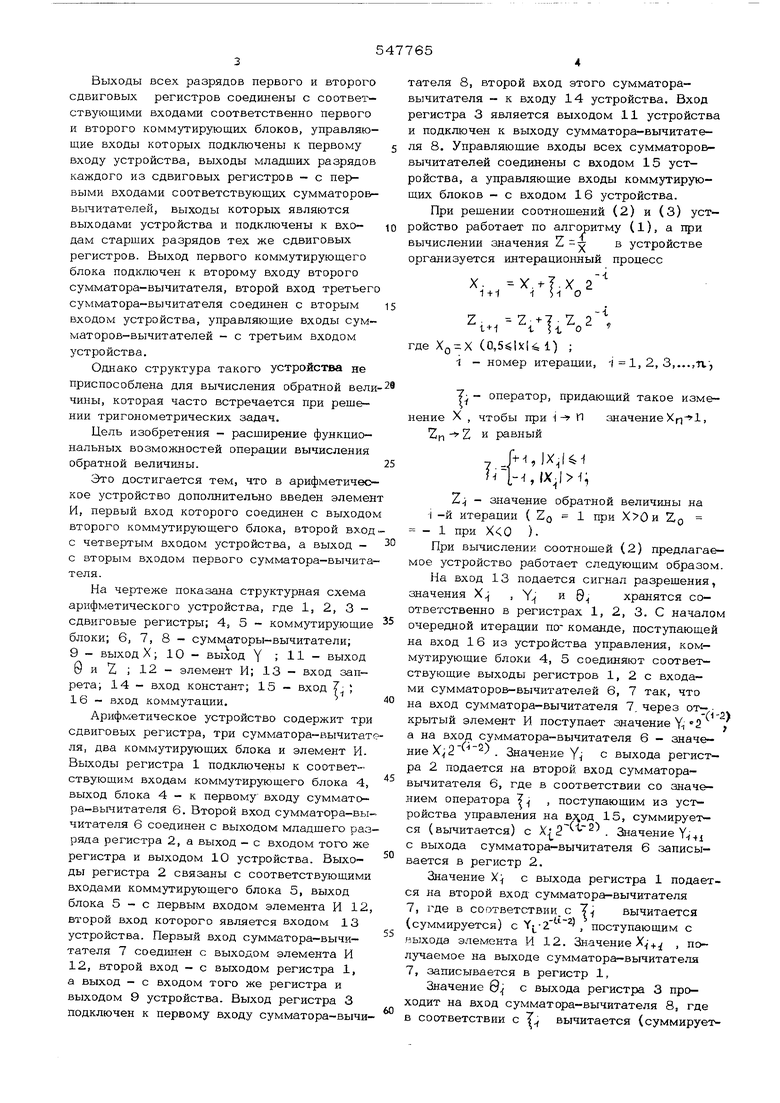

Изобретение относится к области вычислительной техники. Известны арифметические устройства, ра ботающие с информацией, представленной в виде векторов, предназначенные для решени задач, содержащих большое число тригономе рических функций jl, 2, Гз1 . Эти арифметич кие устройства состоят из сдвиговых регис ров, сумматоров-вычитателей и коммутирую щих блоков. Недостатком таких устройств является отсутствие в их наборе операции вычисления обратной величины. Наиболее близкое по технической сущнос ти к изобретению арифметическое устройств з реализует алгоритм Волдера Y. - Y.tT.X. 1+1 1 и 1 X. -X.-T.Y.2 i-t--f 1 М 1 9- 0.-.. 1+-I 1 ) и позволяет вычислять ( .O, (Xf05A-Y S nЛ). R KVx + arcto LL 1 X В предыдущих выражениях X-j ,V 90-) - значения координат и угла на 1 -и итерации; ./ - функция, показывающая направение вращения и равная для соотнощений 2.) .- (4) ля соотношений (3) 1..) 5) - угловая постоянная, равная к - коэффициент общего удлинения ектора, равный произведению коэффициентов длинения на каждой итерации к. п (G) i--2 X,Y, А - начальные данные; - - номера итерации , 3,.... Это арифметическое устройство содержит ри сдвиговых регистра, три сумматора- ычитателя и два коммутирующих блока. Выходы всех разрядов первого и второго сдвиговых регистров соединены с соответствующими входами соответственно первого и второго коммутирующих блоков, управляющие входы которых подключены к первому входу устройства, выходы младших разрядов каждого из сдвиговых регистров - с первыми входами соответствующих сумматороввычитателей, выходы которых являются выходами устройства и подключены к входам старших разрядов тех же сдвиговых регистров. Выход первого коммутирующего блока подключен к второму входу второго сумматора-вычитателя, второй вход третьег сумматора-вычитателя соединен с вторым входом устройства, управляющие входы сумматоров-вычитателей - с третьим входом устройства. Однако структура такого устройства не приспособлена для вычисления обратной вели чины, которая часто встречается при решении тригонометрических задач. Цель изобретения - расщирение функциональных возможностей операции вычисления обратной величины. Это достигается тем, что в арифметическое устройство дополнительно введен элемен И, первый вход которого соединен с выходо второго коммутирующего блока, второй вход с четвертым входом устройства, а выход с вторым входом первого сумматора-вычита теля. На чертеже показана структурная схема арифметического устройства, где 1, 2, 3 сдвиговые регистры; 4, 5 - коммутирующие блоки; 6, 7, 8 - сумматоры-вычитатели; 9 - выход X; 10 - выход Y ; 11 - выход 0 и 2 ; 12 - элемент И; 13 - вход запрета; 14 - вход констант; 15 - вход 7 ; 16 - вход коммутации. Арифметическое устройство содержит три сдвиговых регистра, три сумматора-вычитат ля, два коммутирующих блока и элемент И. Выходы регистра 1 подключены к соответствующим входам коммутирующего блока 4, выход блока 4 - к первому входу сумматора-вьлитателя 6. Второй вход сумматора-вы читателя 6 соединен с выходом младшего раз ряда регистра 2, а выход - с входом того же регистра и выходом 10 устройства. Выходы регистра 2 связаны с соответствующими входами коммутирующего блока 5, выход блока 5 - с первым входом элемента И 12 второй вход которого является входом 13 устройства. Первый вход сумматора-вычи- тателя 7 соединен с выходом элемента И 12, второй вход - с выходом регистра 1, а выход - с входом того же регистра и выходом 9 устройства. Выход регистра 3 подключен к первому входу сумматора-вычи ателя 8, второй вход этого сумматораычитателя - к входу 14 устройства. Вход егистра 3 является выходом 11 устройства подключен к выходу сумматора-вычитатея 8. Управляющие входы всех сумматоров ычитателей соединены с входом 15 устойства, а управляющие входы коммутируюих блоков - с входом 16 устройства. При рещении соотношений (2) и (З) устойство работает но алгоритму (1), а при в устройстве ычислении значения организуется интерацио1шый процесс -У.Т.Х 2 1 и о XQ-X (0,5$lJ(i4i) i - номер итерации, -j 1, 2, 3,...,TL, 7- - оператор, придающий такое измеX , чтобы при -1- П значение , Z и равный r+H,Jx,K ,, Z - значение обратной величины на -i -и итерации ( ZQ 1 при ZQ - 1 при ). При вычислении ооотношей (2) предлагаемое устройство работает следующим образом. На вход 13 подается сигнал разрешения, значения X. хранятся соответственно в регистрах 1, 2, 3. С началом очередной итерации по- команде, поступающей на вход 16 из устройства управления, коммутирующие блоки 4, 5 соединяют соответствующие выходы регистров 1, 2 с входами сумматоров-вычитателей 6, 7 так, что на вход сумматора-вычитателя 7, через от- крытый элемент И поступает значение , а на вход сумматора-вычитателя 6 - значение Х 2 ) . Значение Y-j с выхода регистра 2 подается на второй вход сумматоравычитателя 6, где в соответствии со значением оператора .j , поступающим из устройства управления на 15, суммируется (вычитается) с . Значение с выхода сумматора-вычитателя 6 записывается в регистр 2. Значение X; с выхода регистра 1 подается на второй вход сумматора-вычитателя 7, где в соответствии, с 7 вычитается (суммируется) с , поступающим с выхода элемента И 12. Значение . , получаемое на выходе сумматора-вычитателя 7, записывается в регистр 1, Значение 0 с выхода регистра 3 проходит на вход сумматора-вычитателя 8, где в соответствии с вычитается (суммируется) с угловой постоянной Л , поступающей по входу 14 из запоминающего устрой ства на второй вход сумматора-вычитателя 8. Значение , получаемое на выходе сумматора-вычитателя 8, записывается в регистр 3 и по выходу 11 поступает в устройство, где используется для определения . Процесс повторяется до вьшолнения заданного количества итераций. В конце oneрации результаты , Уп+ч«9nti могут быть выведены соответственно по линиям 9, 10, 11. При вычислении соотношений (З) работа арифметического устройства аналогична ра- боте в режиме вычисления соотнощений (2) с той разницей, что значение YJ получается как функция знака , снимаемого в устройство управления с выхода 10, При вычислении величины Z -i значения YQ , Х и Z хранятся соответственно в регистрах 1, 2, 3, а на вход 13 элемента И 12 поступает сигнал запрета. С началом очередной итерации происходит следующее. По команде из устройства управления по входу 16 коммутирующий блок 4 соединяет соответствующие выходы регистра 1 с вторым входом сумматора-вычитателя 6 таким образом, что на вход сумматора-вычитателя поступает значение Хр 2 , которое в соответствии с складывается (вычитается со значением Х. из регистра 2. Значение f-j с выхода сумматора-вычитателя за писывается в регистр 2 и поступает по выходу 10 в устройство управления для определения значения . Значение из регистра 3 поступает на вход сумматора-вычитателя 8, где к нему в соответствии с - . прибавляет ся (вычитается) величина 2 попадающая на вход 14 из запоминающего устройст ва. Значение УО с выхода регистра 1 через сумматор-вычитатель 7 без изменений снов перезаписывается в регистр 1. На этом итерация заканчивается, и процесс повторяется до выполнения заданного количества итераций, В конце операции результат Z п может быть выведен по линии 11. Эффективность изобретения заключается в расщирении функциональных возможностей арифметического устройства, достигаемом за счет незначительного увеличения затрат оборудования. Формула изобретения Арифметическое устройство, содержащее три сдвиговых регистра, три сумматоравычитателя и два коммутирующих блока, причем выходы всех разрядов первого и второго сдвиговых регистров соединены с соответствующими входами соответственно первого и второго коммутирующих блоков, управляющие входы которых подключены к первому входу устройства, выходы младших разрядов каждого из сдвиговых регистров подключены к первым входам соответствующих сумматоров-вычитателей, выходы которых являются выходами устройства и подключены к входам старщих разрядов тех же сдвиговых регистров, выход первого коммутирующего блока подключен к второму входу второго сумматора-Бычитателя, второй вход третьего сумматора-вычктателя соединен с вторым входом устройства, управляющие входы сумматоров-вычита-т-елей соединены с трсзтьим входом устройства, отличающееся тем, что, с целью расщирения функциональных возможностей устройства, оно содержит элемент И, первый вход которого соед1шен с выходом второго коммутирующего блока, второй вход соединен с четвертым входо.м устройств, а выход - с вторым входом первого сум- матора-вычитателя. Источники информации, принятые во внимание при экспертизе: 1. Авторское свидетельство СССР № 445042, кл. G 06 F 7/38, 1972. 2. Патент Великобритании .№ 1331410, кл. G 4А, 1973. aJ.E.VoEder The CORDIC trigonometric comput-ing techn.q, Transactions onFaectron c CompLttprs, YES-8, № 3, 1959 прототип).

к

i... i

760

t t Г

J4 o-

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU750483A1 |

| Арифметическое устройство | 1979 |

|

SU796844A1 |

| Арифметическое устройство | 1978 |

|

SU746508A1 |

| Арифметическое устройство | 1975 |

|

SU550634A1 |

| Устройство для преобразования компонент тензора | 1978 |

|

SU734703A1 |

| Арифметическое устройство | 2016 |

|

RU2625528C1 |

| Арифметическое устройство | 1982 |

|

SU1022152A1 |

| Арифметическое устройство | 1975 |

|

SU633016A1 |

| Устройство для вычисления обратного кругового синуса | 1973 |

|

SU478313A1 |

| Вычислительное устройство | 1988 |

|

SU1522196A1 |

Авторы

Даты

1977-02-25—Публикация

1975-07-04—Подача