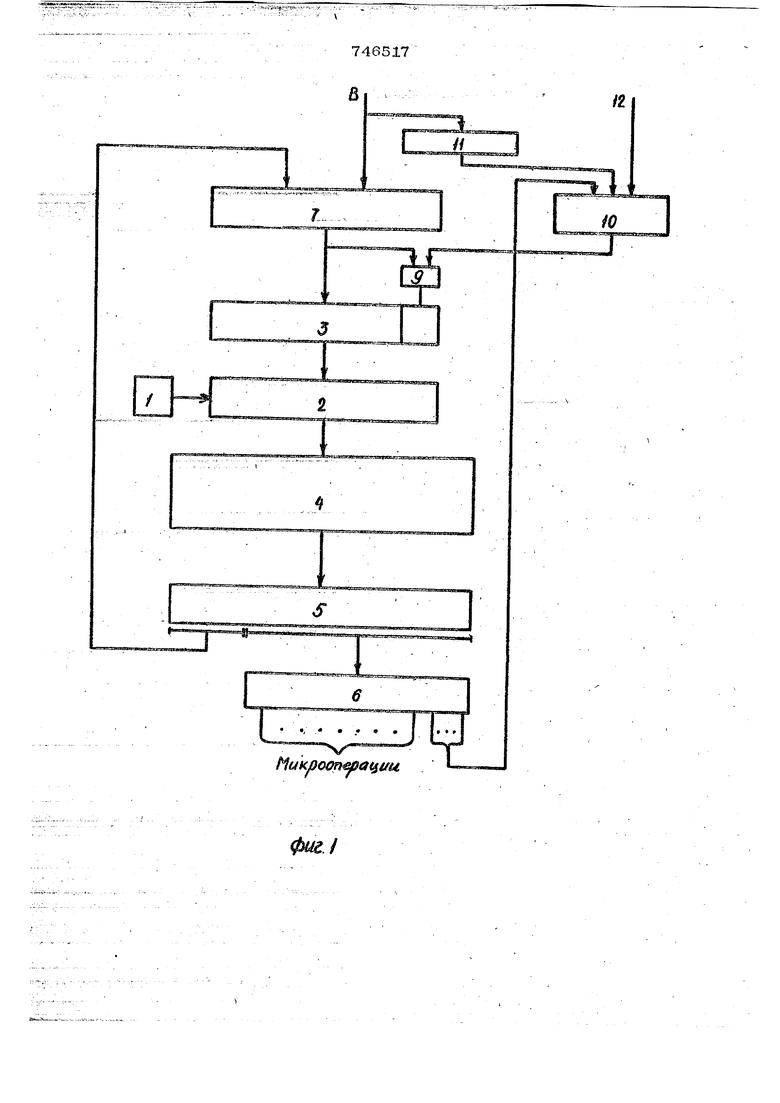

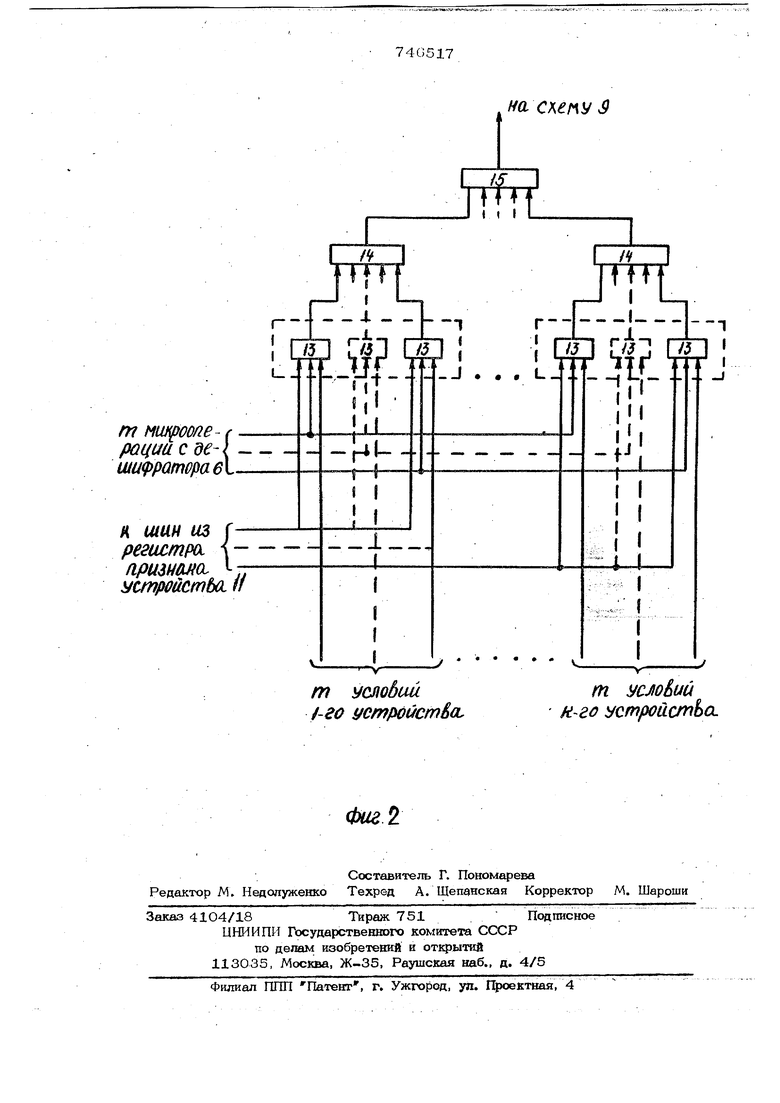

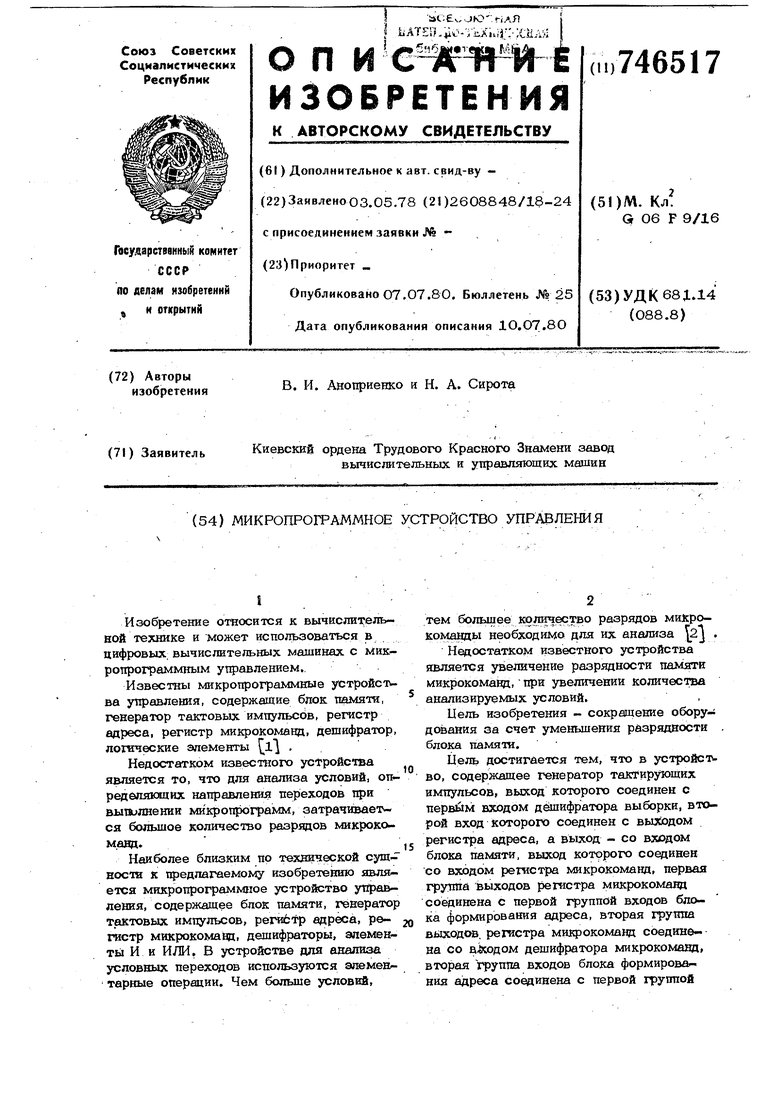

Изобретение относится к вычислительной технике и может использоваться в цифровых вычислительных машинах с микропрограммным управлением.. Известны микропрограммные устройства управления, содержащие блок памяти, генератор тактовых импульсов, регистр адреса, регистр микрокоманд, дешифратор, логические элементы l . Недостатком известного устройства является то, что для анализа условий, оть ределяюших направления переходов при выполнении микропрограмм, затрачивается большое количество разрядов микрокоманд. Наиболее близким по технической сушвостя к предлагаемому изобретению является микропрограммное устройство утфавления, содержащее блок памяти, генератор тактовых импульсов, регибтр адреса, регистр микрокоманд, дешифраторы, элементы И и ИЛИ, В устройстве для анализа условных переходов используются эяемен тарные операции. Чем больше условий. тем большее количество разрядов микрокоманды необходимо для их анализа |2j . Недостатком известного устройства является увеличение разрядности памяти микрокоманд, при увеличении количества анализируемых условий. Цель изобретения - сокраш:ение оборудования за счет уменьшения разрядности блока памяти. Цель достигается тем, что в устройство, содержащее генератор тактирующих импульсов, выход которого соединен с первйм входом дешифратора выборки, второй вход которого соединен с вызй)дом регистра адреса, а выход - со входом блока памяти, выход которого соединен со входом решстра микрокоманд, первая груша выходов регистра микрокоманд соединена с первой группой входов блока формирования адреса, вторая группа выходов, регистра микрокоманд соединена со вводом дешифратора микрокоманд, вторая группа входов блока формирования адреса соединена с первой группой ВХОДОВ устройства, выход блока формирования адреса соединен со входами ртар ших разрядов регистра адреса, введены регистр признака устройства и дешифратор условий, причем вход регистра признака устройства соединен с первой группой входов устройства, а выход - с первым входом дешифратора условий, второй вход которого соединен со второй группой входов устройства, а третий вход - с первой группой выходов дешифратора микрокоманд, вторая группа выходов дешифратора микрокоманд соединена с группой вы ходов устройства, выход дешифратора условий соединен с первым входом элемента ИЛИ, второй вход которого соединен с вь ходом блока фьрмир6)вания адреса, выход элемента ИЛИ соединен с младщими разрядами регистра адреса. На фиг. 1 показана блок-схема микропрограммного устройства управления; на фиг. 2 - блок дешифратора условий. Устройство микропрограммного управле ния содержит генератор 1 тактовых импульсов, выхбд которого соединен с дешифратором 2 выборки, последний связан по ВХОДУ с регистром 3 адреса, а по выходу - с блоком 4 памяти, выхо;} которого связан с регистром 5 микрокоманд. Выход регастра 5 связан с дешифратором 6 микрокоманд и первым входом блока 7 формирования адреса, на второй вход кото рого поступают запросы на микропрограммное обслуживание по входу 8. Выход бло ка 7 связан со входами старших разрядов регистра 3 адреса и через элемент 9 ИЛИ с младшими разрядами регистра 3 адреса. Второй вход 9 ИЛИ соединен с дешифратором 10 условий, первый вход которого соединен с регистром 11 приз нака устройства, второй вход - с дешифратором 6 микрокоманд, а ва третий вход поступают сигналы анализируемых услови по входу 12. На вход репютра 11 посту пают запросы на микропрограммное обслу живание. Предлагаемое устройство сле дующим образом. Генератор 1 тактирующих импульсов выдает сигнал считывания на дешифратор 2 и Происходит выборка микрокоманды из блока 4 памяти по адресу, поступающему из регистра 3. Код выбранвоб микрокоманды устанавливается на регистре 5. Разряды микро команды, определякшие набор мнкроопе рздий, поступают ва |авшифратор 6, расшифровываются и выдаются в виде мшф& операций. Разряды адресной части микрокоманды поступают на блок 7. Блок 7 ормирует код адреса очередной микрокоманды, который заносится в регистр 3. Генератор 1 тактирующих импульсов выдает очередной сигнал считывания и цикл повторяется снова. По запросам на микропрограммное обслуживание устройств, поступающих по входу 8, в регистре 11 устанавливается в единицу триггер, соответствующий тому устройству, чей запрос воспринимается, остальные триггеры сбрасываются. Регистр 11 имеет столько триггеров, сколько устройств обслуживается. По запросам на микропрограммное обслуживание блок 7 формирует начальный адрес микропрограммы обслуживания. Таким образом выполняется переключение на обслуживание соответствующего устройства. Условные переходы выполняются следующим образом. Если выбрана очередная микрокоманда и в ней записана микрооперация анализа условия, то она с дешифратора 6 поступает на дешифратор 10. Содержимое регистра 11 также поступает на дешифратор 10, указывая условие какого устройства необходимо анализировать. При наличии анализируемого условия сигнал с выхода дешифратора 10 через элемент 9 ИЛИ изменяет состояние определенного разряда регистра 3. При отсутствии условия состояние разряда не меняется. Одновременно может анализироваться несколько условий несколькими микрооперациями. В этом случае в регистре 3 изменяется состояние нескольких разрядов. Если необходимо проанализировать по гп условий от К устройств, то дешифратор имеет К групп узлов (фиг. 2). Каждая группа имеет m элементов 13 И и элемент 14 ИЛИ. На первые входы элементов 13 И первой группы заведен первый выход регистра 11 признака устройства. На первые входы элементов 13 И группы заведен к -ый выход регистра 11. На вторые входы элементов 13 И каждой группы заведены с игналы п микроопераций с дешифратора 6. На третьи Входы элементов 13 И соответствующей группы заведены сигналы условий соответствующего устройства. Выходы элементов 13 И через элементы 14, 15 н 9 ИЛИ поступают на вход определенного разряда ретстра 3. При анализе условий по сигналам из регистра 11 признака устройства включается группа узлов того устройства, чь микропрограмма отрабатывается в данны момент. Какое условие необходимо анали зировать в пределах группы определяет микрооперация, поступаклдая с дешифрато ра 6. При наличии анализируемого услов срабатывает соответствующий элемент 1 И и через элементы 14, 15 и 9 ИЛИ изменяется состояние определе шого раз да регистра 3, Предлагаемое устройство микропрограммного управления для микр программного обслуживания нескольких устройств позволяет одними и теми же микрооперациями анализировать условия различных устройств. Если необходимо проанализировать от К устройств по гп условий, то общее ко личество анализируемых условий К Количество двоичных разрядов, необходимое для агтлиза этих условий в известном устройстве С,7 ) в предлагаемом устройстве для анали за такого же количества условий необходимо Р разрядов к p.Cog,(ey,) В предлагаемом устройстве необходимо на Сод(к) двоичных разрядов меньше, чем в известном, что позволяет уменьшить количество разрядов микрокоманды, и следовательно разрядность блока памяти. Формула изобретения Устройство микропрограммного управл ния, содержащее генератор тактирующих импульсов, выход которого соединен с первым входом дешифратора выборки, втон рой вход которого соединен с выходом регистра адреса, а выход - со входом блока памяти, выход Которого соедяяен со входом регистра микрокоманд, первая группа выходов регистра микрокоманд соединена с первой группой входов блока формирования адреса, вторая группа выходов регистра микрокоманд соединена со входом дешифратора микрокоманд, вторая группа входов блока формирования адреса соединена с первой группой входов устройства, выход блока формирсжания адреса соединен со входами старших разрядов регистра адреса, отличающееся тем, что, с целью сокращения оборудования, оно содержит ретстр признака устройства и дешифратор услЬвий, причем вход регистра признака устройства соединен с первой группой входов устройства, а выход - с первым входом дешифратора условий, второй вход которого соединен со второй группой входов устройства, а третий вход - с первой грутгаой выходов дешифратора микрокоманд, вторая труппа выходов дешифратора микрсжоманд соединена с группой вьцсодов устройства, выход дешифратора условий соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом блока формирования адреса, выход элемента ИЛИ соединен с младшими разрядами регистра адреса. Источники информации, принятые во внимание при экспертизе 1.Хассон С. Микропрограммное управление. Мир, 1974, гл. 8,.п. , рис. 16. 2,Авторское свидетельство СССР М 291201, кл. G ОС F 9/1G, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1978 |

|

SU744572A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Мультимикропрограммная управляющая система | 1989 |

|

SU1631542A1 |

| Устройство для восстановления работы процессора | 1984 |

|

SU1191910A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

0./

1

г

ГЮ

т мщоопе- f рации с дс-1 шид ратсраб,.

X ший из регистра,

аризн и ои J. устройстЬа, //

т услобии /-го устроистВси

на 3

if

ггг

( I L

I

-1

/J I I /J

т условии k-го стройстЬа.

Авторы

Даты

1980-07-05—Публикация

1978-05-03—Подача