Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1168936A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1647566A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1059573A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано в качестве управляющей подсистемы в многоуровневых системах управления сбора и обработки информации. Цель изобретения - повышение быстродействия при реализации параллельных асинхронных алгоритмов. Система содержит блоки 1.1-1.N микропрограммного управления, группу 2 элементов И, группу 3 элементов ИЛИ, блок 4 элементов ИЛИ, блок передачи адресов запуска, одно- вибратор 5, элемент И 6. Код операции, выполняемой системой, подается

СП Ј

на вход 7, а сигнал пуска- на вход 8 В процессе работы каждый из блоков 1.1-1.N независимо и параллельно с работой других блоков асинхронно вы- полняет закрепленные за ним участки микропрограммы. Сигналы микроопераций выдаются по выходам 11.1-11.N а состояние казвдого из блоков микропрограммного управления - по выхо- дам 12.1-12.N. Сигналы завершения выполнения выдаваемых микроопераций поступают по входам T0.1-10.N, а логические условия - по входам 9.1- 9.N. Каждый блок микропрограммного

Изобретение относится к автомати- 20 ке и цифровой вычислительной технике и может быть использовано в качестве управляющей подсистемы в многоуровневых системах управления, сбора и об- информации.25

Цель изобретения - повышение быстродействия мультимикропрограммной управляющей системы при реализации параллельных асинхронных алгоритмов т.е. когда между управляющим и управ- 30 ляемым устройствами существуют двусторонние связи. Каждая такая связь реализуется в виде линии, состоящей из прямого и обратного каналов. По прямому каналу устройство управления 35 выдает сигнал - микрооперацию,а по обратному каналу поступает сигнал - событие, подтверждающий завершение выполнения соответствующей микрооперации.40

Реализация параллельных асинхронных микропрограмм, заданных например, с помощью асинхронных блок-схем либо сетей Петри, подразумевает, что соответствующее устройство управления 45 содержит технические средства, в частности, при задании параллельных асинхронных алгоритмов с помощью параллельных асинхронных блок-схем необходимы технические средства для 5д микропрограммирования следующих типов вершин: оператор (выдача микрооперации); условный переход; сборка; бифуркатор; синхронизатор.

Вершина типа сборка - п-ереход к некоторой микрокоманде параллельного участка может быть выполнен с любого другого параллельного участка. Вершина типа бифуркатор - любой

55

управления может запускать параллельные участки микропрограммы в любых других блоках путем передачи соответствующих начальных адресов через блок 4 передачи адресов запуска. Синхронизация параллельно работающих микропрограмм осуществляется путем опроса сигналов шины 13 состояния блоков микропрограммного управления, Признак конца работы системы вырабатывается на выходе 14 при условии, что все блоки микропрограммного управления завершили свою работу. 1 з.п. ф-лы, 10 ил.

0 5

0 5 0

5 д

5

параллельный участок может запускать другие параллельные участки алгоритма. Вершине типа синхронизатор соответствует слияние двух или более параллельных участков и переход к последовательному участку алгорит- ма. Вершины типа синхронизатор могут появляться в любых параллельных ветвях алгоритма асинхронного управления.

Возможность микропрограммирования асинхронных параллельных алгоритмов, сбора и обработки информации посредством реализации алгоритмов с вер шинами типа сборка, бифуркатор, синхронизатор увеличивает быстродействие .

В системе обеспечивается параллельная и независимая работа блоков микропрограммного управления, что позволяет реализовать параллельные алгоритмы управления и обработки информации.

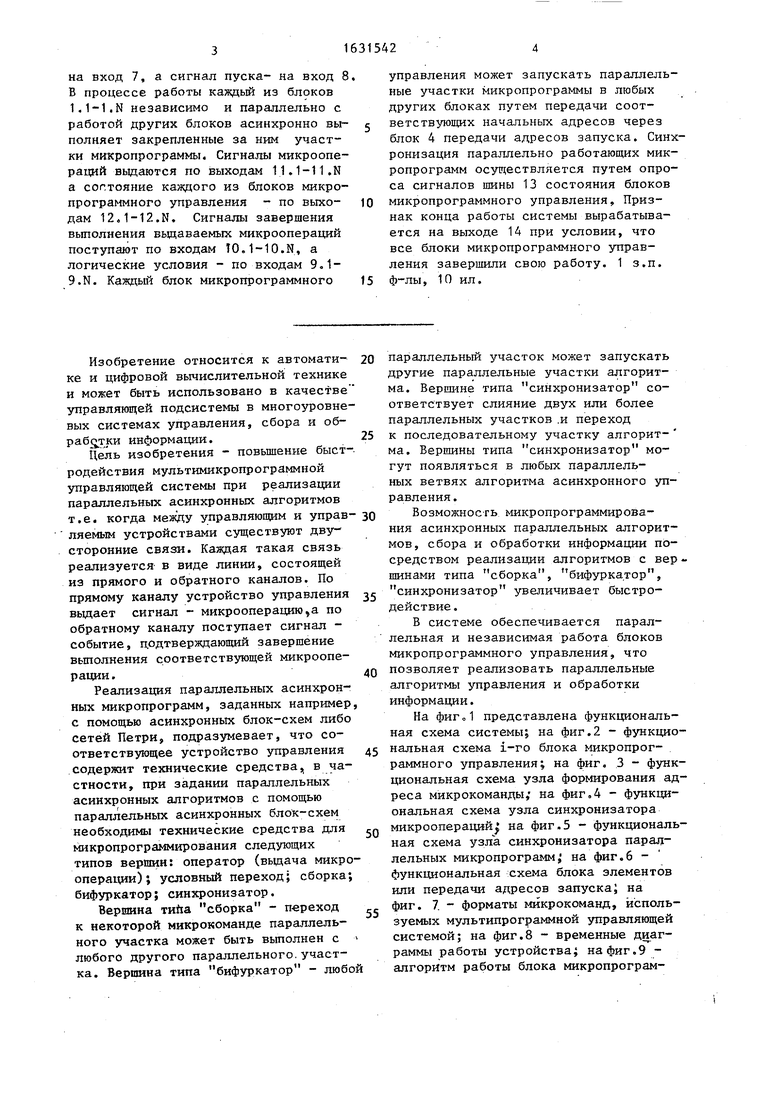

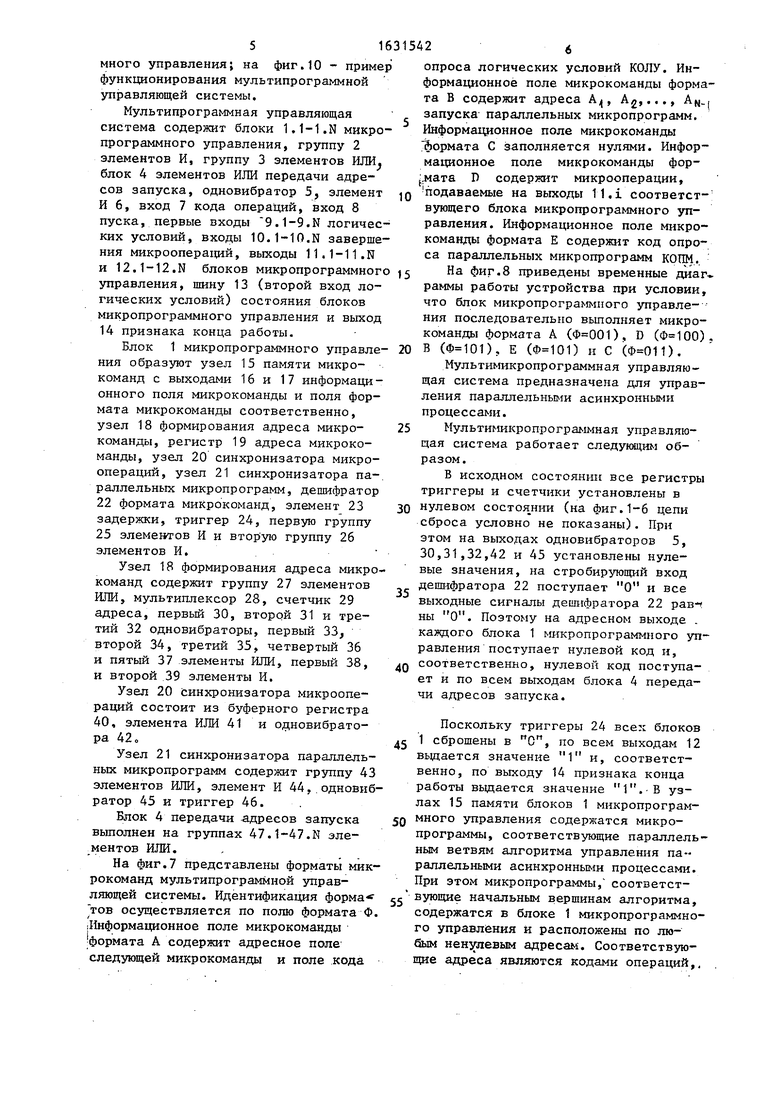

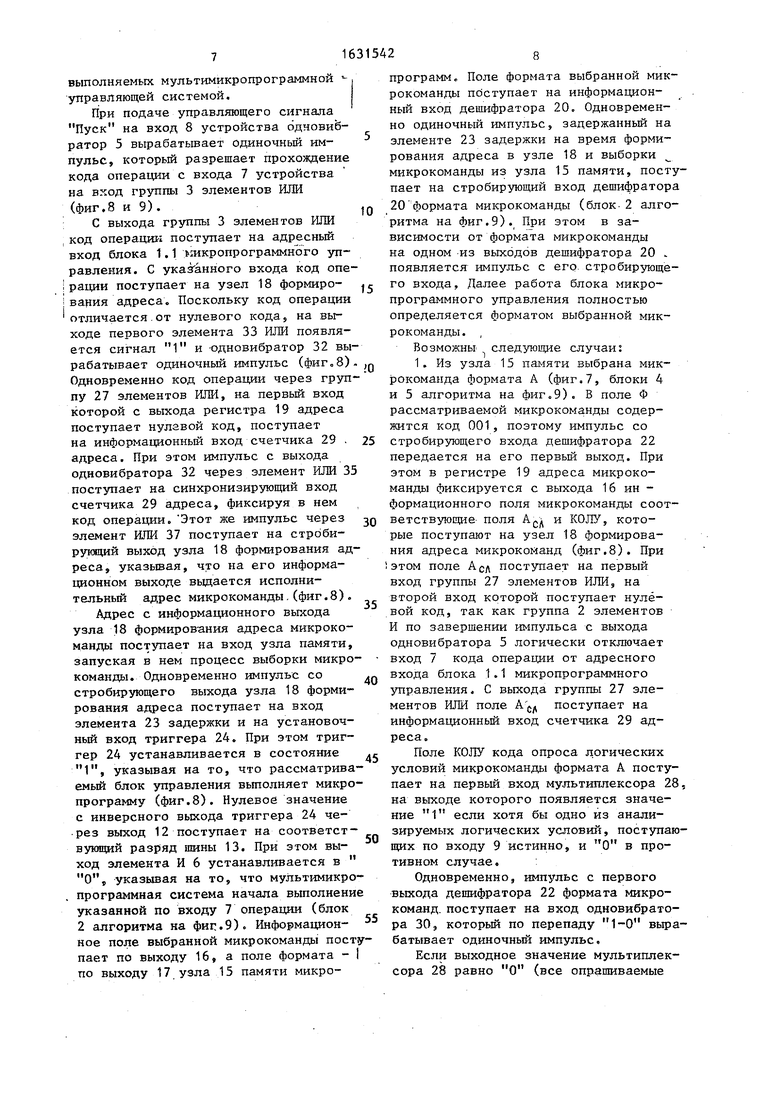

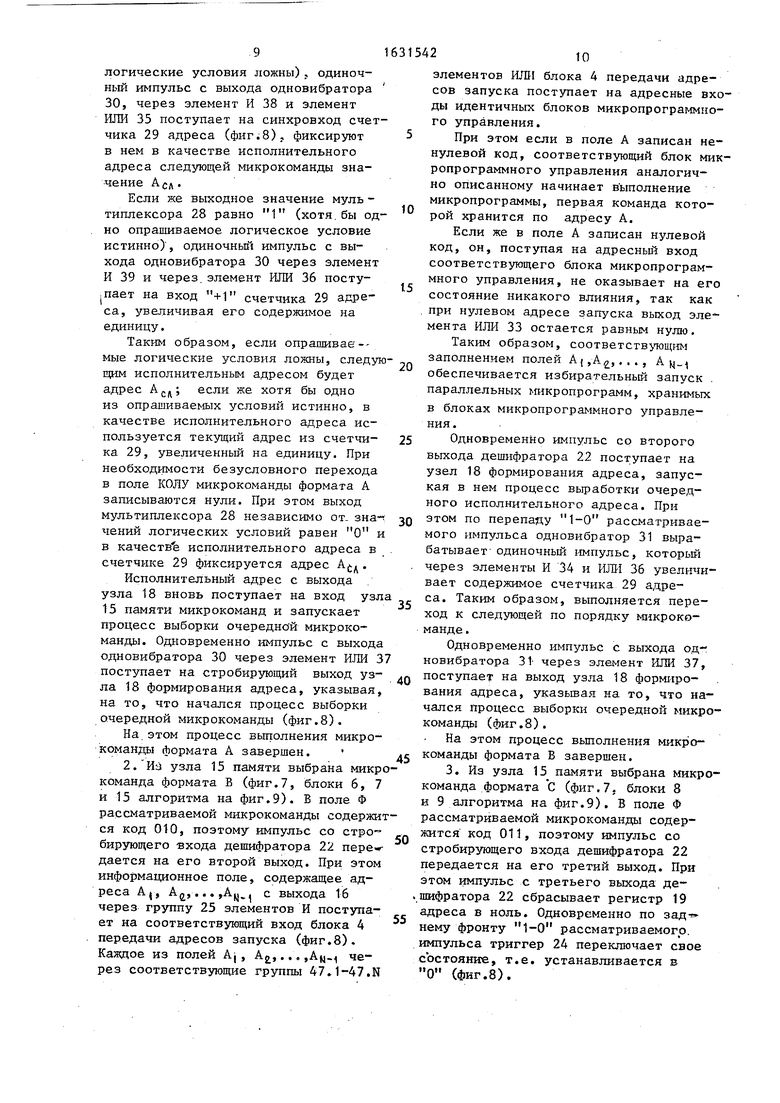

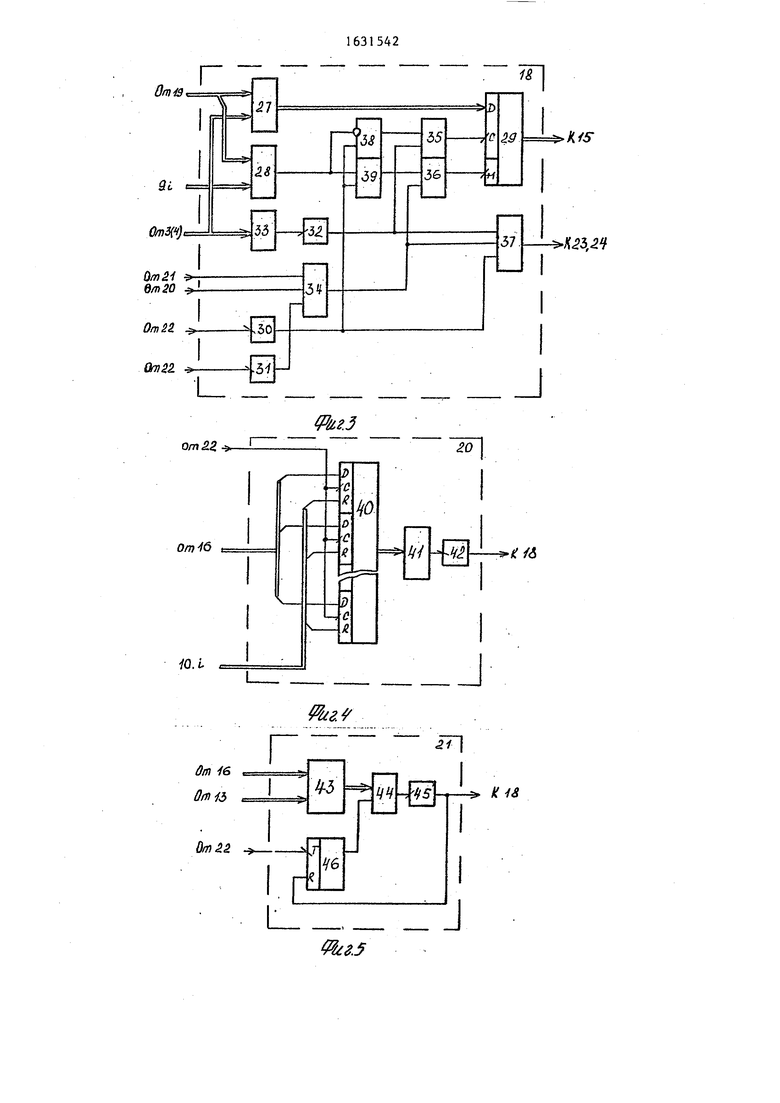

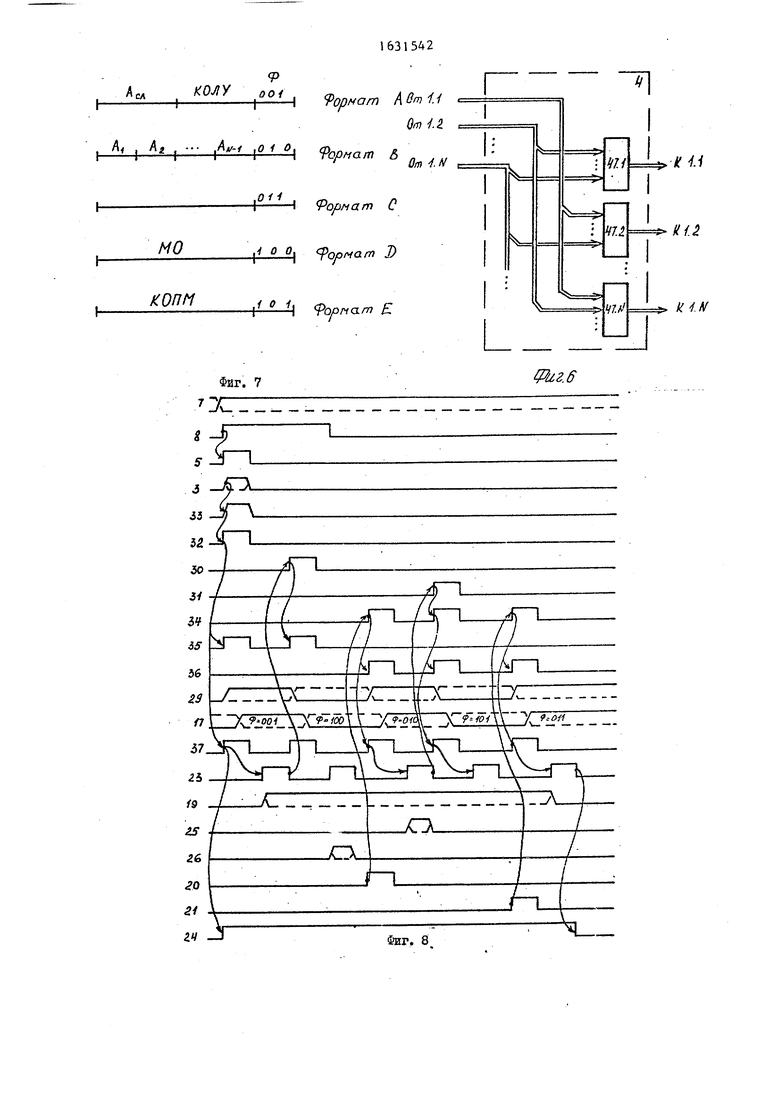

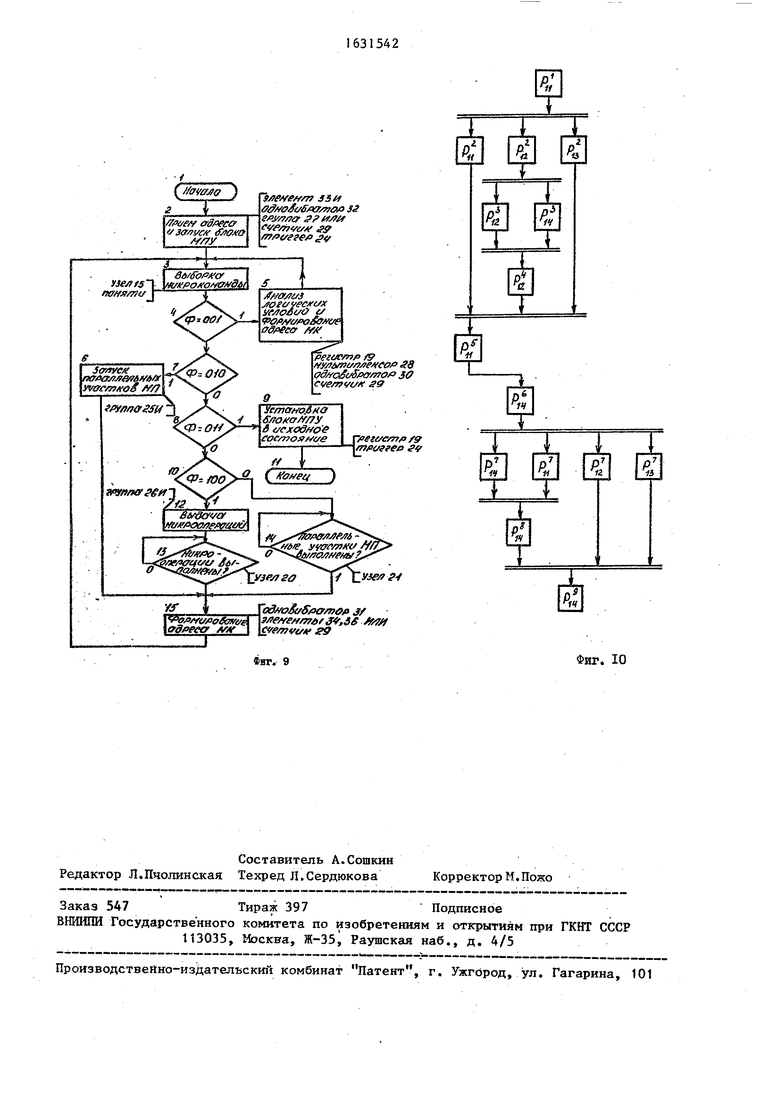

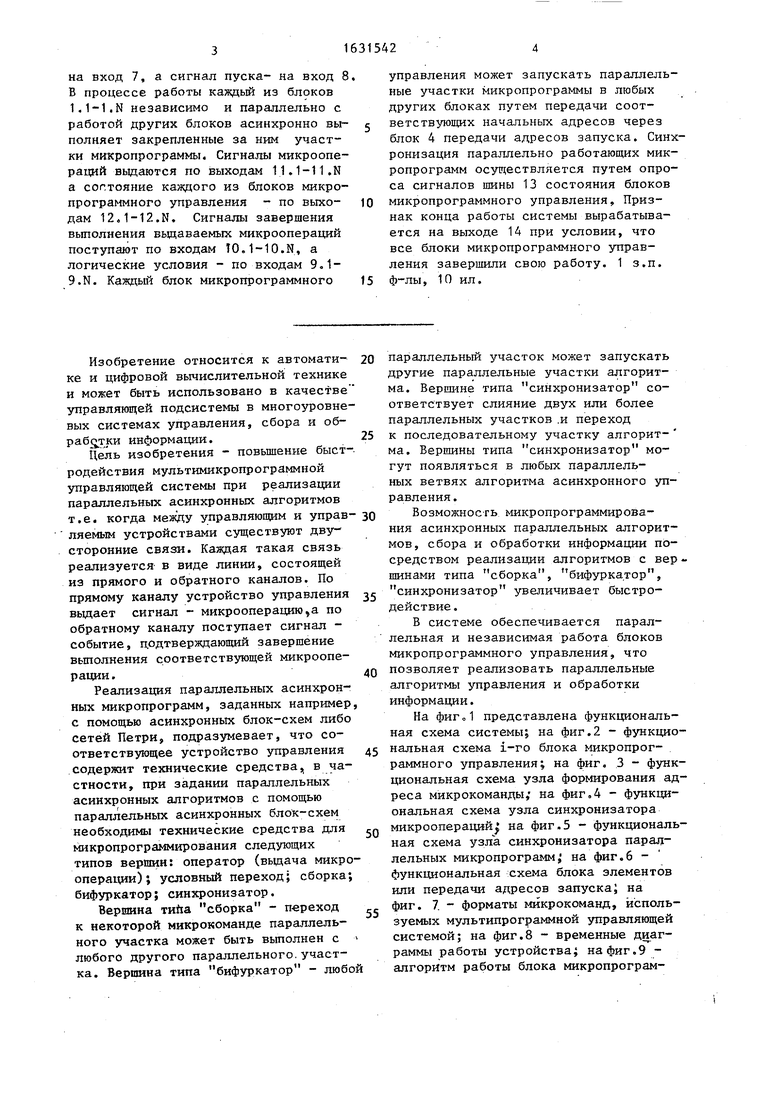

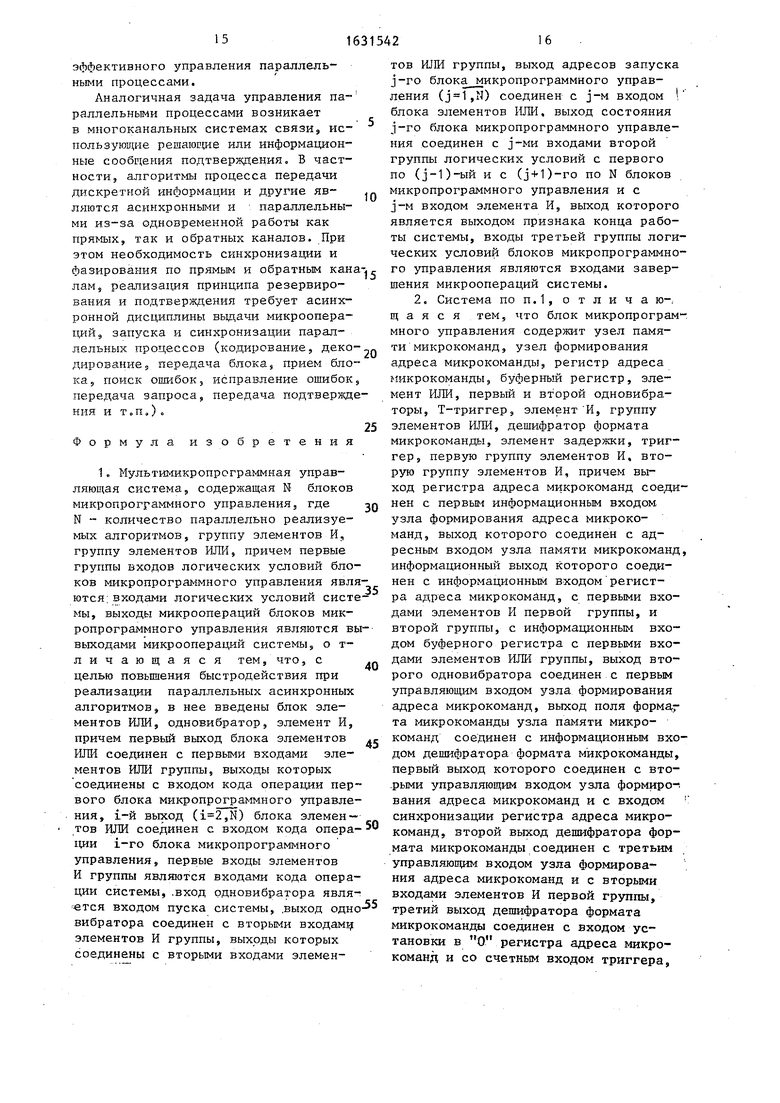

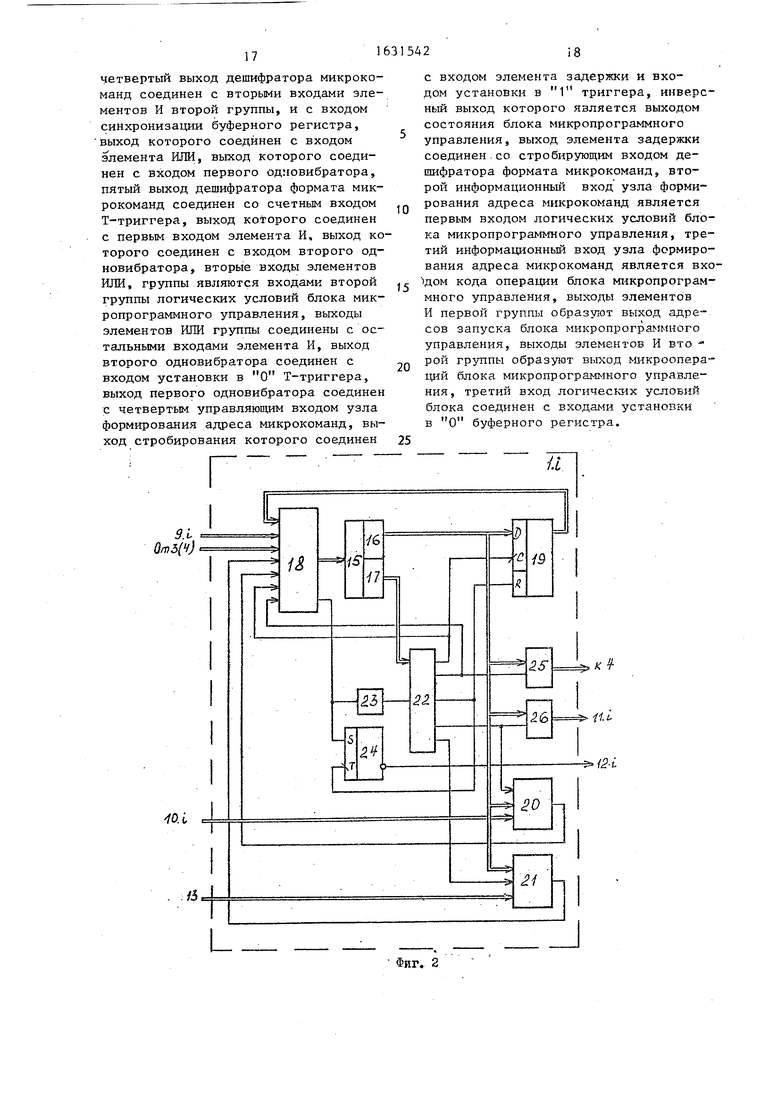

На фиг.,1 представлена функциональная схема системы; на фиг.2 - функциональная схема 1-го блока микропрограммного управления; на фиг, 3 - функциональная схема узла формирования адреса микрокоманды, на фиг,4 - функциональная схема узла синхронизатора микроопераций на фиг.5 - функциональная схема узла синхронизатора параллельных микропрограмму на фиг.6 - функциональная схема блока элементов или передачи адресов запускаJ на фиг. 7 - форматы микрокоманд, используемых мультипрограммной управляющей системой; на фиг.8 - временные диаграммы работы устройства на фиг.9 - алгоритм работы блока микропрограммного управления; на фиг.10 - пример функционирования мультипрограммной управляющей системы.

Мультипрограммная управляющая система содержит блоки 1.1-1.N микропрограммного управления, группу 2 элементов И, группу 3 элементов ИЛИ блок 4 элементов ИЛИ передачи адресов запуска, одновибратор 5, элемент JQ И 6, вход 7 кода операций, вход 8 пуска, первые входы 9.1-9.N логических условий, входы 10.1-10.N завершения микроопераций, выходы 11.1-11.Ы и 12.1-12.N блоков микропрограммного 15 управления, шину 13 (второй вход логических условий) состояния блоков микропрограммного управления и выход 14 признака конца работы.

опроса логических условий КОЛУ. Ин формационное поле микрокоманды фор та В содержит адреса А, АЈ,..., A запуска параллельных микропрограмм Информационное поле микрокоманды формата с заполняется нулями. Инфо мационное поле микрокоманды фор мата D содержит микрооперации, подаваемые на выходы 11.1 соответс вующего блока микропрограммного уп равления. Информационное поле микр команды формата Е содержит код опр са параллельных микропрограмм КОПМ

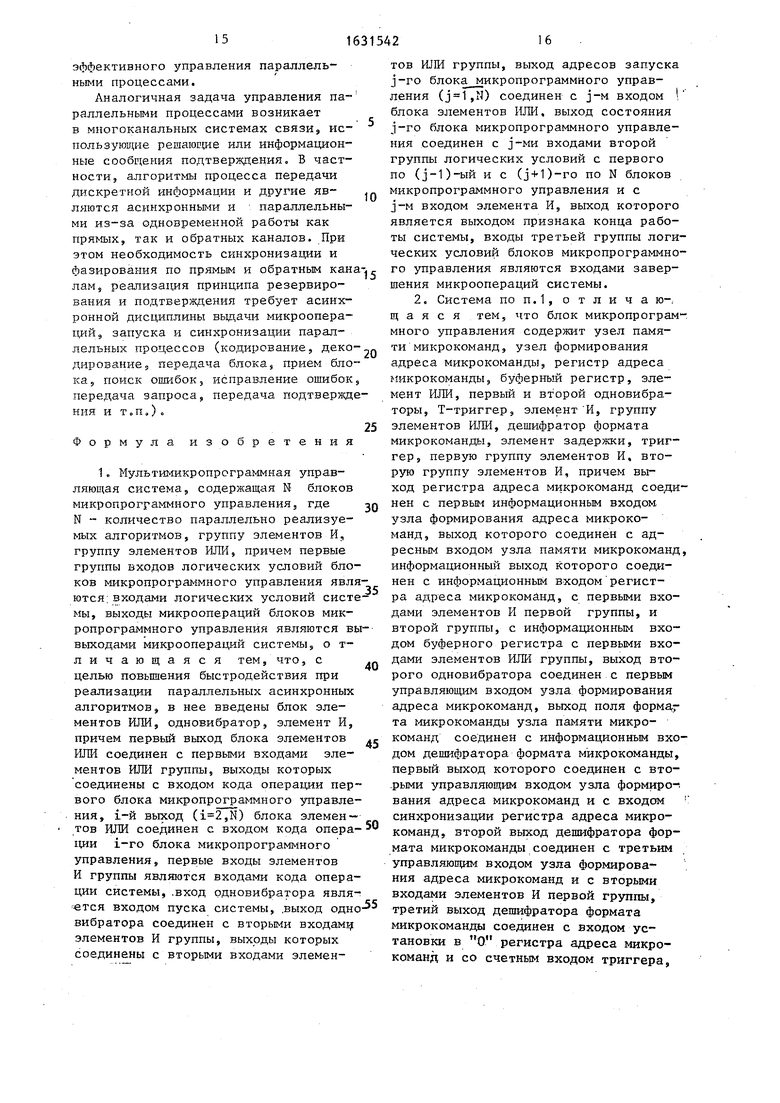

На фиг.8 приведены временные ди раммы работы устройства при услови что блок микропрограммного управле ния последовательно выполняет микр команды формата А (), D (

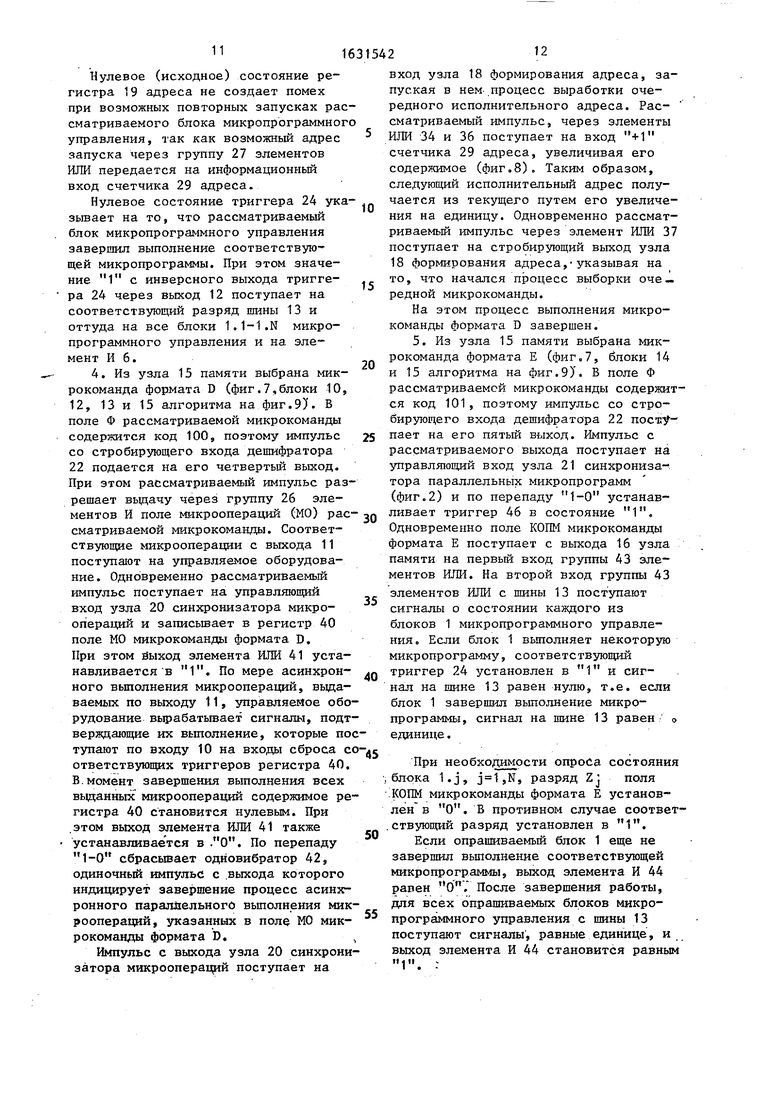

Блок 1 микропрограммного управле- 20 В (), Е () и С ().

ния образуют узел 15 памяти микрокоманд с выходами 16 и 17 информаци - онного поля микрокоманды и поля формата микрокоманды соответственно, узел 18 формирования адреса микрокоманды, регистр 19 адреса микрокоманды, узел 20 синхронизатора микроопераций, узел 21 синхронизатора параллельных микропрограмм, дешифратор 22 формата микрокоманд, элемент 23 задержки, триггер 24, первую группу 25 элементов И и вторую группу 26 элементов И.

Узел 18 формирования адреса микрокоманд содержит группу 27 элементов ИЛИ, мультиплексор 28, счетчик 29 адреса, первый 30, второй 31 и третий 32 одновибраторы, первый 33, второй 34, третий 35, четвертый 36 и пятый 37 элементы ИЛИ, первый 38, и второй 39 элементы И.

Узел 20 синхронизатора микроопераций состоит из буферного регистра 40, элемента ИЛИ 41 и одновибрато- ра 42 о

Узел 21 синхронизатора параллельных микропрограмм содержит группу 43 элементов ИЛИ, элемент И 44, одновибратор 45 и триггер 46.

Блок 4 передачи адресов запуска выполнен на группах 47.1-47.N элементов ИЛИ.

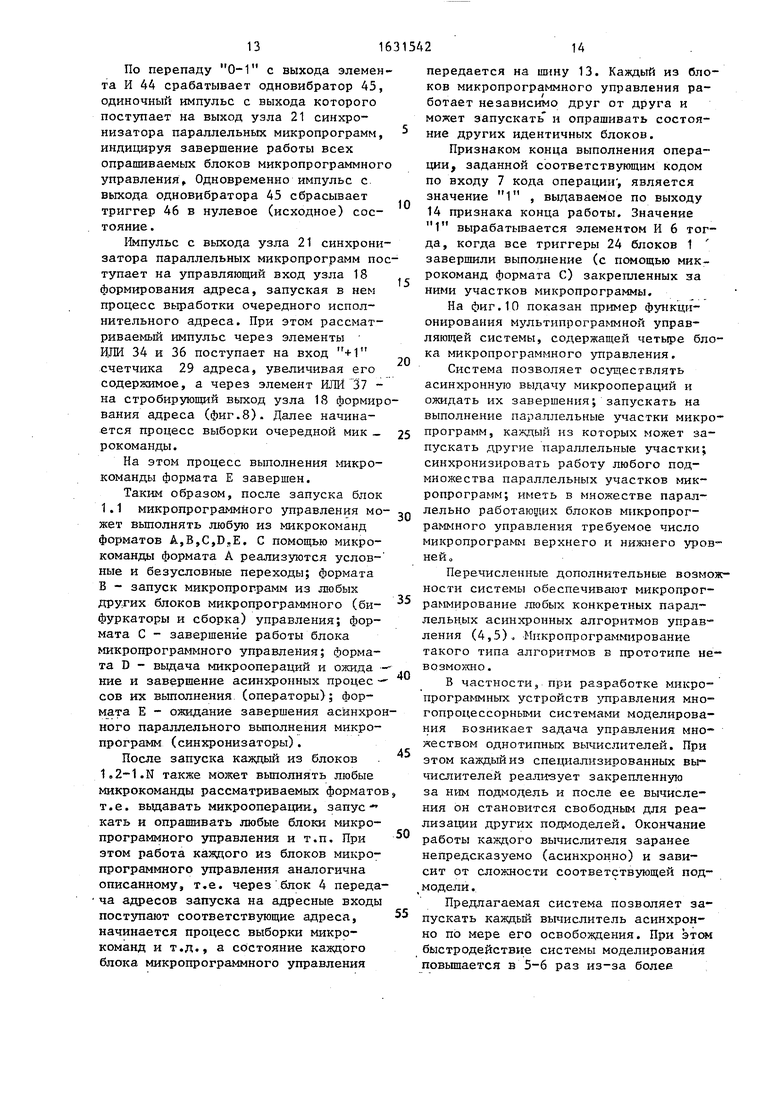

На фиг.7 представлены форматы микрокоманд мультипрограммной управляющей системы. Идентификация форма тов осуществляется по полю формата Ф Информационное поле микрокоманды формата А содержит адресное поле следующей микрокоманды и поле кода

опроса логических условий КОЛУ. Информационное поле микрокоманды формата В содержит адреса А, АЈ,..., AN-J запуска параллельных микропрограмм. Информационное поле микрокоманды формата с заполняется нулями. Информационное поле микрокоманды формата D содержит микрооперации, подаваемые на выходы 11.1 соответствующего блока микропрограммного управления. Информационное поле микрокоманды формата Е содержит код опроса параллельных микропрограмм КОПМ.

На фиг.8 приведены временные диаграммы работы устройства при условии, что блок микропрограммного управления последовательно выполняет микрокоманды формата А (), D (),

5

0

5

0

Мультимикропрограммная управляющая система предназначена для управления параллельными асинхронными процессами.

Мультимикропрограммная управляющая система работает следующим образом.

В исходном состоянии все регистры триггеры и счетчики установлены в нулевом состоянии (на фиг.1-6 цепи сброса условно не показаны). При этом на выходах одновибраторов 5, 30,31,32,42 и 45 установлены нулевые значения, на стробирующий вход дешифратора 22 поступает О и все выходные сигналы дешифратора 22 рав- ны О. Поэтому на адресном выходе . каждого блока 1 микропрограммного управления поступает нулевой код и, соответственно, нулевой код поступает и по всем выходам блока 4 передачи адресов запуска.

Поскольку триггеры 24 всех блоков 1 сброшены в 0й, по всем выходам 12 выдается значение 1 и, соответственно, по выходу 14 признака конца работы выдается значение 1. В узлах 15 памяти блоков 1 микропрограммного управления содержатся микропрограммы, соответствующие параллельным ветвям алгоритма управления параллельными асинхронными процессами. При этом микропрограммы, соответствующие начальным вершинам алгоритма, содержатся в блоке 1 микропрограммного управления и расположены по любим ненулевым адресам. Соответствующие адреса являются кодами операций,.

10

ыполняемых мультимикропрограммной - правляющей системой.

При подаче управляющего сигнала Пуск на вход 8 устройства бдчовиб- атор 5 вырабатывает одиночный имульс, который разрешает прохождение ода операции с входа 7 устройства а вход группы 3 элементов ИЛИ (фиг.8 и 9).

С выхода группы 3 элементов ИЛИ код операции поступает на адресный ход блока 1.1 микропрограммного упавления. С указанного входа код опеации поступает на узел 18 формиро- -, вания адреса. Поскольку код операции отличается от нулевого кода, на выходе первого элемента 33 ИЛИ появляется сигнал 1 и одновибратор 32 вырабатывает одиночный импульс (фиг 8). ,0 Одновременно код операции через труп- пу 27 элементов ИЛИ, на первый вход которой с выхода регистра 19 адреса поступает нулевой код, поступает на информационный вход счетчика 29 25 адреса. При этом импульс с выхода одновибратора 32 через элемент ИЛИ 35 поступает на синхронизирующий вход счетчика 29 адреса, фиксируя в нем код операции. Этот же импульс через о элемент ИЛИ 37 поступает на строби- рующий выход узла 18 формирования адреса, указывая, что на его информационном выходе выдается исполнительный адрес микрокоманды (фиг.8).

Адрес с информационного выхода узла 18 формирования адреса микрокоманды поступает на вход узла памяти, запуская в нем процесс выборки микро- - команды. Одновременно импульс со 40 стробирующего выхода узла 18 формирования адреса поступает на вход элемента 23 задержки и на установочный вход триггера 24. При этом триггер 24 устанавливается в состояние &с 1, указывая на то, что рассматриваемый блок управления выполняет микропрограмму (фиг.8). Нулевое значение с инверсного выхода триггера 24 через выход 12 поступает на соответствующий разряд шины 13. При этом выход элемента И 6 устанавливается в О, указывая на то, что мультимикро- программная система начала выполнение указанной по входу 7 операции (блок 2 алгоритма на фиг. 9) . Информацией- ное поле выбранной микрокоманды поступает по выходу 16, а поле формата - I по выходу 17 узла 15 памяти микро35

50

, 5 о

- 0 с 5

0

программ. Поле формата выбранной микрокоманды поступает на информационный вход дешифратора 20. Одновременно одиночный импульс, задержанный на элементе 23 задержки на время формирования адреса в узле 18 и выборки микрокоманды из узла 15 памяти, поступает на стробирующий вход дешифратора 20 формата микрокоманды (блок 2 алгоритма на фиг.9). При этом в зависимости от формата микрокоманды на одном из выходов дешифратора 20 ,. появляется импульс с его стробирующего входа, Далее работа блока микропрограммного управления полностью определяется форматом выбранной микрокоманды. ,

Возможны следующие случаи:

Поле КОЛУ кода опроса логических условий микрокоманды формата А поступает на первый вход мультиплексора 28, на выходе которого появляется значение 1 если хотя бы одно из анализируемых логических условий, поступающих по входу 9 истинно, и О в противном случае.

Одновременно, импульс с первого выхода дешифратора 22 формата микрокоманд поступает на вход одновибратора 30, который по перепаду 1-0 вырабатывает одиночный импульс.

Если выходное значение мультиплексора 28 равно О (все опрашиваемые

логические условия ложны), одиночный импульс с выхода одновибратора 30, через элемент И 38 и элемент ИЛИ 35 поступает на синхровход счетчика 29 адреса (фиг.8), фиксируют в нем в качестве исполнительного адреса следующей микрокоманды значение Асл .

Если же выходное значение муль - типлексора 28 равно 1 (хотя бы одно опрашиваемое логическое условие истинно) , одиночный импульс с выхода одновибратора 30 через элемент И 39 и через элемент ИЛИ 36 посту- (пает на вход +1 счетчика 29 адреса, увеличивая его содержимое на единицу.

Таким образом, если опрашиваемые логические условия ложны, следующим исполнительным адресом будет адрес Асл; если же хотя бы одно из опрашиваемых условий истинно, в качестве исполнительного адреса используется текущий адрес из счетчика 29, увеличенный на единицу. При необходимости безусловного перехода в поле КОЛУ микрокоманды формата А записываются нули. При этом выход мультиплексора 28 независимо от значений логических условий равен О и в качеств исполнительного адреса в счетчике 29 фиксируется адрес AtA.

Исполнительный адрес с выхода узла 18 вновь поступает на вход узл 15 памяти микрокоманд и запускает процесс выборки очередной микрокоманды. Одновременно импульс с выхода одновибратора 30 через элемент ИЛИ 3 поступает на стробирующий выход узла 18 формирования адреса, указывая, на то, что начался процесс выборки очередной микрокоманды (фиг.8).

На этом процесс выполнения микрокоманды формата А завершен.

10

15

20

25

31542ю

элементов ИЛИ блока 4 передачи адресов запуска поступает на адресные входы идентичных блоков микропрограммного управления.

При этом если в поле А записан ненулевой код, соответствующий блок микропрограммного управления аналогично описанному начинает выполнение микропрограммы, первая команда которой хранится по адресу А.

Если же в поле А записан нулевой код, он, поступая на адресный вход соответствующего блока микропрограммного управления, не оказывает на его состояние никакого влияния, так как при нулевом адресе запуска выход элемента ИЛИ 33 остается равным нулю.

Таким образом, соответствующим заполнением полей Aj,A,..., А ц обеспечивается избирательный запуск параллельных микропрограмм, хранимых в блоках микропрограммного управления.

Одновременно импульс со второго выхода дешифратора 22 поступает на узел 18 формирования адреса, запуская в нем процесс выработки очередного исполнительного адреса. При этом по перепаду 1-0 рассматриваемого импульса одновибратор 31 вырабатывает одиночный импульс, который через элементы И 34 и ИЛИ 36 увеличивает содержимое счетчика 29 адреса. Таким образом, выполняется переход к следующей по порядку микрокоманде .

Одновременно импульс с выхода одновибратора 31 через элемент ИЛИ 37, поступает на выход узла 18 формирования адреса, указывая на то, что начался процесс выборки очередной микрокоманды (фиг.8).

На этом процесс выполнения микрокоманды формата В завершен.

30

35

40

45

50

55

Нулевое (исходное) состояние регистра 19 адреса не создает помех при возможных повторных запусках рассматриваемого блока микропрограммного управления, так как возможный адрес запуска через группу 27 элементов ИЛИ передается на информационный вход счетчика 29 адреса.

Нулевое состояние триггера 24 указывает на то, что рассматриваемый блок микропрограммного управления завершил выполнение соответствую щей микропрограммы. При этом значение 1 с инверсного выхода триггера 24 через выход 12 поступает на соответствующий разряд шины 13 и оттуда на все блоки 1.1-1.N микропрограммного управления и на элемент И 6.

15

20

25

вход узла 18 формирования адреса, пуская в нем процесс выработки оче редного исполнительного адреса. Ра сматриваемый импульс, через элемен ИЛИ 34 и 36 поступает на вход +1 счетчика 29 адреса, увеличивая его содержимое (фиг.8). Таким образом, следующий исполнительный адрес пол чается из текущего путем его увели ния на единицу. Одновременно рассм риваемый импульс через элемент ИЛИ поступает на стробирующий выход уз 18 формирования адреса,-указывая н то, что начался процесс выборки оч редной микрокоманды.

На этом процесс выполнения микр команды формата D завершен.

ментов И поле микроопераций (МО) рас-JQ ливает триггер 46 в состояние 1.

35

40

сматриваемой микрокоманды. Соответствующие микрооперации с выхода 11 поступают на управляемое оборудование. Одновременно рассматриваемый импульс поступает на управляющий вход узла 20 синхронизатора микроопераций и записывает в регистр 40 поле МО микрокоманды формата D. При этом йыход элемента ИЛИ 41 устанавливается в 1. По мере асинхронного выполнения микроопераций, выдаваемых по выходу 11, управляемое оборудование вырабатывает сигналы, подтверждающие их выполнение, которые поступают по входу 10 на входы сброса ответствующих триггеров регистра 40. В момент завершения выполнения всех выданных микроопераций содержимое регистра 40 становится нулевым. При этом выход элемента ИЛИ 41 также устанавливается в .О. По перепаду 1-0 сбрасывает одновибратор 42, одиночный импульс с выхода которого индицирует завершение процесс асинхронного параллельного выполнения микроопераций, указанных в поле МО микрокоманды формата D., Импульс с выхода узла 20 синхронизатора микроопераций поступает на

Одновременно поле КОПМ микрокоманд формата Е поступает с выхода 16 уз памяти на первый вход группы 43 эл ментов ИЛИ. На второй вход группы элементов ИЛИ с шины 13 поступают сигналы о состоянии каждого из блоков 1 микропрограммного управле ния. Если блок 1 выполняет некотор микропрограмму, соответствующий триггер 24 установлен в 1 и сигнал на шине 13 равен нулю, т.е. ес блок 1 завершил выполнение микропрограммы, сигнал на шине 13 равен единице.

50

При необходимости опроса состоя .блока 1.j, ,N, разряд Z; поля КОПМ микрокоманды формата Е устано лен в О. В противном случае соот ствующий разряд установлен в 1.

Если опрашиваемый блок 1 еще не завершил выполнение соответствующе микропрограммы, выход элемента И 4 равен После завершения работы для всех опрашиваемых блоков микро программного управления с шины 13 поступают сигналы, равные единице,

выход элемента И 44 становится рав

и 11I i

5

0

5

вход узла 18 формирования адреса, запуская в нем процесс выработки очередного исполнительного адреса. Рассматриваемый импульс, через элементы ИЛИ 34 и 36 поступает на вход +1 счетчика 29 адреса, увеличивая его содержимое (фиг.8). Таким образом, следующий исполнительный адрес получается из текущего путем его увеличения на единицу. Одновременно рассматриваемый импульс через элемент ИЛИ 37 поступает на стробирующий выход узла 18 формирования адреса,-указывая на то, что начался процесс выборки очередной микрокоманды.

На этом процесс выполнения микрокоманды формата D завершен.

Одновременно поле КОПМ микрокоманды формата Е поступает с выхода 16 узла памяти на первый вход группы 43 элементов ИЛИ. На второй вход группы 43 элементов ИЛИ с шины 13 поступают сигналы о состоянии каждого из блоков 1 микропрограммного управления. Если блок 1 выполняет некоторую микропрограмму, соответствующий триггер 24 установлен в 1 и сигнал на шине 13 равен нулю, т.е. если блок 1 завершил выполнение микропрограммы, сигнал на шине 13 равен о единице.

с

0

При необходимости опроса состояния .блока 1.j, ,N, разряд Z; поля КОПМ микрокоманды формата Е установлен в О. В противном случае соответствующий разряд установлен в 1.

Если опрашиваемый блок 1 еще не завершил выполнение соответствующей микропрограммы, выход элемента И 44 равен После завершения работы, для всех опрашиваемых блоков микропрограммного управления с шины 13 поступают сигналы, равные единице, и

выход элемента И 44 становится равным

и 11I i

По перепаду 0-1 с выхода элемента И 44 срабатывает одновибратор 45, одиночный импульс с выхода которого поступает на выход узла 21 синхронизатора параллельных микропрограмм, индицируя завершение работы всех опрашиваемых блоков микропрограммног управления, Одновременно импульс с выхода одновибратора 45 сбрасывает триггер 46 в нулевое (исходное) состояние .

Импульс с выхода узла 21 синхронизатора параллельных микропрограмм потупает на управляющий вход узла 18 формирования адреса, запуская в нем процесс выработки очередного исполнительного адреса. При этом рассматриваемый импульс через элементы ИЛИ 34 и 36 поступает на вход +1 счетчика 29 адреса, увеличивая его содержимое, а через элемент ИЛИ 37 - на стробирующий выход узла 18 формирвания адреса (фиг.8). Далее начинается процесс выборки очередной мик рокоманды.

На этом процесс выполнения микрокоманды формата Е завершен.

Таким образом, после запуска блок 1.1 микропрограммного управления мо жет выполнять любую из микрокоманд форматов A,B,C,D.E. С помощью микрокоманды формата А реализуются условные и безусловные переходы; формата В - запуск микропрограмм из любых других блоков микропрограммного (би- фуркаторы и сборка) управления; формата С - завершение работы блока микропрограммного управления; формата D - выдача микроопераций и ожида ние и завершение асинхронных процес сов их выполнения (операторы); формата Е - ожидание завершения асинхроного параллельного выполнения микропрограмм (синхронизаторы).

После запуска каждый из блоков 1.2-1.Ы также может выполнять любые микрокоманды рассматриваемых формато т.е. выдавать микрооперации., запус - кать и опрашивать любые блоки микропрограммного управления и т.п. При этом работа каждого из блоков микропрограммного управления аналогична описанному, т.е. через блок 4 передача адресов запуска на адресные входы поступают соответствующие адреса, начинается процесс выборки микрокоманд и т.д., а состояние каждого блока микропрограммного управления

0

5

0

5

30 5

5

40

45

50

передается на шину 13. Каждый из блоков микропрограммного управления работает независимо друг от друга и может запускать и опрашивать состояние других идентичных блоков.

Признаком конца выполнения операции, заданной соответствующим кодом по входу 7 кода операции , является значение 1 , выдаваемое по выходу 14 признака конца работы. Значение 1 вырабатывается элементом И 6 тогда, когда все триггеры 24 блоков 1 завершили выполнение (с помощью микрокоманд формата С) закрепленных за ними участков микропрограммы.

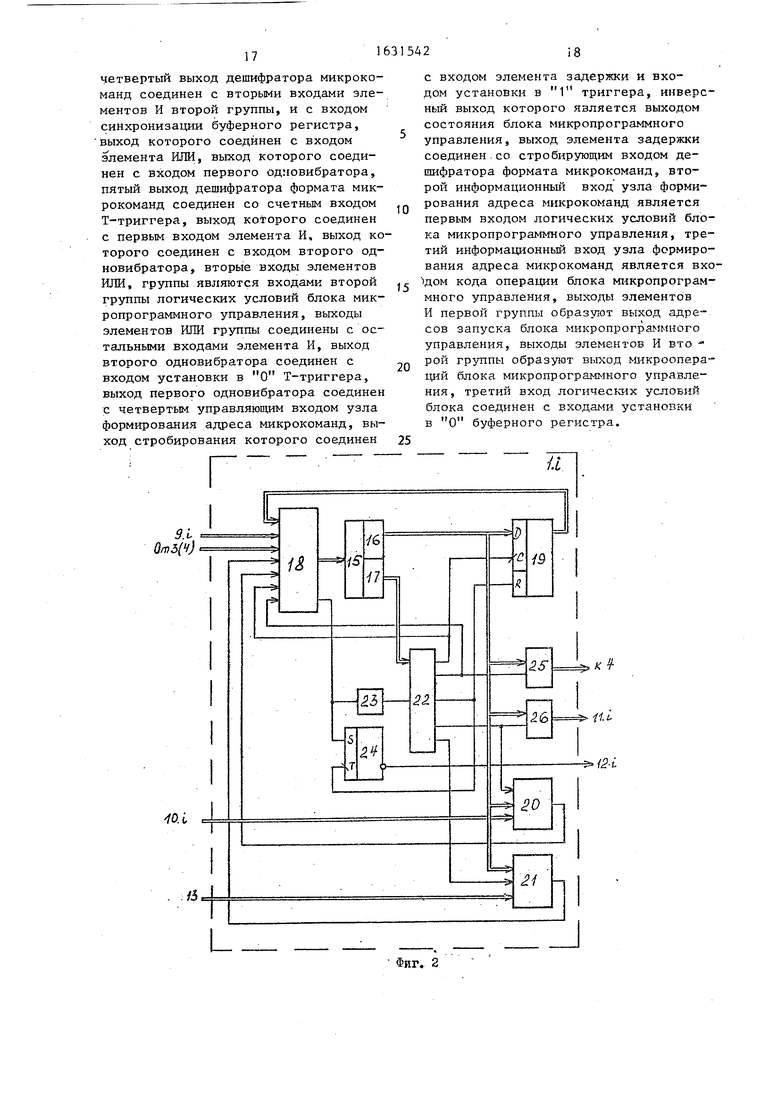

На фиг.10 показан пример функционирования мультипрограммной управляющей системы, содержащей четыре блока микропрограммного управления.

Система позволяет осуществлять асинхронную выдачу микроопераций и ожидать их завершения; запускать на выполнение параллельные участки микропрограмм, каждый из которых может запускать другие параллельные участки; синхронизировать работу любого подмножества параллельных участков микропрограмм; иметь в множестве параллельно работаюдщх блоков микропрограммного управления требуемое число микропрограмм верхнего и нижнего уровней о

Перечисленные дополнительные возможности системы обеспечивают микропрограммирование любых конкретных параллельных асинхронных алгоритмов управления (4,5)„ Микропрограммирование такого типа алгоритмов в прототипе невозможно.

В частности, при разработке микропрограммных устройств управления многопроцессорными системами моделирования возникает задача управления множеством однотипных вычислителей. При этом каждый из специализированных вычислителей реализует закрепленную за ним подмодель и после ее вычисления он становится свободным для реализации других подмоделей. Окончание работы каждого вычислителя заранее непредсказуемо (асинхронно) и зависит от сложности соответствующей под- %модели.

Предлагаемая система позволяет запускать каждый вычислитель асинхронно по мере его освобождения. При этом быстродействие системы моделирования повышается в 5-6 раз из-за более

эффективного управления параллельными процессами.

Аналогичная задача управления параллельными процессами возникает в многоканальных системах связи, использующие решающие или информационные сообщения подтверждения. В частности, алгоритмы процесса передачи дискретной информации и другие яв- , ляются асинхронными и параллельными из-за одновременной работы как прямых, так и обратных каналов. При этом необходимость синхронизации и фазирования по прямым и обратным кана-j лам, реализация принципа резервирования и подтверждения требует асинхронной дисциплины выдачи микроопераций, запуска и синхронизации параллельных процессов (кодирование, деко- - дирование, передача блокаs прием блока, почек ошибок, исправление ошибок, передача запроса, передача подтверждения и т.п.)о

2

Формула изобретения

4

,, ,-

5

Q 0

0

5

тов ИЛИ группы, выход адресов запуска j-ro блока микропрограммного управления (,N) соединен с j-м входом I блока элементов ИЛИ, выход состояния j-ro блока микропрограммного управления соединен с j-ми входами второй группы логических условий с первого по (}-1)-ый и с (j-H)-ro no N блоков микропрограммного управления и с j-м входом элемента И, выход которого является выходом признака конца работы системы, входы третьей группы логических условий блоков микропрограммного управления являются входами завершения микроопераций системы.

четвертый выход дешифратора микрокоманд соединен с вторыми входами элементов И второй группы, и с входом синхронизации буферного регистра, выход которого соединен с входом элемента ИЛИ, выход которого соединен с входом первого одмовибратора, пятый выход дешифратора формата микрокоманд соединен со счетным входом Т-триггера, выход которого соединен с первым входом элемента И, выход которого соединен с входом второго од- новибратора, вторые входы элементов ИЛИ, группы являются входами второй группы логических условий блока микропрограммного управления, выходы элементов ИЛИ группы соединены с остальными входами элемента И, выхоц второго одновибратора соединен с входом установки в О Т-триггера, выход первого одновибратора соединен с четвертым управляющим входом узла формирования адреса микрокоманд, выход стробирования которого соединен

Qmb(4)

0

с входом элемента задержки и входом установки в 1 триггера, инверсный выход которого является выходом состояния блока микропрограммного управления, выход элемента задержки соединен со стробирующим входом дешифратора формата микрокоманд, второй информационный вход узла формирования адреса микрокоманд является первым входом логических условий блока микропрограммного управления, третий информационный вход узла формирования адреса микрокоманд является вхо- r дом кода операции блока микропрограммного управления, выходы элементов И первой группы образуют выход адресов запуска блока микропрограммного управления, выходы элементов И вто - рой группы образуют выход микроопераций блока микропрограммного управления , третий вход логических условий блока соединен с входами установки

0

в 0 буферного регистра.

25

к ЧФиг. 2

Фиг.З

от 22.

От 46

&г

Г

L

Лг.5

ькгъ.м

20

м

-а/6

J

Щ

Р

АСА КОЛУ 001fn а у ,

|1-1-I 9ормот /(Вт 1.1

(fall , А, , Лг t ... |0, g|

От 1 N

°11 I Формат С

МО

° ° Формат D

КОПМ

.10-1

«Ро/з/уа/т Ј

Фиг. 7

s

33

П

Ш

Г

ВДг

je/

«У

&. kiv

Фиг. 8

9/ &fetff 7 J3ff 00#04 /ffjaff/ aa 33 гдуяла

( fff

gy

регистр & ffy/ t mwMe#f0f 39 QdffoЈv5f amoЈ 3O fvemwf( 39

одяо&/5/эа/п0р з/ 34,$S /Miff cvfmvv 89

Фиг. 9

/ ett/em/ /9 тр&ггее fv

yj&fff-f

Фиг. 10

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Станок для обматывания электрических проводников изолирующей пряжей | 1931 |

|

SU33594A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1991-02-28—Публикация

1989-02-28—Подача