(54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| Динамическое запоминающее устройство | 1982 |

|

SU1065886A1 |

| Устройство управления | 1984 |

|

SU1171790A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА АКТИВНОГО ВИДЕО | 1999 |

|

RU2173883C2 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Динамическое оперативное запоминающее устройство | 1987 |

|

SU1499401A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1983 |

|

SU1119065A1 |

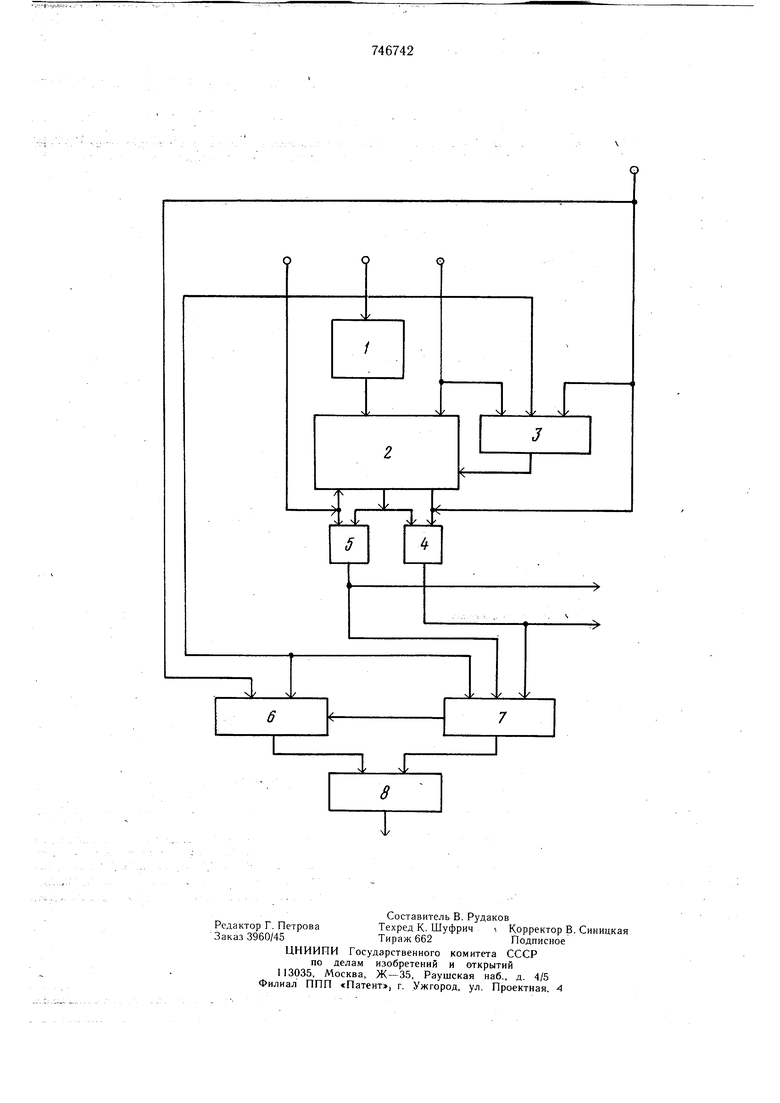

Изобретение относится к области запоминающих устройств. Известны устройства для защиты памяти 1. Одно из известных устройств содержит блок считывания, регистры, логические элементы, в соответствии с которыми данные, подлежаи ие защите, снабжаются специальными метками, которые определяют возможность доступа пользователя к хранимым данным. Недостатком известного устройства является то, ЧТО в случае подмены либо исклю чения метки, вся информация, хранимая в па мяти, оказывается незащищенной. Известно также устройство для защиты памяти, содержащее регистры, накопитель -информации, дещифраторы, элементы ИЛИ и И 2. Недостатком известного устройства является его низкая функциональная надеж-ность, выражающаяся в том, что не исключается возможность считывания данных путем несанкционированного доступа пользователей к носителям информации, либо визуального считывания данных, хранимых на перфоносителях (перфолентах, перфокартах). Целью изобретения является повыщение надежности устройства. Поставленная цель достигается тем, что устройство содержит генератор Кодов адреса, счетчик и схему сравнения, прМчём входы генератора кодов адреса подключены соответственно к выходу накопителя информации, к первому, второму и третьему входам устройства и выходам одних из регистров, а выход соединен с первыми входами элементов И, вторые входы которых подключены ко второму и третьему входам устройства, выходы элементов И соединены с первым и вторым выходами устройства и одними из входов счетчика, другой вход которого подключен к четвертому входу устройства, выходы счетчика соединены с первым входом схемы сравнения и входами других регистров, выходы которых подключены ко второму входу схемы сравнения, выход которой соединен с третьим выходом устройства. На чертеже изображена схема предложенного устройства.

Устройство содержит накопитель 1 информации, генератор 2 кодов адреса, регистры 3, первый 4 и второй 5 элементы И, регистры 6, счетчик 7 и схему 8 сравнения.

Входы генератора 2 подключены соответственно к выходу накопителя 1, к первому, второму и третьему входам устройства и выходам регистров 3, а выход соединен с первыми входами элементов И 4 и 5, вторые входы которых подключены ко второму и третьему входам устройства. Выходы элементов И 4 и 5 соединены с первым и вторым выходами устройства и одними из входов счетчика 7, другой вход которого подключен к четвертому входу устройства. Выходы счетчика 7 соединены с первым входом схемы 8 сравнения и входами регистров 6, выходы которых пoJiключeны ко второму входу схемы 8 сравнения, выход которой соединен с третьим выходом устройства.

Устройство работает следующим образом. Режим записи в память.

Идентификатор программы, поступающий на четвертый вход устройства, выбирает из накопителя 1 ключ закона перемещивания адресов, который подается на генератор 2. Генератор в соответствии с ключом закона перемешивания адресов осуществляет выбор закона перемешивания адресов, по которому и происходит перемешивание адресов. МлаДшие разряды кода адреса подаются на генератор 2 и на регистры 3, в которых записывается только первый код адреса (этот первый код адреса будет необходим для режима считывания из памяти). На генератор также поступает сигнал-запрос на запись. По этому сигналу генератор начинает перемешивание адресов, поступающих по первому входу устройства в.соответствии с законом, выбранным по ключу закона перемешивания адресов. На выходе генератора образуется перемешанная последовательность адресов, которая через элемент И 5, на один из входов которого поступает сигнал-запрос записи, подается на первый выход устройства, связанный с оперативным запоминающим устройством (ОЗУ) (на чертеже не показано). Эта последовательность подается и на счетчик 7, который производит счет сформированным адресам и записывает его в регистры 6. Если записываемая информация будет записана на внешний накопитель, то она будет переписываться из ОЗУ последовательно, т. е. в перемешанном виде. Даже если какой-либо неправомочный пользователь получит возможность считывания информацйй с внёшнего накопителя, то он получит перемешанную последовательность информации.

Режим считывания из памяти. Так же как и пргг записи, идентификатор программы выбирает из накопителя 1

ключ закона перемешивания адресов, который поступает на генератор 2. Генератор по ключу закона перемешивания адресов производит выборку закона перемещивания адресов, по которому осуществляется перемешивание адресов. По идентификатору с приходом сигнала-запроса на считывание из регистров 3 производится считывание первого кода адреса, по которому эта программа была ранее записана. Этот код подается на генератор. С первого входа устройства в генератор подаются младшие разряды кода адреса. Старшие разряды кода адреса (на чертеже не показаны) определяют объем памяти (страница памяти, блок памяти и др.), в пределах которого необходимо производить перемешивание адресов. Имея объем памяти и начальный адрес, генератор по сигналу-запросу на считывание начинает перемешивание адресов. Перемешанная последовательность адресов считывания через элемент И 4, на один из входов которого подается сигнал-запрос на считывание, передается в ОЗУ. Эта последовательность адресов также подается на счетчик 7, который, будучи обнуленный идентификатором, начинает считать количество

сформированных адресов считывания и передает это количество адресов на схему 8 сравнения. Из регистров 6 по сигналу-запросу на считывание и по идентификатору программы выбирается количество сформированных в режиме записи адресов данной программы и подается на схему сравнения.

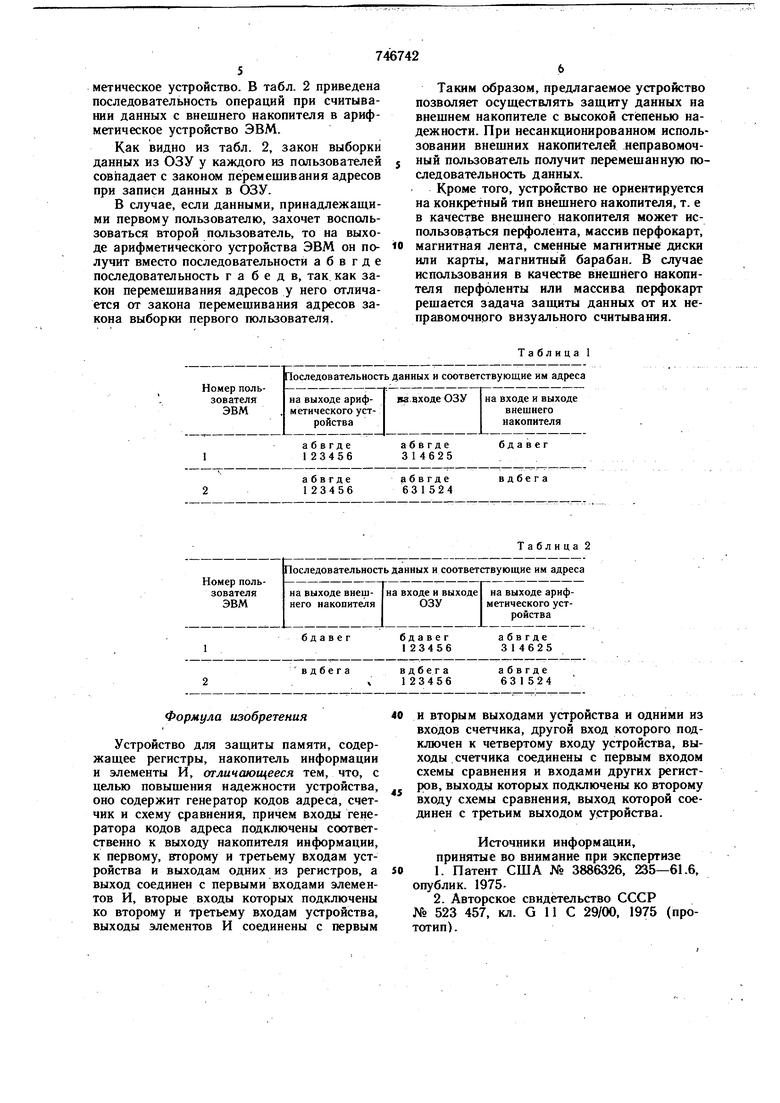

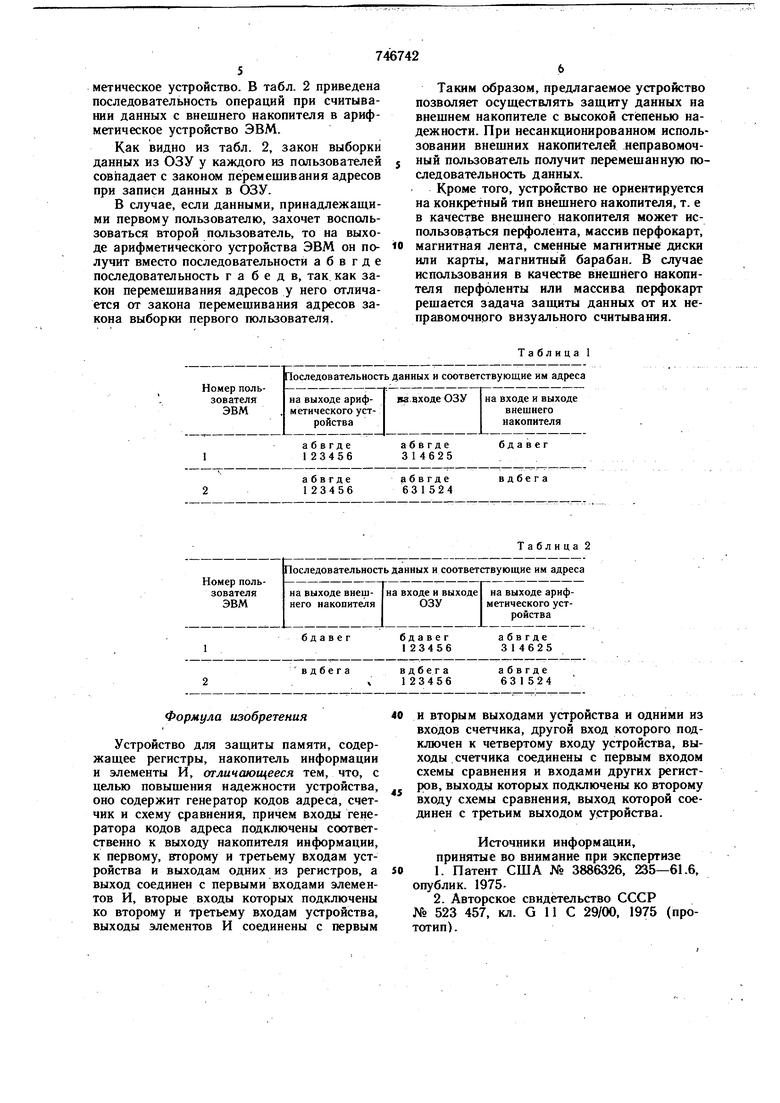

Процесс защиты при записи данных на внешний накопитель пояснен в табл. 1. Адреса данных, подлежащих защите, поступают из арифметического устройства (на чертеже не показано) на вход устройства, которое модифицирует их по определенному , закону. Таким образом, данные в ОЗУ записываются по определенному закону и в дальнейшем переписываются оттуда на внещНИИ накопитель последовательно.

Как видно из табл. 1, устройство модифицирует адреса данных при их записи в ОЗУ. Причем адреса модифицируются в пределах объема памяти, необходимого для записи блока данных. Таким образом, в оперативной памяти данные будут записаны не по порядку, а по определенному для каждого пользователя закону. При записи данных на внёщний накопитель данные из

ОЗУ выбираются последовательно, начиная с первой ячейки. И в результате данные на внешнем накопителе оказываются перемешанными по определенному закону.

При считывании информации переписывается с внешнего накопителя в ОЗУ последовательно. С помощью устройства преобразования адресов формируется последовательность адресов, в которой будет считываться информация из ОЗУ и передаваться в арифметическое устройство. В табл. 2 приведена последовательность операций при считывании данных с внешнего накопителя в арифметическое устройство ЭВМ.

Как видно из табл. 2, закон выборки данных из ОЗУ у каждого из пользователей совпадает с законом перемешивания адресов при записи данных в ОЗУ.

В случае, если данными, принадлежащими первому пользователю, захочет воспользоваться второй пользователь, то на выходе арифметического устройства ЭВМ он получит вместо последовательности а б в г д е последовательность г а б е д в, так как закон перемешивания адресов у него отличается от закона перемешивания адресов закона выборки первого пользователе.

Последовательность данных и соответствующие им адреса

:р-1

на выходе ариф- на.входе ОЗУ на входе и выходе

, метического уст-внешнего

ройстванакопителя

абвгде абвгде бдавег

123456 314625

абвгде абвгде вдбега

123456631524

Последовательность данных н соответствующие им адреса

11-

на выходе виеш- I на входе н выходе на выходе арнфнего накопителяОЗУметнческого устбдавег бдавег абвгде

123456 314625

вдбега вдбега абвгде

,123456631524

Формула изобретения

Устройство для защнты памяти, содержащее регистры, накопитель информации и элементы И, отличающееся тем, что, с целью повышения надежности устройства, оно содержит генератор кодов адреса, счетчик и схему сравнения, причем входы генератора кодов адреса подключены соответственно к выходу накопителя информации, к первому, еторому и третьему входам устройства и выходам одних из регистров, а выход соединен с первыми входами элементов И, вторые входы которых подключены ко второму и третьему входам устройства, выходы элементов И соединены с первым

Таким образом, предлагаемое устройство позволяет осушествлять зашигу данных на внешнем накопителе с высокой степенью надежности. При несанкционированном использовании внешних накопителей неправомочный пользователь получит перемешанную последовательность данных.

Кроме того, устройство не ориентируется на конкретный тип внешнего накопителя, т. е в качестве внешнего накопителя может использоваться перфолента, массив перфокарт, магннтная лента, сменные магнитные диски или карты, магнитный барабан. В случае использования в качестве внешнего накопителя перфоленты или массива перфокарт решается задача защиты данных от их неправомочного внзуального считывания.

Таблица 1

Таблнца 2

ройства

И вторым выходами устройства и одними из входов счетчика, другой вход которого подключен к четвертому входу устройства, выходы счетчика соединены с первым входом схемы сравнения и входами других регистров, выходы которых подключены ко второму входу схемы сравнения, выход которой соединен с третьим выходом устройства.

Источники информации, принятые во внимание при экспертизе 1. Патент США № 3886326, 235-61.6, опублик. 19752. Авторское свидетельство СССР № 523 457, кл. G 11 С 29/00, 1975 (прототип).

Авторы

Даты

1980-07-05—Публикация

1978-02-03—Подача