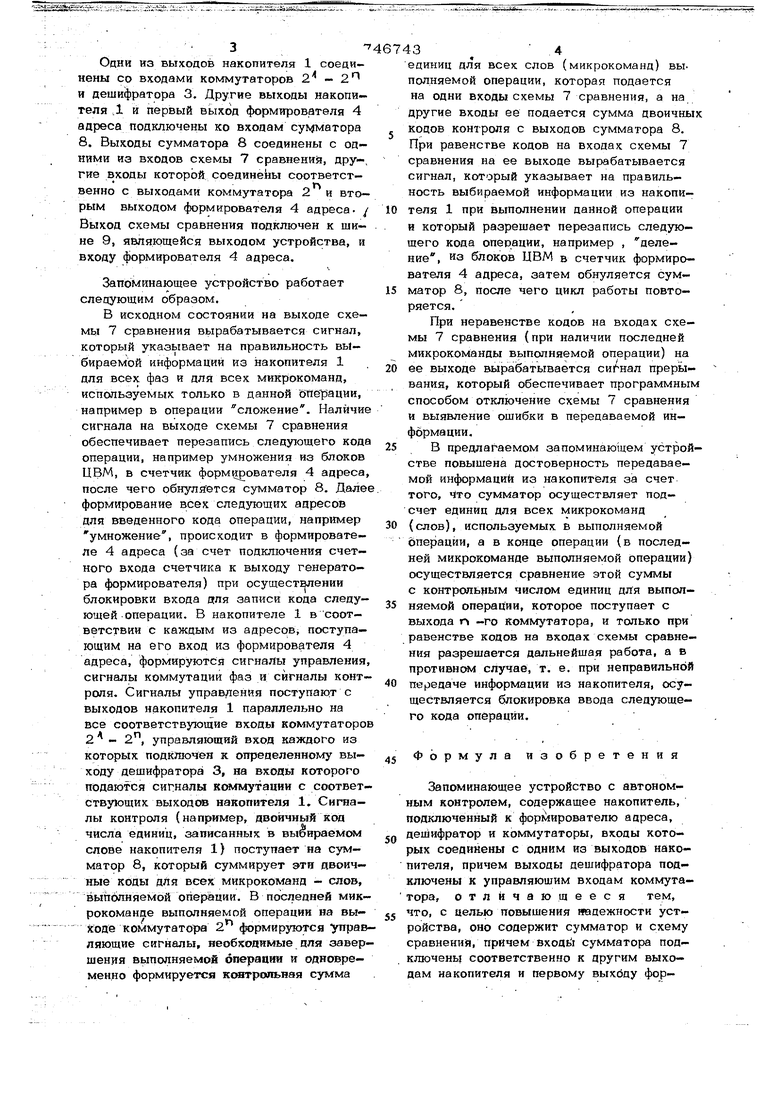

, Изобретение относится к запоминающим устройствам и предназначено для использования в микропрограммных устройствах управления. Известно запоминающее устройство, которое служит для хранения микрокоманд и содержит накопитель с зонами задержки, функции, адреса и управляющих сигналов . Недостатком этого устройства являет ся невысокое быстродействие. Наиболее близким техническим решением к данному изобретению является запоминающее устройство, содержащее накопитель, подключенный к формирователю адреса, дешифратор и коммутаторы входы которых соединены с одними из выходов накопителя, причем выходы деш фратора подключены к управляющим входам коммутаторов 2}. В этом запоминающем устройстве не проверяется правильность передаваемой информации, что снижает надежность .устройства. Целью изобретения является повышение надежности устройства. Поставленная цель достигается тем, что устройство содержит сумматор и схему сравнения, причем входы сумматора подключены соответственно к другим выходам накопителя и первому выходу формирователя адресов, а выходы - к одной из входов схемы сравнения, другие входы которой соединены соответственно с выходами одного из коммутаторов и вторым выходом формирователя адреса, выход схемы сравнения подключен к выходу устройства и входу формирователя адреса. На чертеже представлена структурная схема запоминающего устройства с автономным контролем, служащего для хранения микрокоманд. Устройство содержит накопитель 1, коммутаторы 2 -2 , дешифратор 3, формирователь 4 .адреса со входом 5, выходные шины 6, схему 7 сравнения, сумматор 8, шину 9 прерывания. Одни из выходов накопителя 1 соединены со входами коммутаторов 2 - 2 и дешифратора 3. Другие выходы накопителя Д и первый выход формирователя 4 адреса подключены ко входам сумматора 8. Выходы сумматора 8 соединены с одними иа входов схемы 7 сравнения, другие входы которой соединены соответственно с выходами коммутатора 2 и вторым выходом формирователя 4 адреса. / Выход схемы сравнения подключен к шине 9, являющейся выходом устройства, и входу формирователя 4 адреса. Запоминающее устройство работает следующим образом. В исходном состоянии на выходе схемы 7 сравнения вырабатывается сигнал, который указывает на правильность выбираемой информации из накопителя 1 для всех фаз и для всех микрокоманд, используемых только в данной Шерации, например в операции сложение. Наличие сигнала на выходе схемы 7 сравнения обеспечивает перезапись следующего код операции, например умножения из блоков ЦВМ, в счетчик формирователя 4 адреса после чего обнуляется сумматор В. Дале формирование всех следующих адресов для введенного кода операции, например умножение, происходит в формирователе 4 адреса (за счет подключения счетного входа счетчика к выходу генератора формирователя) при осуществлении блокировки входа для записи кода следующей -операции. В накопителе 1 всоответствии с каждым из адресов, поступающим на его вход из формирователя 4 адреса, формируются сигналы управления сигналы коммутации фаз и сигналы контроля. Сигналы управ/1ения поступают с выходов накопителя 1 параллельно на все соответствующие входы коммутаторо 2 - 2, управляющий вход каждого из которых подключен к определенному выходу дешифратора 3, на входы которого подаются сигналы коммутации с соответству1ощих выходов накопителя 1. Сигналы контроля (например, двоичный ксад числа единиц, записанных в выбираемом слове накопителя 1) поступает на сумматор 8, который суммирует эти двоичные коды для всех микрокоманд - слов, выполняемой операции. В последней микрокоманде выполняемой операции на выходе коммутатора 2 формируются управ ляющие сигналы, необходимые для завер шения выполняемой операции и одновременно формируется ксятрольная сумма 3 единиц для всех слов (микрокоманд) вы. полняемой операции, которая подается на одни входы схемы 7 сравнения, а на другие входы ее подается сумма двоичных кодов контроля с выходов сумматора 8. При равенстве кодов на входах схемы 7 сравнения на ее выходе вырабатывается сигнал, который указывает на правильность выбираемой информации из накопи- теля 1 при выполнении данной операции и который разрешает перезапись следующего кода операции, например , деление, из блоков ЦВМ в счетчик формирователя 4 адреса, затем обнуляется сумматор 8, после чего цикл работы повторяется. При неравенстве кодов на входах схемы 7 сравнения (при наличии последней микрокоманды вьтолняемой операции) на ее выходе вырабатывается прерывания, который обеспечивает программным способом отключение схемы 7 сравнения и выявление ошибки в передаваемой информации. В предлагаемом запоминающем устройстве повышена достоверность передаваемой информации из накопителя за счет того, iTo сумматор осуществляет подсчет единиц для всех микрокоманд (слов), используемых в выполняемой операции, а в конце операции (в последней микрокоманде выполняемой операции) осуществляется сравнение этой суммы с контрольным числом единиц для выполняемой операции, которое поступает с выхода п -го коммутатора, и только при равенстве кодов на входах схемы сравнения разрешается дальнейшая работа, а в противндал случае, т. е. при неправильной передаче информации из накопителя, осуществляется блокировка ввода следующего кода операции. Формула изобретения Запоминающее устройство с автономным контролем, содержащее накопитель, подключенный к формирователю адреса, дешифратор и коммутаторы, входы которых соединены с одним из выходов накопителя, причем выходы дешифратора подключены к управляющим входам коммутатора, отличающееся тем, что, с целью повышения надежности устройства, оно содержит сумматор и схему сравнений, причем входи сумматора подключены соответственно к другим выходам накопителя и первому выходу формирователя адресов, a выходы - к одним из входов схемы сравнения, другие вко- ды которой соединены соответственно с выходами одного из коммутаторов , и вторым выходом формирователя адреса, выход схемы сравнения подключен к выходу устройства и входу формирователя адреса.

746743

Источники информации, принятые во внимание при экспертизе

1.Булей Г. Микропрограммирование, М.Мир. 1973, с. 17.

2.Авторское свидетельство СССР

N9 49О179, кл. Q 11 С 11/00, 1973 г (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1980 |

|

SU898511A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство управления | 1981 |

|

SU995091A1 |

| Запоминающее устройство | 1976 |

|

SU661607A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU957277A1 |

| Микропрограммное устройство управления | 1981 |

|

SU987623A1 |

| УСТРОЙСТВО ПРОГРАММНОГО КОНТРОЛЯ | 1967 |

|

SU224909A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

Авторы

Даты

1980-07-05—Публикация

1978-04-17—Подача