1

Изобретение относится к запоминающим устройствам и предназначено для использования в микропрограммных устройствах управления.

Известно запоминающее устройство, содержащее накопитель, формирователь адреса, дешифратор, связанный с цепями управления коммутаторов, информационные входы которых подключены параллельно к выходам накопителя 11 .

Недостаток этого устройства - малая надежность.

Наиболее близким техническим рещением к изобретению является запоминающее устройство микрокоманд, содержащее накопитель, формирователь адреса, депшфратор, связанный с цепями управления коммутаторов, информационные входы которых подключены параллельно к выходам накопителя, сумматор и блок сравнения 2.

В зтом устройстве осуществляется пооперационный контроль (т.е. только после выборки всех слов из накопителя, используемых в данной операции) по четности без учета

изменения внешних условий, которые оказы- вают влияние на количество микрокоманд, используемых в выполняемой операции, и на последовательность их выполнения, что снижает надежность и ограничивает область применения известного запоминающего устройства микрокоманд.

Цель изобретения - повышение надежности и расширение области применения устройства.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопитель, формирователь адресных сигналов, дешифратор, коммутаторы, сумматор и схему сравнения, причем вход накопителя подключен к первому выходу формирователя адресных сигналов, а выходы соединены соответственно с одними из входов сумматора, входами дешифратора, одними из входов коммутаторов и первым входом формирователя адресных сигналов, второй и третий входы которого являются соответственно первым и вторым входами устройства, выходы дешифратора соединены с другими входами

3

коммутаторов, одни из выходов дешифратора и выходы сумматора подключены соответственно к одним из входов схемы сравнения, выход которой соединен с четвертым входом формирователя адреошх сигналов и является одним из выходов устройства, другими выходами которого являются одни из выходов коммутаторов, второй выход формирователя адресных сигналов подключен к другому входу сумматора, введены дополнительнь1е сумматор и коммутатор, входы которого подключены соответственно к одним из входов сумматора и второму входу устройства, входы дополнителыюго сумматора соединены соответственно с выходами дополнительного коммутатора, одними из выходов одного из коммутаторов и вторым выходом формирователя адресных сигналов, а выходы подключены к другим входам схемы сравнения.

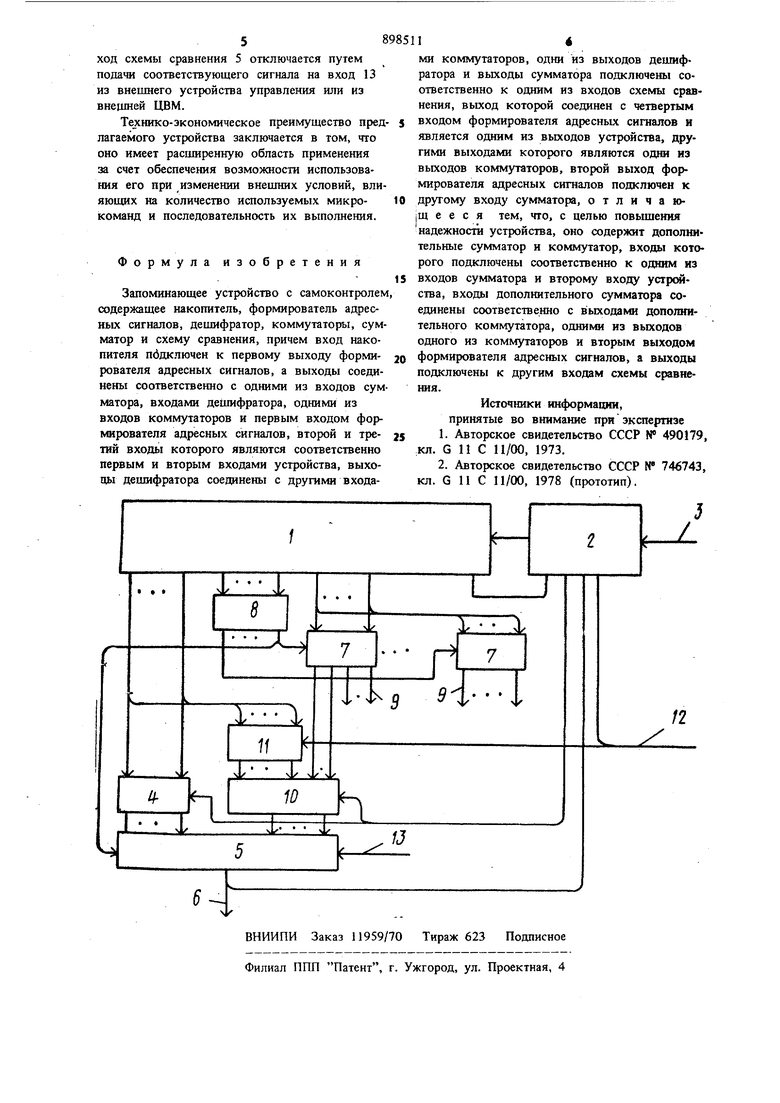

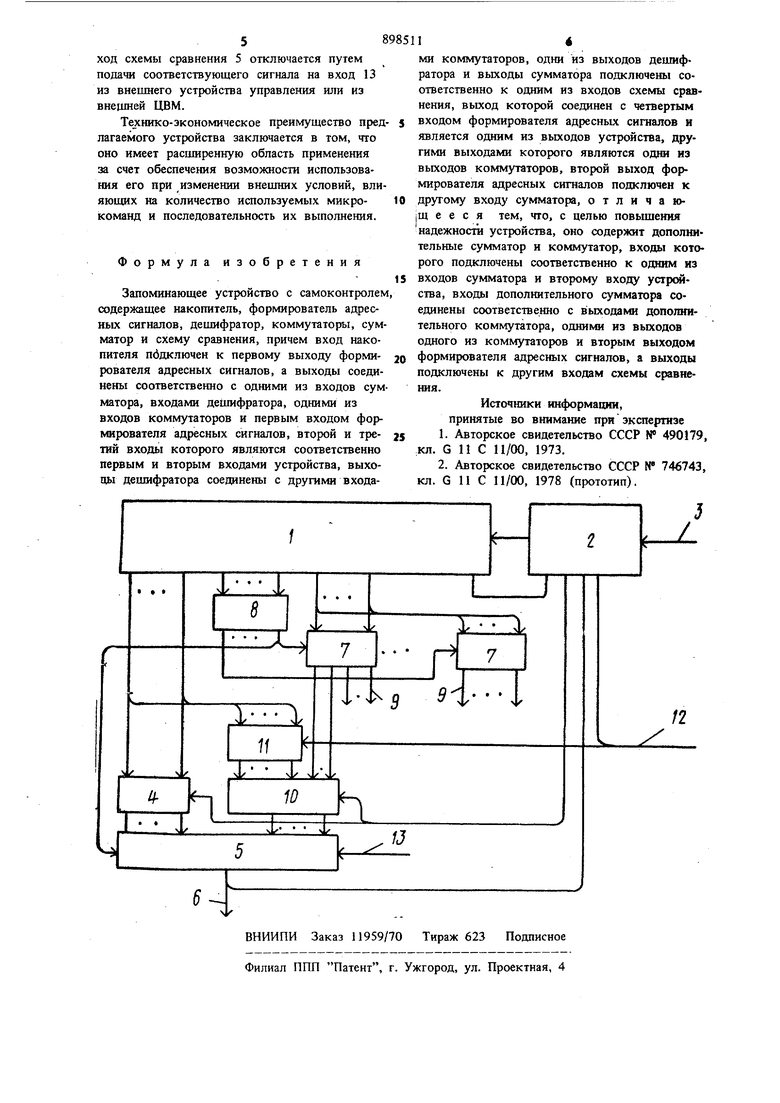

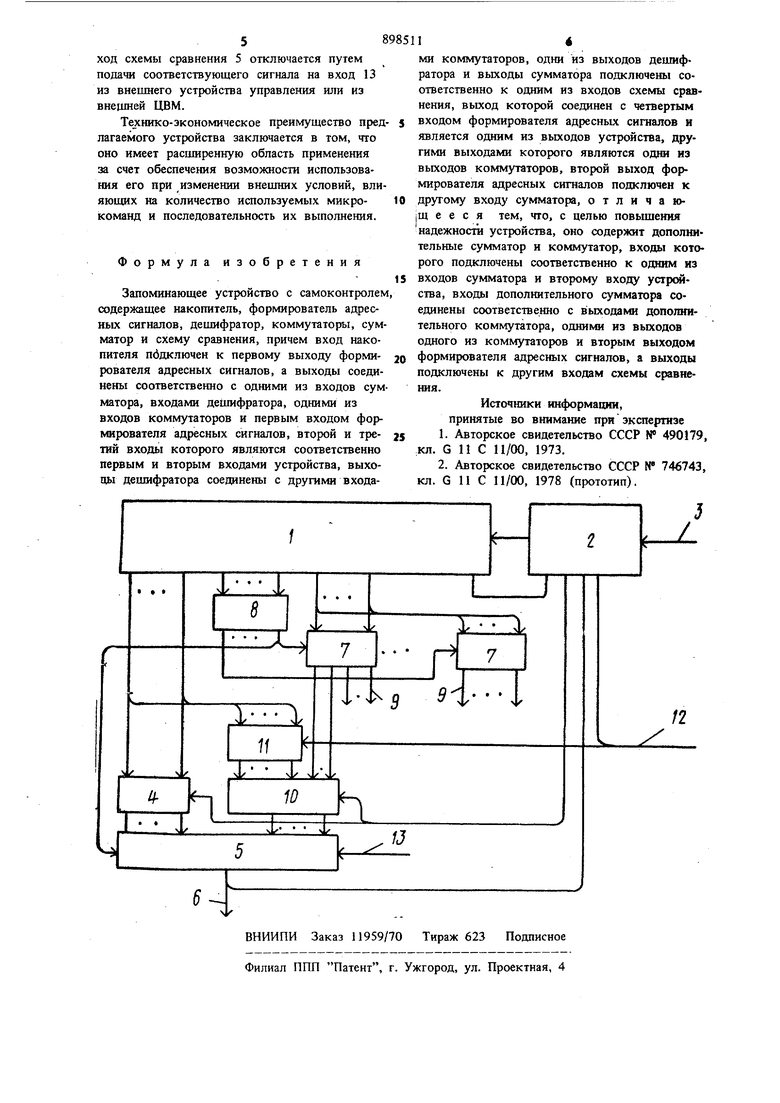

На чертеже изображена структурная схема запоминающего устройства с самоконтролем. Устройство содержит накопитель 1, вход которого подключен к первому вькоду формирователя адресных сигналов 2, один из входов которого является первым входом 3 устройства, сумматор 4, схему сравнения 5, имеющую выход, являющийся одним из выходов 6 устройства, коммутаторы 7 по числу микрокоманд, максимально используемых в одной операции, дешифратор 8. Коммутаторы 7 имеют выходы 9. Кроме того, устройство содержит дополнительные сумматор 10 и коммутатор П. Устройство имеет второй 12 и третий 13 входы.

Входы коммутатора 11 подключены соотретственно к одним из входов сумматора 4 и входу 12 устройства. Входы сумматора 10 роединены соответственно с выходами коммутатора 11 и одними из выходов одного из коммутаторов 7 и вторым выходом формирователя 2. Одни из входов схемы сравнения 5 подключены к выходам сумматора 4, дешифратора 8 и входу 13 устройства, другие к выходам сумматора 10.

Запоминающее устройство работает следующим образом.

В исходном состоянии на выходе схемы сравнения 5 вырабатьгаается сигнал, указьшакнций на правильность выбираемой информации из накопителя 1 для всех фаз и для всех микрокоманд, используемых только в данной операции, например в операции сложение. Наличие сигнала на выходе схемы сравнения 5 обеспечивает перезапись следующего кода операции, например умножение, из блоков ЦВМ в счетчик формирователя 2, после чего обнуляются сумматоры 4 и 10. Далее, формирование всех следующих адресов для введенного кода операции (например ум14

ножение) осуществляется в формирователе 2. Из накопителя 1, в соответствии с каждым из адресов, поступающим на его вход из формирователя 2, выбирается слово с сигналами управления, коммутации фаз и контроля. Сигналы управления поступают с одних их выходов накопителя 1 параллельно на все соответствующие входы коммутаторов 7. На входы дешифратора 8 подаются сигналы коммутации с других выходов накопителя 1. Сигналы контроля (например, двоичный .код числа единиц записанных в выбранном слове из накопителя 1) поступают на входы сумматора 4 (накапливающего типа) и суммируются в нем во всех микрокомандах вьшолняемой операции как при наличии, так и при отсутствии сигнала на входе 12 запоминающего устройства. Кроме того, сигналы контроля поступают на входы сумматора 10 (накапливающего типа) и суммируются в нем при каждом возникновении сигнала на входе 12, указьюающего на отклонение программы вьшолнения да1шой операции, т.е. образуется код смещения контрольной суммы. В последней микрокоманде выполняемой операции подключается схема сравнения 5, на выходе одного из коммутаторов 7 формируются управляющие сигналы необходимые для завершения вьшолняемой операции и, одновременно, формируется контрольная сумма единиц для всех микрокоманд вьшолняемой операции без учета возможнь:х отклонений программы выполнения данной операции. Эта контрольная подается иа входы сумматора 10, в котором суммируется с кодом смещения контрольной суммы и результат подается на одни из входов схемы сравнения 5, на другие входы которой с выходов сумматора 4 подается резултат сложения контрольных кодов для всех микрокоманд данной операции, который смещен на такую же величину, как и контрольная сумма. При равенстве кодов на обеих группах входов схемы сравнения 5 на выходе ее вырабатывается сигнал, указьшающий на правильность выбираемой информации из накопителя 1 при вьшолнении данной операции, и разрешающий перезапись следующего кода операции, например деление из блоков ЦВМ в счетчик формирователя 2, после чего обнуляются сумматоры 4 и 10, и далее цикл работы повторяется. При неравенстве кодов на обеих группах входов схемы сравнения 5 (при наличии последней микрокоманды, выполняемой операции) на выходе ее вырабатывается сигнал ошибки (прерывания программы подаваемой во внешнюю ЦВМ, который обеспечивает также блокировку цепи ввода следующего кода операции из ЦВМ. После выявления ошибки в передаваемой информации выход схемы сравнения 5 отключается путем подачи соответствующего сигнала на вход 13 из внешнего устройства управления или из внешней ЦВМ. Технико-экономическое преимущество пред лагаемого устройства заключается в том, что оно имеет расширенную область применения за счет обеспечения возможности использования его при изменении внешних условий, вли яющих на количество используемых микрокоманд и последовательность их выполнения. Формула изобретения Запоминающее устройство с самоконтролем содержащее накопитель, формирователь адресных сигналов, дешифратор, коммутаторы, сум матор и схему сравнения, причем вход накопителя пбдключен к первому выходу форми- 20

рователя адресных сигналов, а выходы соединены соответственно с одними из входов сумматора, входами дешифратора, одними из входов коммутаторов и первым входом формирователя адресных сигналов, второй и третий входы которого являются соответственно первым и вторым входами устройства, выходы дешифратора соединены с другими входаподключены к другим входам схемы сравнения.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 490179, кл. G 11 С 11/00, 1973.

2.Авторское свидетельство СССР N 746743, кл. G 11 С 11/00, 1978 (прототип). 14 ми коммутаторов, одни из выходов дешифратора и выходы сумматора подключены соответственно к одним из входов схемы сравнения, выход которой соединен с четвертым входом формирователя адресных сигналов и является одним из выходов устройства, другими выходами которого являются одни из выходов коммутаторов, второй выход формирователя адресных сигналов подключен к другому входу сумматора, отличаю|Щ е е с я тем, что, с цепью повьш1ения надежности устройства, оно содержит дополнительные сумматор и коммутатор, входы которого подключены соответственно к одним из входов сумматора и второму входу устройства, входы дополнительного сумматора соединены соответственно с выходами дополнительного коммутатора, одними из выходов одного из коммутаторов и вторым выходом формирователя адресных сигналов, а выходы

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1978 |

|

SU746743A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU957277A1 |

| ВСЕСОЮЗНАЯ IГ}ШНТНО»Т?ХШ1':?'-КД5^ ВИЕЛИО^г^'Д f | 1972 |

|

SU332463A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1156146A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1264243A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU898510A1 |

Авторы

Даты

1982-01-15—Публикация

1980-05-27—Подача