(54) ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазовый дискриминатор | 1983 |

|

SU1167523A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Частотно-фазовый детектор | 1980 |

|

SU921043A1 |

| Цифровой частотный демодулятор | 1984 |

|

SU1298845A1 |

| Частотно-фазовый дискриминатор | 1977 |

|

SU699666A1 |

| Импульсно-фазовый дискриминатор | 1973 |

|

SU450309A1 |

| Фазовый дискриминатор | 1977 |

|

SU632073A1 |

| Цифровой демодулятор сигналов с относительной фазовой модуляцией | 1981 |

|

SU985970A1 |

| Фазовый дискриминатор | 1986 |

|

SU1334355A1 |

| Калибратор фазового сдвига | 1985 |

|

SU1352400A1 |

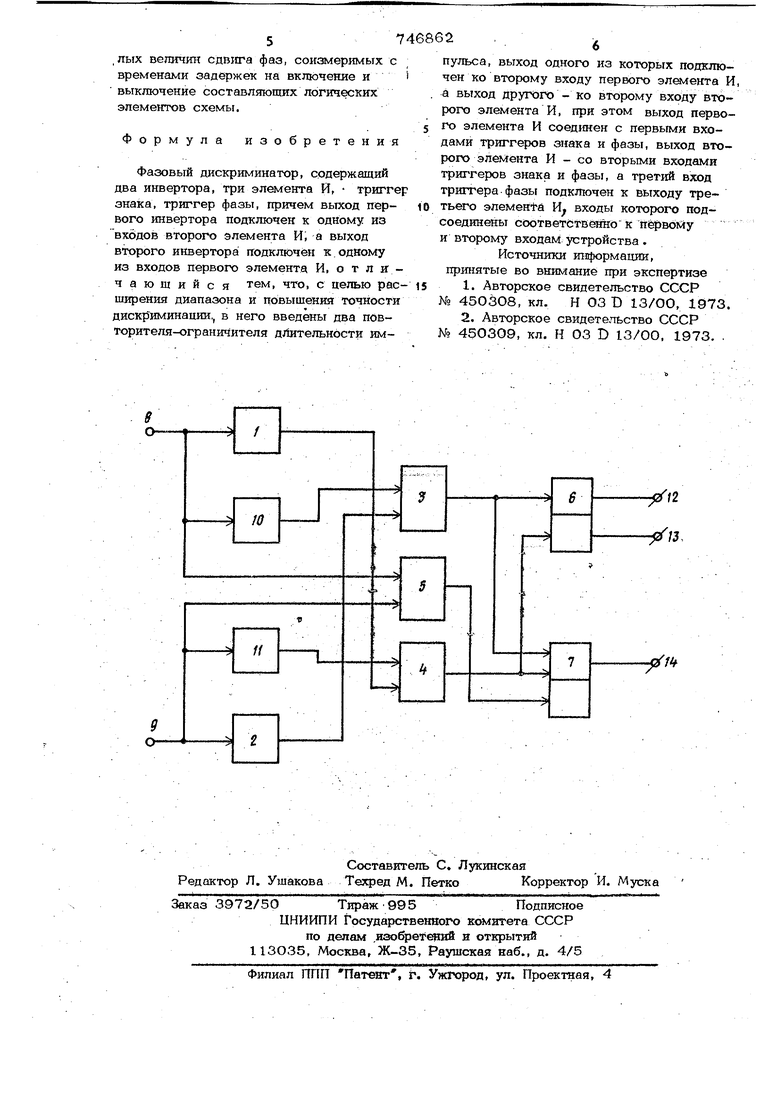

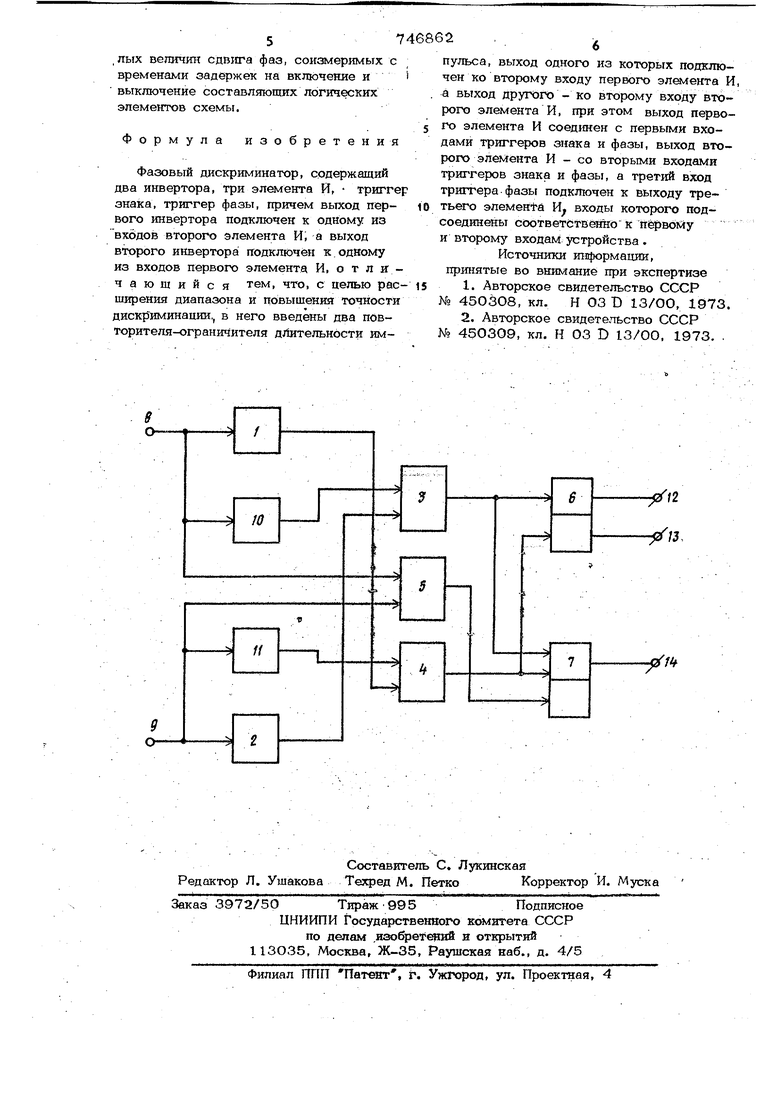

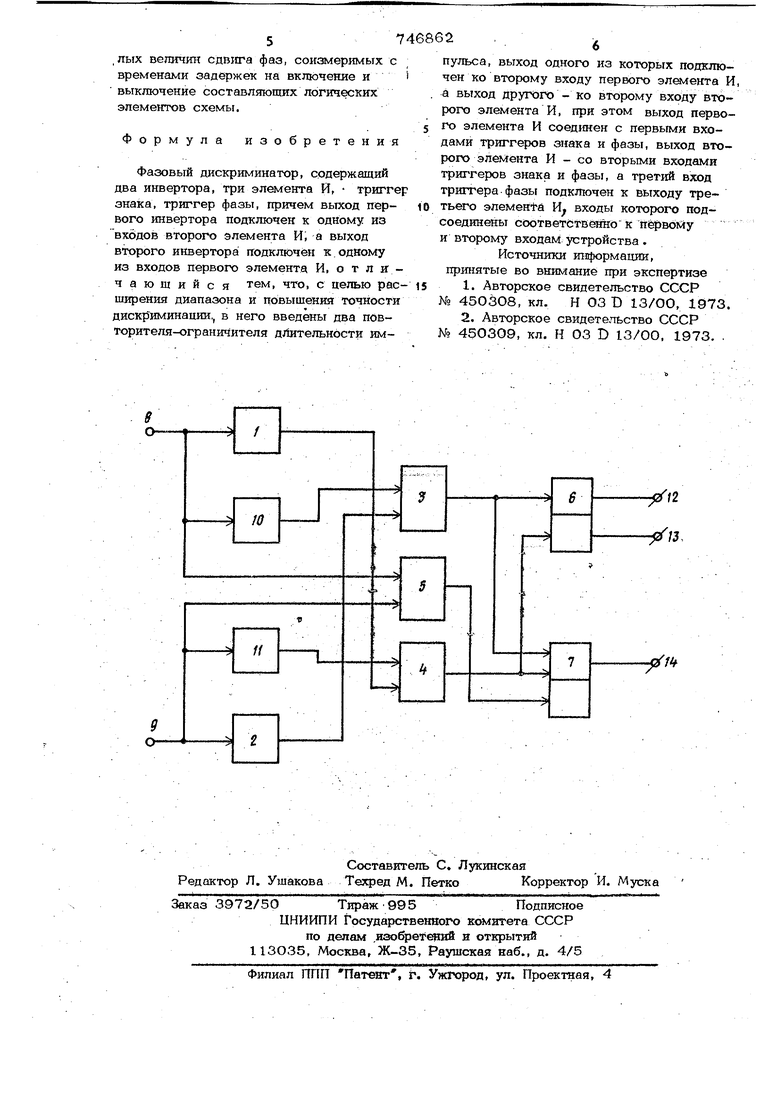

. , I . Изобретение относится к измерительной технике, оно предназначено для определения знака и величины сдвига фаз двух импульсных сигналов. Известен фазовой дискриминатор, содержащий формирователь прявмоугольных импульсов, два триггера, входные и выходные схемы И 1, Однако этот фазовый дискриминатор o6ecnetfflBaeT работоспособность только при входных импульсах малой длительности с величиной задержки между сигналами, превышающе длительность входного импульса. Известен также фазовый дистфиминатор, содержащий два импульсно-фаэовых различителя, каждый из которых состоит из триггера, инвертора и двух логических схем И, и логическую схему ИЛИ, входы которой подключены к выходам соответствующей логической схемы И каждого из импульсно-фазовых различителей, на входы которого поданы входные сигналы, а также две линии задержки, каждая из которых включена меж соответствующим входом дискриминатора и входом триггера соответствующего импульсно-фазового рааличителя, а каждый вход дискриминатора подключен непосредственно к входам инвертора и схемы И противоположного импульснофазового различителя 2 Однако в этом дйЬкрим1гааторе минимальная величина сдвига фаз ограничивается величиной времени линий задерж сдвиге фаз между вхбДНыкй сигналами меньшем, чем (,, сзагнал на выходе дискриминатора отсутствует, то есть схема не предназначена для определения величины сдвига фаз, меньшего, чем величина Тд. Кроме того, момент выключения выходного сигнала определяется не моментом появления сигнала на отстйощем входе дискриминатора (что соответствовало бы величине измеряемого сдвига фаз), а моментом появления этого сигнала на выходе линии задержки, ; Т.е. указанная схема имеет погреигаость 37 формирования длительности выходного сигнала на величину Фд . Цель изобретения - расширения диапазона и повышение точности дискриминации. Поставленная цель достигается тем, что в фазовый дискриминатор, содержащий два инвертора, три элемента И, триггер знака, триггер фазы, причем выход первого инвертора подключен к одному из входов второго элемента И, а выход второго инвертора йбМЙючён к одному из входов первого элемента И, введены два повторителя-ограничителя длительности импульса, вьтход одного из которых подключен1Шб1(б(й 1вШйу первого элек1ента И, а выход другого Ш второму входу ВТО1ЮГО элгаиента И, при этом выход пфвого элемента И соединен с первыми входами триггеров знака и фазы, вйХод второго элемента И еб вторйми входами тригге рюВ знака и фаЙ, а третий вход триггера ф1;ЭЬ1 Ш)11йвЬчен к выходу третьегЬ элемента И входы которого подсоединены соответcT&ekab к первому и второму входам устройства. На чертеже представлена структурная схема предлагаемого фазового дискриминатора. Этот дискриминатор содёржитР два, инверто|ра 1 и 2, три элемента И 3,4 и 5, триггер 6 знака, триггер 7 фазы, 9 две вхадные клеммы 8 и 9, два повторй ел:й--дграничителя iO и 11 длитёльytocfK Шпупьса, две выходные йлеммы 12 и 13 знака и выходную клемму 14 , фазы. - - ::. ;% Т-- -- Выход первого инвертора 1, вход коTbJDord соединен с входной KnoviMoft 8, подколочен к одному из входов второто элемен а И 4, а Выхсщ вторкях йнве|ртора 2, вход которого соединен второй входной клеммой 0, яодключен к ойнЬму из вхОйЙВ первого элемента Ti 3 Повто ритель-ограничитель id включен межйу входной клеммой 8 и элементом И 3, а повторитеяь-огранйчитейь 11 между входной клеммой 9 и вторьш эле ментом И 4. Выход первого эп&лента И соединен с одними Входами триггеров 6 и 7 знака и фазы, выход второго эле мента И 4 - с другШи Входами трйггеров 6 И 7 знака и фазы, а сбросовый Вход триггера 7 фазы подключен к вьгхо третьего элемента И 5, входы которого подсоединены соответственно к первой И второй входным клеммам 8 и 9. 2 Предлагаемый дискриминатор работает следующим образом. На входные клеммы 8 и 9 поступают меандровые сигналы одинаковой частоты. Если сигнал на входной клемме 8 опережает сигнал на входной клемме 9, то в момент прихода переднего фронта сигнала на входную клемму 8 на выходе повторителя-ограничителя 10 формируется короткий импульсный сигнал, по которому через первый элемент И 3 (на втором входе элемента И 3 присутствует разрешающий потенциал с выхода инвертора 2) тригг еры 6 и 7 устанавливаются ч единичное состояние. При поступлении второго задержанного по фазе сигнала на входную клемму 9, срабатывает третий элемент и 5, сигнал с выхода которого переводит в нулевое состояние триггер 7,.в результате чего на В Е 1ходной клемме 14 формируется импульрный сигнал, длительность которого )ЁЗЙВЙ& сдвигу фаз между входными сигналами. Состояние триггера 6 сохраняется до момента перемёнь знака сдвига фаз. При Опережении сигнала на входной йлетлме 9 триггф 7 устанавливается в единичное, триггер 6 в нулевое состояние по сигналу с выхода второго элемента И 4, на первый вход которого поступает сформиров анный повторителемограничителем 11 короткий импульс, а на второй вход - раарещаюший потенциал с выхода ийвёртор а 1. Формирование выходного сигнала на выходной клемме 14 осушествляетСЯ аналогично описанному BbtJiie установкой триггера 7 в нулевое состояние при поступлении на входную клемму 8 Йтстаюшего сигнала и совпадении обоих входных сет-налов на третьем элементе И 5. Введение в фазовый дискриминатор повторителей1ограничителей 1О и 11 обеспечивает включение выходного сигнала (характеризующего величину сдвига фаз) сразу же при поступлении Опережающего входного сигнала. Организация включения триггера 7 фазы по сигналам от первого и второго элт4ентов И 3 и 4 (входы которых управляются Ьт выходов инверторов 1 и 2) обеспечивает блокировку повторного включения триггера 7 при поступлении отстающего входного сигнала, а наличие третьё1ч) элемента И 5 обеспечивает при этом формирование сигнала выключения триггера 7, в результате чего повыщается точность измерения достаточно Ма,лых величин сдвига фаз, соизмеримых с временами задержек на включение и

выключение составл5тющих логических элементов схемы. Формула изобретения

Фазовый дискриминатор, содержащий два инвертора, три элемента И, тригге знака, триггер фазы, причем выход первого инвертора подключен к одному из входов второго элемента И, а выход BTXjporo инвертора подключен к.одному из входов первого элемента И, о т л я чающийся тем, что, с целью рас ширения диапазона и повышения точности дискриминации,, в него введены два повторителя-ограничителя длительности импульса, выход одного из которых подключен ко второму входу первого элемента И а выход другого - ко второму вхойу второго элемента И, при этом выход первого элемента И соединен с первыми входами триггеров знака и фазы, выход второго элемента И - со вторыми входами триггеров знака и фазы, а третий вход триггера фазы подключен к выходу третьего элемен а И входы которого подсоединены соответствеяно к пёрвойу и второму входам устройства . Источники информации, принятые во внимание при экспертизе

№ 4503О8, кл. Н 03 D 13/ОО, 1973.

№ 450309, кл, F 03 D 13/00, 1973. .

Авторы

Даты

1980-07-05—Публикация

1977-12-02—Подача