Изобретение относится к вычислительной технике, а именно к устройствам управления регенерацией динамической памяти ЭВМ,

Цель изобретения - повышение быстродействия за счет уменьшения числа обращений для регенерации памяти.

Сущность изобретения заключается в том, что при обращениях к памяти на запись или считывание происходит регенерация строк, указанных в младших разрядах адреса. При работе ЭВМ обращения могут идти по произвольным адресам, так что в течение

времени восстановления Тв. обычно равного 1 мс или 2 мс, некоторые строки будут перебираться неоднократно, а к другим возможно, совсем не будет обращений Равномерно распределенная во времени операция регенерации памяти гарантирует обращение к каждой строке за время Тв Для полного восстановления динамической памяти достаточно ввести операцию регенерации не по всем строкам, а лишь по тем по которым не было обращений за время Тв. В ЭТОЙ связи интервал времени Тв разделяется на две равные части. Во время

ю

XJ

первой контролируются все обращения к памяти. При обнаружении обращения запоминается этот факт для любой строки. По окончании первого интервала хранятся признаки обращений к тем строкам, по которым производилась запись или считывание. Во время второй части интервала Тв организуется регенерация тех строк памяти, к которым не было обращений.

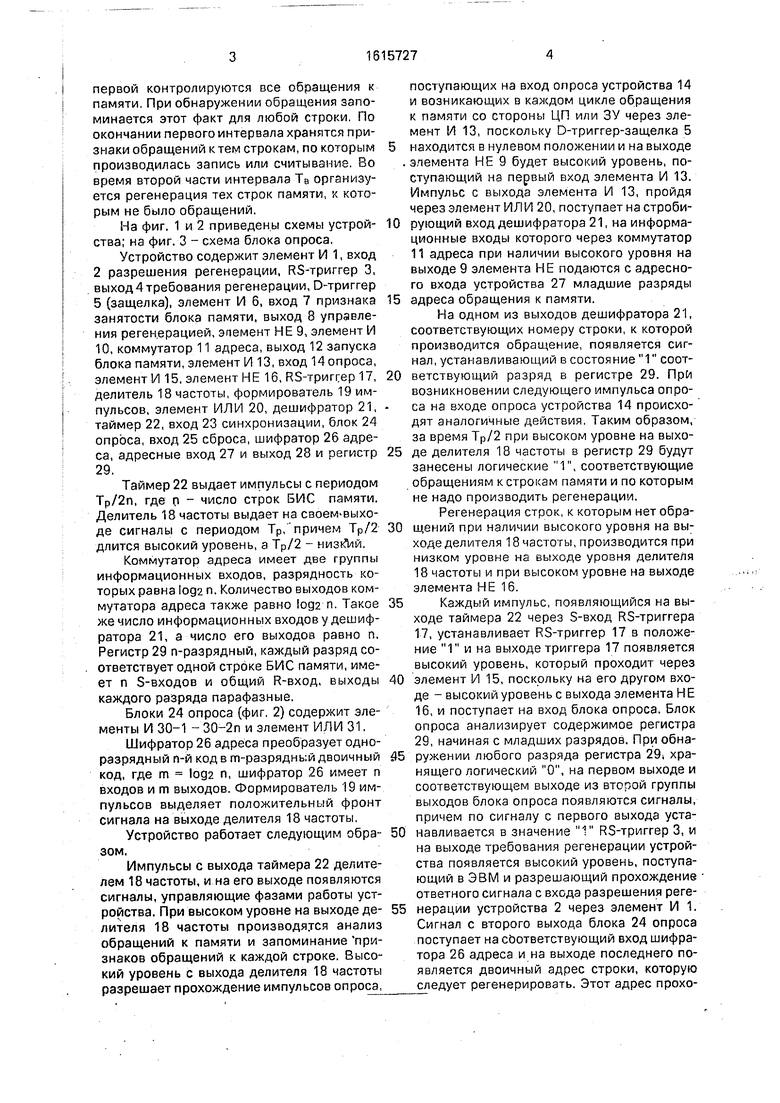

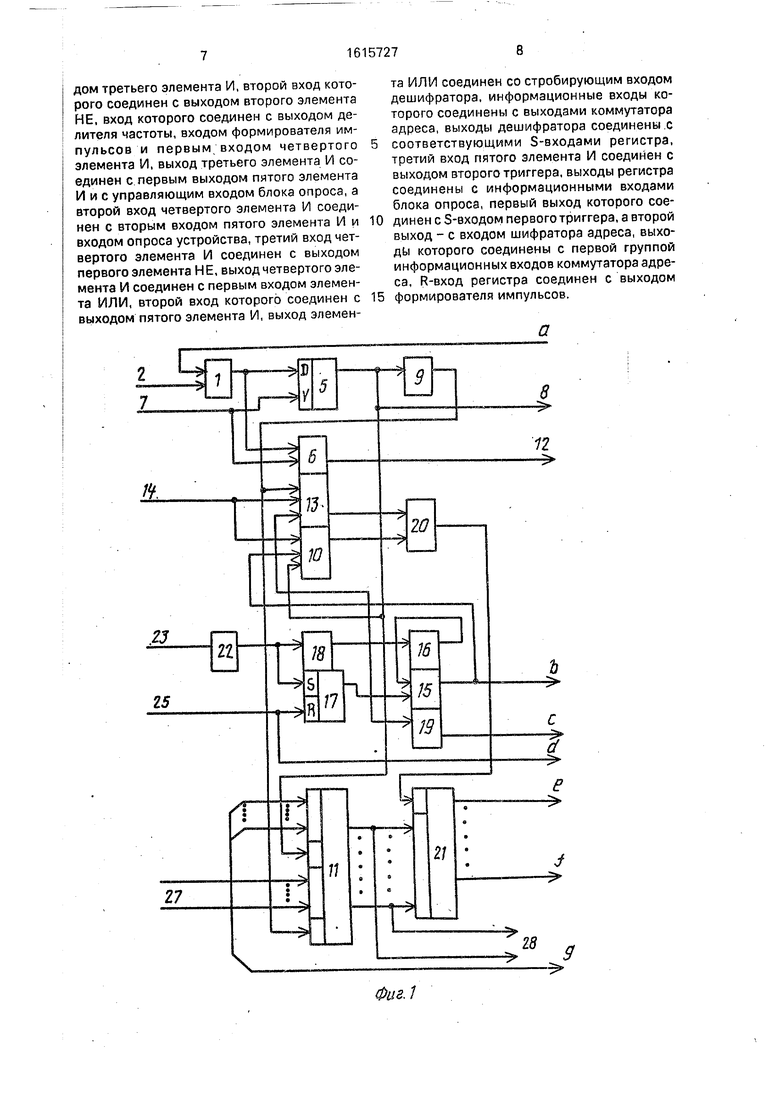

На фиг. 1 и 2 приведены схемы устрой- ства; на фиг. 3 - схема блока опроса,

Устройство содержит элемент И 1, вход 2 разрешения регенерации, RS-триггер 3, выход 4 требования регенерации, D-триггер 5 (защелка), элемент И 6, вход 7 признака занятости блока памяти, выход 8 управления регенерацией, элемент НЕ 9, элемент И 10, коммутатор 11 адреса, выход 12 запуска блока памяти, элемент И 13, вход 14 опроса, элемент Л 15, элемент Н Е 16, RS-триггер 17, делитель 18 частоты, формирователь 19 импульсов, элемент ИЛИ 20, дешифратор 21, таймер 22, вход 23 синхронизации, блок 24 опроса, вход 25 сброса, шифратор 26 адреса, адресные вход 27 и выход 28 и регистр 29,

Таймер 22 выдает импульсы с периодом Тр/2п, где о - число строк БИС памяти. Делитель 18 частоты выдает на своем-выхо- де сигналы с периодом Тр, причем Тр/2 длится высокий уровень, а Тр/2 - низЛ1й,

Коммутатор адреса имеет две группы информационных входов, разрядность которых равна 1од2 п. Количество выходов коммутатора адреса также равно loga п. Такое же число информационных входов у дешифратора 21, а число его выходов равно п. Регистр 29 п-разрядный, каждый разряд соответствует одной строке БИС памяти, имеет п S-входов и общий R-вход, выходы каждого разряда парафазные.

Блоки 24 опроса (фиг. 2) содержит элементы И 30-1 -30-2п и элемент ИЛИ 31,

Шифратор 26 адреса преобразует одноразрядный п-й код в т-разрядный двоичный код, где m 1092 п, шифратор 26 имеет п входов и m выходов. Формирователь 19 импульсов выделяет положительный фронт сигнала на выходе делителя 18 частоты.

Устройство работает следующим обра- зом.

Импульсы с выхода таймера 22 делителем 18 частоты, и на его выходе появляются сигналы, управляющие фазами работы устройства. При высоком уровне на выходе де- лителя 18 частоты производятся анализ обращений к памяти и запоминание признаков обращений к каждой строке. Высокий уровень с выхода делителя 18 частоты разрешает прохождение импульсов опросз

поступающих на вход опроса устройства 14 и возникающих в каждом цикле обращения к памяти со стороны ЦП или ЗУ через элемент И 13, поскольку D-триггер-защелка 5 находится в нулевом положении и на выходе элемента НЕ 9 будет высокий уровень, по- ступаюа ий Н8 первый вход элемента И 13. Импульс с выхода элемента И 13, пройдя через элемент ИЛИ 20, поступает на строби- рующий вход дешифратора 21, на информационные входы которого через коммутатор 11 адреса при наличии высокого уровня на выходе 9 элемента НЕ подаются с адресного входа устройства 27 младшие разряды адреса обращения к памяти.

На одном из выходов дешифратора 21, соответствующих номеру строки, к которой производится обращение, появляется сигнал, устанавливающий в состояние 1 соответствующий разряд в регистре 29. При возникновении следующего импульса опроса на входе опроса устройства 14 происходят аналогичные действия. Таким образом, за время Тр/2 при высоком уровне на выходе делителя 18 частоты в регистр 29 будут занесены логические 1, соответствующие обращениям к строкам памяти и по которым не надо производить регенерации.

Регенерация строк, к которым нет обращений при наличии высокого уровня на выходе делителя 18 частоты, производится при низком уровне на выходе уровня делителя 18 частоты и при высоком уровне на выходе элемента НЕ 16.

Каждый импульс, появляющийся на выходе таймера 22 через S-вход RS-триггера 17, устанавливает RS-триггер 17 в положение 1 и на выходе триггера 17 появляется высокий уровень, который проходит через элемент И 15, поскольку на его другом входе - высокий уровень с выхода элемента НЕ 16, и поступает на вход блока опроса. Блок опроса анализирует содержимое регистра 29, начиная с младших разрядов. При обнаружении любого разряда регистра 29i хранящего логический О, на первом выходе и соответствующем выходе из второй группы выходов блока опроса появляются сигналы, причем по сигналу с первого выхода устанавливается в значение 1 RS-триггер 3, и на выходе требования регенерации устройства появляется высокий уровень, поступающий в ЭВМ и разрешающий прохождение ответного сигнала с входа разрешения регенерации устройства 2 через элемент И 1. Сигнал с второго выхода блока 24 опроса поступает на сЬответствующий вход шифратора 26 адреса и на выходе последнего появляется двоичный адрес строки, которую следует регенерировать. Этот адрес прохоком уровне на выходе триггера 5 и появляется на информационных входах дешифратора 21,

Завершив очередной обмен с памятью ЭВМ выставляет сигнал разрешения регенерации устройства, который, пройдя через элемент И1, попадает на D-вход D-триггера- защелки 5, на вход V которого подается разрешающий сигнал с входа 7 признака занятости устройства, в результате-О-триг- гер-защелка 5 устанавливается в состояние 1 и на его выходе появляется высокий уровень, который разрешает прохождение сигнала с входа опроса устройства 14 через элемент И 10, а также прохождение адреса восстановления через коммутатор 11 адреса. На выходе элемента НЕ 9 появляется низкий уровень, который блокирует прохождение сигнала опроса через элемент

Высокий уровень с выхода триггера-защелки 5 поступает на выход управления регенерацией устройства. Одновременно с установкой триггера-защелки 5 на выходе элемента И 6 появляется импульс, поступающий на выход 12 запуска блока памяти и оттуда в память, отчего Запускается временная диаграмма работы памяти при регенерации и снимается высокий уровень на входе 7 признака занятости блока памяти В результате триггер-защелка 5 хранит состояние 1 до появления очередного высокого уровня на входе 7.

Блок управления памятью, входящий в состав ЭВМ, вырабатывает управляющие сигналы, необходимые для регенерации памяти по сигналу с выхода управления регенерацией устройства 8, и, получив адрес строки с адресного выхода устройства 8 который проходит через коммутатор 11 адреса благодаря высокому уровню на выходе триггера-защелки 5, производит регенерацию.

Появляющийся на выходе элемента И

10 импульс по сигналу опроса, возникающего и в цикле регенерации, проходит через элемент ИЛИ 20 и поступает на стробирую- щии вход дешифратора 21, на информаци онные входы которого подан адрес регенерации, т.е. номер строки, по которой производится регенерация. В результате на выходе дешифратора 21 появляется импульс, устанавливающий разряд регистра У, по которому осуществляется регенерация, в состояние 1.

В конце цикла регенерации на входе сброса устройства 25 появляется импульс поступающий на R-входы триггеров 17 и з которые устанавливаются в состояние О в результате чего снимается сигнал с входа

4 т 50 55 -

блока 24 опроса и на выходе требования регенерации устройства 4.

По очередному импульсу на выходе таймера 22 цикл работы устройства повторяет- 5 ся до тех пор, пока все разряды регистра 29 не будут установлены в состоянеие I, что соответствует восстановлению всех строк БИСов памяти. С этом случае с приходом очередного импульса с выхода таймера 22 и 0 установкой в состояние 1 RS-триггера 17 с выхода элемента И 15 на вход блока 24 опроса придет высокий уровень и на первом выходе блока опроса сигнал не появится

-Состояние всех 1 в регистре 29 хра- Ь нится до перехода уровня на выходе делителя частоты с низкого на высокий. При этом на выходе формирователя 19 импульсов появляется импульс, который сбрасывает все разряды регистра 29 в нулевое состояние и Затем повторяется работа устройства при высоком уровне на выходе делителя.18 частоты.

Формула изобретения 25Устройство управления регенераиией

динамической памяти, содержащее два триггера, таймер, коммутатор адреса два .элемента И, первый элемент НЕ, причем выход первого триггера является выходом 30 требования регенерации устройства и соединен с первым входом первого злемента И второй вход которого соединен с входом разрешения регенерации устройства, а выход с D-входом второго триггера и первым вхо- J5 дом второго элемента И, второй вход которого соединен с входом признака занятости блока памяти устройства и входом второго триггера, выход второго элемента И соединен с вь1ходом запуска блока памяти устройства 40 а выход второго триггера является выходом управления регенерацией устройства и соединен с первым управляющим входом коммутатора адреса и входом первого элемента НЕ выход которого соединен с вторым управлять ющим входом коммутатора адреса, вторая группа информационных входов коммутатора адреса соединена с адресным входом устройства, выходы коммутатора адреса являются адресным выходом устройства, отличаю - 0 щ е е с я тем, что, с целью повышения быстродействия, оно дополнительно содержит третий, четвертый и пятый элементы И, третий триггер, элемент ИЛИ, делитель частоты формирователь импульсов, дешифратор ре- 5 гистр, блок опроса, шифратор адреса, второй элемент НЕ, причем вход делителя частоты, соединен с выходом таймера и S-входом третьего триггера. R-вход которого соединен с R-входом первого триггера и входом „сброса устройства, а внход - с первым вхо- :

дом третьего элемента И, второй вход которого соединен с выходом второго элемента НЕ, вход которого соединен с выходом делителя частоты, входом формирователя импульсов и первым входом четвертого элемента И, выход третьего элемента И соединен с первым выходом пятого элемента И и с управляющим входом блока опроса, а второй вход четвертого элемента И соединен с вторым входом пятого элемента И и входом опроса устройства, третий вход четвертого элемента И соединен с выходом первого элемента НЕ, выход четвертого элемента И соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, выход элемента ИЛИ соединен со стробирующим входом дешифратора, информационные входы которого соединены с выходами коммутатора адреса, выходы дешифратора соединены .с

соответствующими S-входами регистра, третий вход пятого элемента И соедийен с выходом второго триггера, выходы регистра соединены с информационными входами блока опроса, первый выход которого соединен с З-входом первого триггера, а второй выход - с входом шифратора адреса, выходы которого соединены с первой группой информационных входов коммутатора адреса, R-вход регистра соединен с выходом

формирователя импульсов.

а

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления памятью | 1977 |

|

SU748414A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1990 |

|

SU1785034A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1377864A1 |

| Устройство для обработки изображений | 1986 |

|

SU1316003A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1587594A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

Изобретение относится к вычислительной технике. Целью изобретения является повышение быстродействия за счет уменьшения числа обращений для регенерации памяти. Сущность изобретения заключается в том, что в известное устройство, содержащее два триггера, таймер, коммутатор адреса, два элемента И, элемент НЕ, дополнительно введены три элемента И, третий триггер, элемент ИЛИ, делитель частоты, формирователь импульсов, дешифратор, регистр, блок опроса (регистра), шифратор адреса и второй элемент НЕ. В предлагаемом изобретении при обращении к памяти на запись или считывание происходит регенерация строк, указанных в младших разрядах адреса. При работе ЭВМ обращения могут идти по произвольным адресам, так что в течение времени восстановления некоторые строки будут перебираться неоднократно, а к другим возможно совсем не будет обращений. Равномерно распределенная во времени операция регенерации памяти гарантирует обращение к каждой строке за время Tв. Для полного восстановления динамической памяти достаточно ввести операцию регенерации не по всем строкам, а лишь по тем, по которым не было обращений за время Tв. В этой связи интервал времени Tв разделяется на две равные части. Во время первой контролируются все обращения к памяти. При обнаружении обращения запоминается этот факт для любой строки. По окончании первого интервала хранятся признаки обращений к тем строкам, по которым производились запись или считывание. Во время второй части интервала Tв организуется регенерация тех строк памяти, к которым не было обращений. 3 ил.

Фаг. 7

29

и

26

у

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Техническое описание, ч | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сообщения арматуре предварительных напряжений при изготовлении железобетонных элементов центробежным способом | 1935 |

|

SU50384A1 |

Авторы

Даты

1990-12-23—Публикация

1989-01-16—Подача