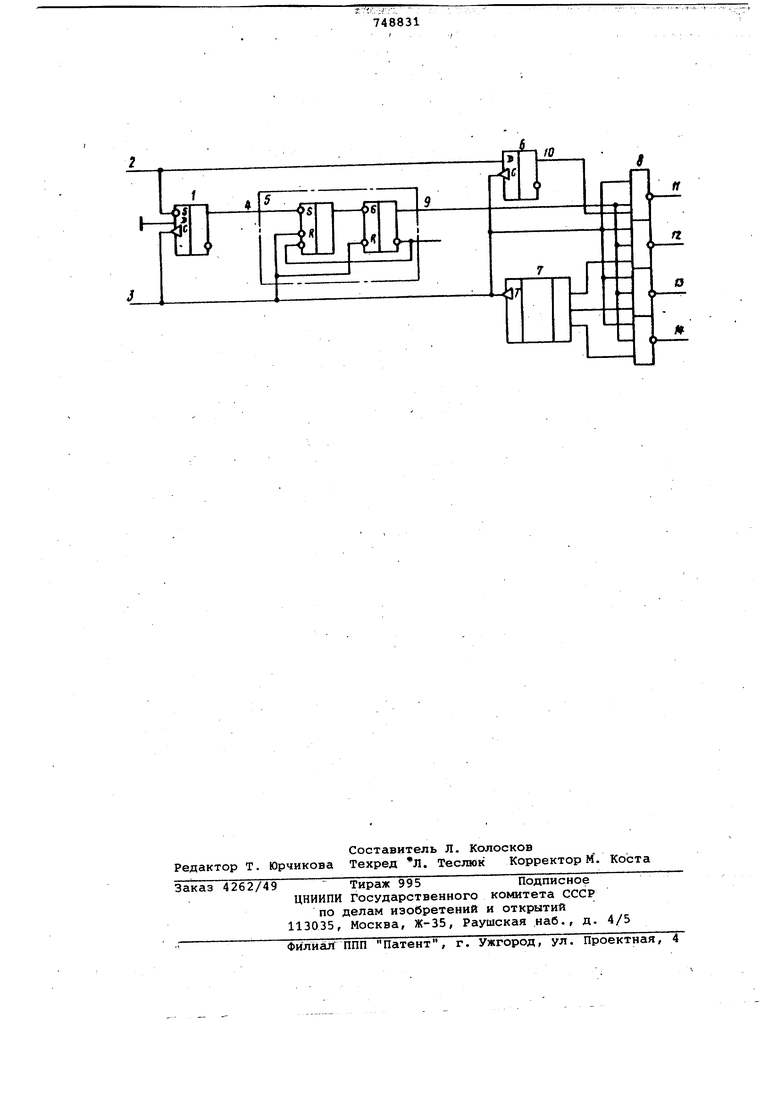

Изобретение относится к импульсной технике. Синхронизатор импульсов может быть использован при измерении и формировании временных интервалов, Известны устройства, обеспечивающие формирование импульсов, синфазных последовательности тактовых импульсов, по асинхронным импульсам запроса, содержащие элементы памяти импульсов запроса и элементы привязки сформированного потенциала запроса к тактовым импульсам 1. Данное устройство при поступлении импульсов запроса с нестабильным периодом следования, причем минимальная величина перепада может быть меньше периода следования, & средняя всегда больше, не обеспечивает полного соответствия количества импульсов опроса формируемых на выходе, количеству импульсов, поступающих на шину запроса (сбой типа потеря импульса згпроса Х близким по технической сущности к изобретению является устройство, содержащее блок пё1мяти импульсов запроса, соединенный входом с шиной запроса, и блок памяти тактовых импульсов, соединенный входом с шиной тактовых импульсов, анализатор нуля .{2 . Однако такое устройство обладает малой разрешающей способностью, равной периоду следования тактовых импульсов . Его быстродействие ниже предельного для устройств на тактируемых триггерах на величину задерж и в анализаторе нуля. Целью изобретения является повышение разрешающей способности и быстродействия синхронизатора импульсов. Цель достигается тем, что в синхронизатор импульсов, содержащий триг.гер памяти импульсов запроса, установочный вход которого соединен с шиной запроса, а сйнхровход - с шиной тактовых импульсов, блок памяти тактовых импульсов, тактирукнций вход которого соединен с шиной тактовых импульсов, и выходные вентили, введены триггер уточнения привязки, синхровход которого соединен с шиной тактовых импульсов, информационный вход - с шиной запроса, а выход - с первым входом первого выходного вентиля, и счетт чик, выходы которого подключены к первым входам остальных выходных венТиЛей, а вход соединен с шиной тактовых импульсов и с вторыми входами выходных вентилей, третьи входы которых подсоединены к выходу блока па мяти тактовых импульсов, входом подключенного к выходу триггера памяти импульсов запроса. Блок памяти тактовых импульсов выполнен в виде двух триггеров, выхо первого,из которых соединен с входом установки второго триггера, при этом один выход второго триггера подключе к входу сброса первого триггера, а другой выход является выходом блока памяти, входом которого является вхо установки первого триггера, а с тактирующим входом блока памяти тактовых импульсов связаны входы сброса обоих триггеров. На чертеже представлена функциональная схема синхронизатора импульсов, который содержих триггер 1 памяти импульсов запроса, установочный вход которого соединен с шиной 2 импульсов запроса, синхровход - с шино 3 тактовых импульсов, а выход - с установочным входом 4 первого триггера блока 5 памяти тактовых импульсов. Тактирующий вход блока 5 и синхровходы триггера 6 уточнения привяз ки и счетчика 7 соединены с шиной тактовых импульсов. Код временного п ложения импульсов запроса фиксируется на выходах вентилей 8, входы которых стробируются тактовыми импульсами с шины 3 и стробом с шины 9 раз решения опроса. Информация о временном положении импульса запроса.в целых периодах тактовых импульсов поступает на входы вентилей 8 со счетчи ка 7 и о положении его внутри периода - с выхода 10 триггера б и передается на выходные шины 11-14. Работает синхронизатор импульсов следующим образом. Поступление импульса запроса с шины 2 на установочный вход триггера 1 переводит его в состояние 1 независимо от логического уровня на входе С. Тем самым обеспечивается надежная фиксация прихода импульса запроса. Блок 5 обладает свойством формирования уровня на шине 9, идентичного уровню на входе 4, только по приходе отрицательного фронта импульса на тактирующий вход, причем Ьез обрезки его по длительности сигналом с управляющего эхода 4. Триггер 1 сбрасывается по входу синхронизации по приходе отрицательного фронта импульса с шины 3. Таким образом, триггер 1 находится в состоянии 1 после прихода импульса с шины -2 и сбрасывается лишь после фиксации его состояния на шине 9 бло ка 5. Триггер 6 отрицательным фронто тактового импульса шины 3 фиксируется в состоянии О, если момент прихода фронта попал на вершину отрицательного импульса запроса. Этим обес печивается уточнение измерения положения импульса запроса. Импульс опроса формируется совпадением на входах вентилей 8 строба с шины 9 разрешения опроса и тактовых импульсов с Шины 3. Данный синхронизатор импульсов по сравнению с прототипом имеет более высокую разрешающую способность. Она определяется стабильностью длительности импульса запроса. При длительности импульса запроса, точно равной половине периода тактовых импульсов, разрешающая способность равна половине периода,т.е. вдвое выше, чем у прототипа. Быстродействие предложенного синхронизатора равно предельному быстродействию устройств на тактируемых триггерах и предельной рабочей частоте отдельного триггера. Формула изобретения 1.Синхронизатор импульсов, содержащий триггер памяти импульсов эапроЬа, установочный вход которого соединен с шиной запроса, а синхровход с шиной тактовых импульсов, блок памяти тактовых импульсов, тактирующий вход которого соединен с шиной тактовых импульсов и выходные вен±или,о тличающийся тем, что, с целью повышения разрешающей способности и быстродействия синхронизатора,в него введены триггер уточнения привязки, синхровход которого соединен с шиной тактовых импульсов,информационный вход - с шиной запроса,а выход - с первым входом первого выходного вентиля,и счетчик,выходы которого подключены к первым входам остальных выходных вентилей,а вход соединен с шиной тактовых имйульсов и свторыми входами выходных вентилей,третьи входы, ко- торых подсоединены к выходу блока памяти тактовых импульсов,вход которого подключен к выходу триггера памяти импульсов запроса. 2.Синхронизатор импульсов по п. 1, отличающийся тем, что блок памяти тактовых импульсов выполнен в виде двух триггеров, выход первого из которых соединен с входом установки второго триггера, один вход которого подключен к входу сброса первого триггера, а другой выход является выходом блока памяти, входом которого является вход установки первого триггера, ас тактирующим входом блока памяти тактовых импульсов связаны входы сброса обоих триггеров. Источники информации, принятые во внимание при экспертизе 1. Электроника, 1971, № 11, с. 51. 2.Авторское свидетельство СССР по заявке №2522730, кл. Н 03 К 5/00,1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1984 |

|

SU1201842A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1985 |

|

SU1290325A1 |

| Многоканальный формирователь одиночных импульсов | 1985 |

|

SU1243115A1 |

| Устройство для устранения влияния дребезга сигнала | 1989 |

|

SU1725371A1 |

| Устройство для ввода информации от двухпозиционных датчиков | 1984 |

|

SU1156053A1 |

| Устройство для сопряжения микро-ЭВМ с табло индикации | 1986 |

|

SU1376090A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1985 |

|

SU1277126A1 |

Авторы

Даты

1980-07-15—Публикация

1978-04-10—Подача