1

Изобретение относится к вычнспи. тельной технике и предназначено для использования в специализированных. ЦВМ.

Известны арифметические устройст ва работающие с информацией представленной в виде векторов, предназначенные для решения задач с большим количеством тригонометрических функций и содержащие сдвиговые регистры, сумматоры-вычитатели и коммутирующие блоки. Такие устройства способны вычислоть тригонометрические функции .arctgX l.

Однако они обладают недостаточно высоким быстродействием.

Наиболее близким к изобретению по технической сущности является арифметическое устройство, работающее по алгоритму Волдера:/ «ч V ч - .V. ol л .,« ,..ч

-., . /,.

eiM-e-r i -.

(1)

и позволяющее вычислять

(у собХ-Х а п-к) (2) (Х. аю Y.tn

ТЛ

или«кУуТ Туг (3)

. ;

где К У- QI - значения координат и

угла на i -и итерации; , - функция, показывающая направление вращения и равн;ая: для соотношений (2)

j.3iene.;(4)

15 для соотношений (3)

e,.xs g-nC-y,(5)

где Ck; - угловая постоянная, равная «rclg ) .

„К- коэффициент удлинения вектора;

Л - начальные данные;

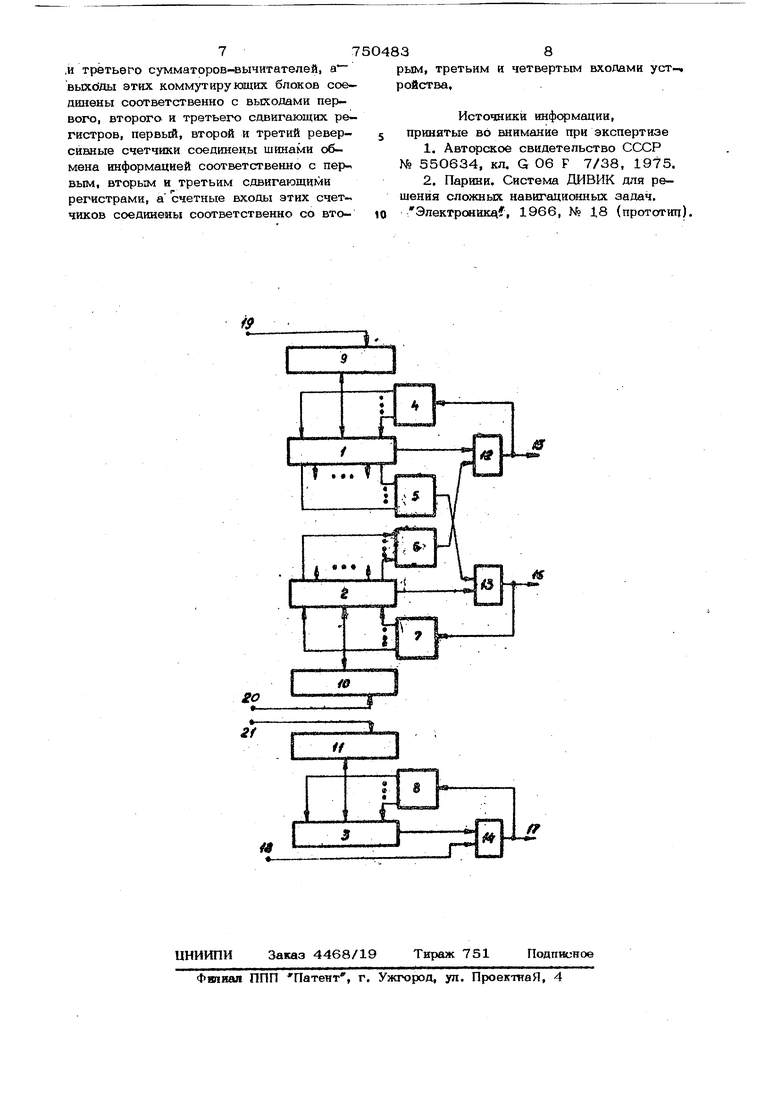

- номер итерации ( 2, 3, . . . ,г). А 1ифметическое устройство, реализующее алгор1ггм, содержит три сдвиговых регистра, три сумматора-вычитателя и . два коммутирующих блока, причем выходы первого и второго сдвигаюших регистров подключены соответственно ко входам первого и второго коммутирующих блоков, выходы младших разрядов этих регистров подключены к первым входам соответственно первого и второго сумма торов-вычитателей, ко вторым входам которых подключены выходы соответственно второго п первого коммутирующих блоков, выход младшего разряда третьего сдвигающего регистра соединен с -первым входом третьего суммато ра-вычитателя, второй вход которого соединен с первым входом устройства, выходы первого, второго и грегьего сумматоров-вычитателей соодяиолы соответственно с первькл, вто- ры.г И грегьим выходами устройства 21. Медостэтком этого арифметического устройства является недостаточное быстр деистЕнс, определяемое временем выгюлио пил операции поворота вектора приблнаигелыю равным тл тактов, где п - разряд ность глгерандов. Цель иэобрьтения - повышение быстродейстпия а|.П фметического устройства Волдера,, Иосгавленпия цель достигается тем, vtTo а арифметическое устройство, содержа:г1ее три сдвигающих регистр, Tpv сум магоро--выч ггателя и два коммутирующих блока, примем выходы первого и второго сдвигающих регистров подключены cooT ветствэнчо ко входам первого и второго коммутируюпхих блоков, выходы младших разрядов эгпх регистров подключегш к liepBbiM входам соответственно первого и второго сумматора-вычитателей, ко. вто- рыпу входам которых.подключены выходы соотоетственно второго и первого комму- тирующих блоков, выход младшего разряд третьего сдвигающего регистра соединен с первым входом третьего сумматора-«ы читателя, второй вход которого соединен с первым входом устройства, выходы пер вого, второго и третьего сумматора-вы- читателей соединены соответственно с первым, вторым и третьим выходами устройства, дополнительно ввепены третий, четвертый и пятый коммутирующие блоки и первый, второй и третий реверсивные счетчики, причем входы третьего четвертого и пятого коммутирующих блоков соединены соответственно с выходами первого, второго и третьего суммато ов-вычитателей, а выходы этих коммутиующих блоков соедтшены соответственно входами первого, второго и третьего двигающих регистров, первый, второй и ретий реверсивные счетчики соединены инами обмена информацией соответствено с первым, вторым и третьим сдвигаюими регистрами, а счетные входы этих счетчиков соединены соответственно со вторым, третьим и четвертым входами устройства. При работе устройства учитывается тот факт, что старшие (1 -2) разрядов на 1 -и переменных X; итерации могут изменяться только переносами или займами из младших (h-l +2) разрядов. Это дает возможность производить вычисления по алгоритму (1) в два этапа: на i -той итерации вначале (как и в известных устройствах за () тактов производится суммирование (вычитание) младших разрядов на комбинационных последовательных сумматорах-вычитателях, а затем за один такт выполняется суммирование старших разрядов с переносом (займом) из младших разрядов в счетчиках. Таким образом, чем больше номер итерации, тем быст- . рее она выполняется. На чертеже показана структурная схема предлагаемого устройства. Схема содержит сдвигающие регистры 1- 3, коммутирующие блоки 4 - 8, реверсивные счетчики 9-11, сумматорывычитатели 12 - 14, выход 15 X, выход 16 У, выход 172, выход 18 угловой постоянной, счетные входы 19-21 счетчика. При работе по алгоритму (1) устройство работает следующим образом 2X ; , У , ив; хранятся соответственно в сдвигаюших регистрах 1-3 ( -2) старших разрядов Х , У-, и Q; переданы в счетчики 9 - 11 соответственно. С началом очередной итерации по ко- . из устройства управления коммутирующие блоки 5 и 6 соединяют соответствующие выходы регистров 1 и 2 со входами сумматоров-вычитателей 13 и 12 так, что на вход сумматора-еычитателя 13 поступает Х-,-2 а на вход сумматора-вычитателя 12 поступаетУ(- коммутирующие блок 4, 7 и 8 соединяют соответствующие входы регистров 1 и 2с выходами суммато- ров-вычитателей 12 14 так, чтобы значения сумм (разностей) (n-i +2) младших разрядов координат и угла запнсывались в (h -i +2) младших разря- дов сдвигающих регистров. Значение Ч , с вькода сдвигающего регистра 1 подается на второй вход сум матора-вычитателя 12, где в соответствии с вычитается (суммируется) с ч/, 2 ) , поступающим с выхода ком мутирующего блока 6, Значение (П-/+2 младших разрядов -f /i , полученное на выходе сумм тора-«ычитателя 12, записывается через коммутирующий блок 4 в (п-| +2) младших разрядов сдвигаю- щего регистра 1. Аналогичным образом производится запись младших разрядов Vj-f.;) и Sj-f. через коммутирующие блоки 5 и 8 в (п-| +2) младших разрядов, сдвигающих регистров 2 и 3. После вьшолнения (n-i +2) тактов сдвига в младших разрядах сдвигающих регистров арифметического устройства получают (n-i +2) младших разрядов ( 1 +)-х значений координат и угла, а также сформированы значения переносов из этих разрядов в старшие. Процесс сдвига заканчивается. Затем в устройстве управления анализируются значения переносов, полученных на выходах сумматоров и поступающих в устройство управления по линиям 15 17. При этом, если значение переноса при образовании Х(- равно 1 ign У) к старшим разрядам координаты , хранящимся в счетчике 9, . прибавляется 1, поступающая из устройства управления по входу 19. Если же значение переноса при образовании Х) равно и-Sign -, :б д-пУ; , к старшим разрядам координаты х - прибавляется -1. При переносе, равном О, содержимое счетчика 9 остается без изменений. Если значение переноса при образовании УН 4 равно и ,j - eignX;, к старшим разрядам координаты У; . хрангоцимся в счетчика Ю, прибавляется , поступающая из устройства управ ления по входу 2О. Если же значение переноса при образовании У равно и 6ig;n fe, i У ftig X;, к старшим разрядам координаты У; , прибавляется -. При переносе, равном О, содержимое счетчика 1О остается без изменений. Если значение переноса при образоваНИИ 0 14;, рашо ,- - 1, к старшим разрядам значения угла 0 -, , хранящимся в счетчике 11, прибавляется 1, поступающая из устройства управления цо входу 21. Если же значение перено-- са при образовании 9-, равно и i fe,, - +li к старшим разрядам угла б; прибавляется . При переносе, равном О, содержимое счетчика 11 остается без изменений. После образования старших разрядов переменных их значения .по шинам обмена информации передаются в соответствующие разряды сдвигающих регистров, а затем ( -1) старших разрядов передаются из регистров в счетчики для выполнения следующей итерации. На этом итерация заканчивается, и процесс повторяется до вьшолнения заданного количества итераций. В конце операции результаты х, гнл Ч ®гч-х огут быть сняты с соответствующих им выходов 15 - 17. Эффективность изобретения заключается в повышении быстродействия арифметического устройства приблизительно в два раза, достигаемым за счет выполнения суммирования старших разрядов, с переносом из мпатикх. разрядов, в счетчиках за один такт. Формула изобретения Арифметическое устройство, содержащее три сдвигающих регистра, три сумматора-вычитателя и два коммутирующих блока, причем вьосоды первого и второго сдвигающих регистров подключены соответственно ко входам первого и второго коммутирующих блоков, выходы младших разрядов этих регистров подключены к первым входам соответственно первого и второго с тиматоров-вычитагелей, ко вторым входам которых подключены выходы соответст-венно второго и первого коммутирующих блоков, вьосод младшего разряда третьего сдвигающего регистра соединен с первым входом третьего сумматора-вычитателя, второй вход которого соединен с первым входом устрой- ройства, выход первого, второго и третьего сумматоров-вычитателей соединены соответственно с первым, вторым и третьим выходами устройства, отлиающиеся тем, что, с целью поышения быстродействия устройства, в его введены третий, четвертый н пятый оммутирующие блоки и первый, второй третий реверсивные счетчики, причем ходы третьего, четвертого и пятого оммутирующих блоков соединены соотетственно с выходами первого, второго

,и третьего сумматоров- ычитателей, а выходы этих коммутирующих блоков соединены соответственно с выходами первого, второго и третьего сдвигающих регистров, первый, второй и третий реверсивные счетчики соединены шинами обмена информацией соответственно с первым, вторым и третьим сдвигающими регистрами, а счетные входы этих счет чиков соединены соответственно со вторым, третьим и четвертым входами уст-ч ройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР NO 550634, кл. G 06 F 7/38, 1975.

2.Парив и. Система ДИВИК для решения сложных навигационных задач.

Электронику, 1966, № 18 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1975 |

|

SU550634A1 |

| Устройство для вычисления тригонометрических функций | 1981 |

|

SU1003079A1 |

| Устройство для преобразования компонент тензора | 1978 |

|

SU734703A1 |

| Арифметическое устройство | 1975 |

|

SU547765A1 |

| Арифметическое устройство | 1975 |

|

SU538363A2 |

| Устройство для преобразованияКООРдиНАТ | 1979 |

|

SU836636A1 |

| Цифровой функциональный преобразователь | 1975 |

|

SU607223A1 |

| Устройство для определения среднего арифметического значения | 1989 |

|

SU1658169A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

1J

ё

/в

10

« С

ff

г

Авторы

Даты

1980-07-23—Публикация

1978-05-04—Подача