1

Изобретение относится к вычислительной технике, особенно к специализированным вычислителям и предназначено для вычисления функций вида Y sin0 и X созв.

Известно устройство, содержащее регистры, сумматоры-вЫчитатели, сдвигающие регистры, постоянное запоминающее устройство и устройство управления с недостаточно высоким временем вычисления синуса и косинуса, равным , где t - период следования тактовых импульсов, an - разрядность регистров 1.

Наиболее близким по технической сущности к изобретению является устройство, для вычисления синусно-косинусных функций, содержащее четыре регистра, два сдвигающих регистра, три сумматора-вычитателя постоянное запоминающее устройство и блок управления 2.

Устройство позволяет реализовать итерационные методы вычисления гармонических функций, однако достаточно медленно действующее (время вычисления синуса и косинуса равно Т , где т - период следования тактовых импульсов, п - разрядность регистров) и достаточно сложное.

Цель изобретения - повыщение быстродействия и упрощение устройства.

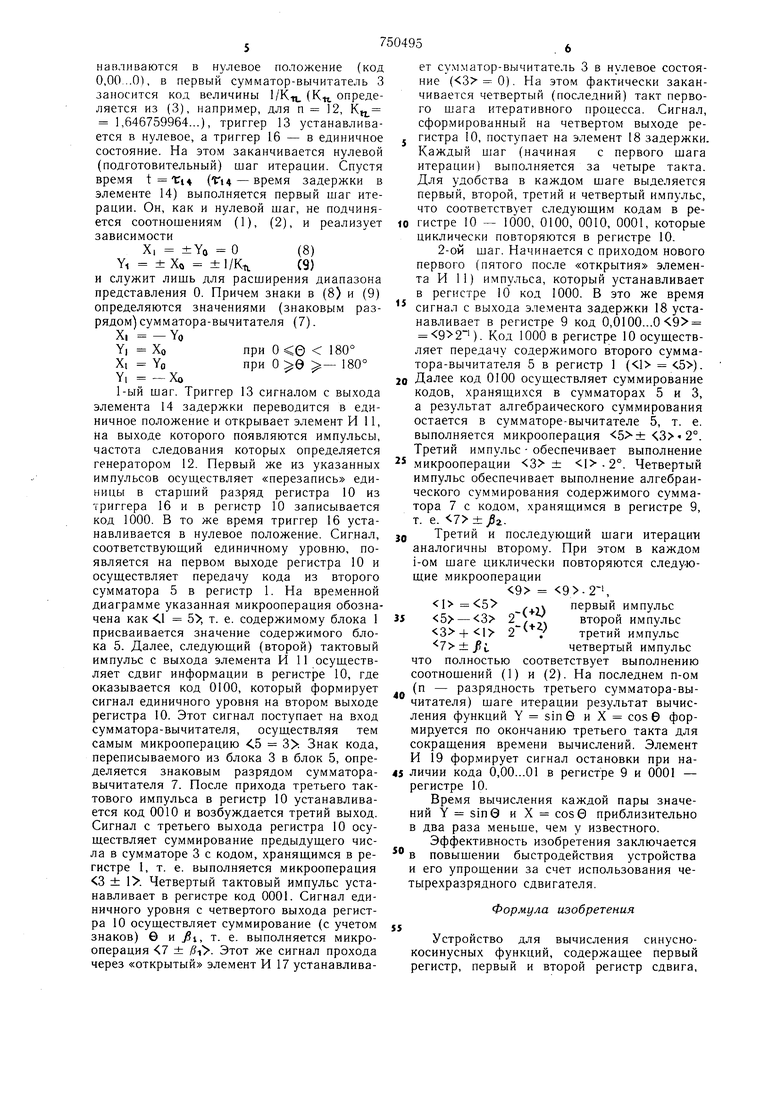

Цоставленная цель достигается тем, что в устройство для вычисления синусно-косинусных функций, содержащее первый регистр, первый и второй регистр сдвига, первый, второй и третий сумматоры-вычитатели, введены первый и второй сдвигатели, блок элементов И, блок элементов ИЛИ, первый второй и третий элементы И, первый, второй и третий элементы ИЛИ, первый и второй элементы задержки, первый и второй триггеры, генератор импульсов, причем управляющий вход устройства соединен с входом первого элемента задержки, с установочными входами первого регистра, первого и второго регистров сдвига, первого и второго сумматоров-вычитателей и с управляющим входом блока элементов И, выход первого элемента задержки подключен к единичному входу первого триггера, единичный выход которого соединен с первым входом первого 20 элемента И, второй вход которого соединен с выходом генератора импульсов, управляющий вход первого регистра соединен с первым выходом второго регистра сдвига, второй и третий выходы которого соединены

с управляющими входами соответственно первого и второго сумматоров-вычитателей, а четвертый выход - с первым входом первого элемента ИЛИ, первым входом второго элемента И, управляюш.им входом третьего сумматора-вычитателя, второй вход первого элемента ИЛИ соединен с единичным выходом второго триггера, единичный вход которого соединен с управляющим входом устройства, а нулевой вход - с выходом первого элемента И, выходы вторых элементов И и ИЛИ соединены соответственно с входом установки нуля первого сумматоравычитателя и третьими входами первого и второго сдвигателей, информационные входы первого и второго сумматоров-вычитателей соединены с выходами соответственно первого и второго сдвигателей, а выходы - с информационными входами соответственно второго сдвигателя и первого регистра, вход второго элемента задержки соединен с первым входом второго элемента И, а выход - с сдвигающим входом первого регистра сдвига, первый выход которого подключен к вторым входам второго элемента И и второго элемента ИЛИ и первому входу третьего сумматора-вычитателя, второй вход которого соединен с первым входом второго элемента ИЛИ и вторым выходом первого регистра сдвига, третий выход которого подключен к вторым входам первого и второго сдвигателей и третьему входу третьего сумматора-вычитателя, выход младщих разрядов первого регистра сдвига соединен с входом блока элементов ИЛИ, выход которого соединен с входом младщих разрядов третьего сумматоравычитателя, информационные входы которого соединены с выходами блока элементов И, входы которого являются информационными входами устройства, нулевой выход знакового разряда третьего сумматора-вычитателя соединен с суммирующим и вычитающим входами соответственно первого и второго сумматоров-вычитателей и суммирующему входу третьего сумматора-вычитателя, единичный выход знакового разряда которого соединен с вычитающим и суммирующим входом соответственно первого и второго сумматоров-вычитателей и вычитающим входом третьего сумматора-вычитателя, выход младшего разряда первого регистра сдвига соединен с первыми входами первого и второго сдвигателей и с вторым входом третьего элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с нулевым входом первого триггера, первый вход третьего элемента ИЛИ соединен с управляющим входом устройства, выход первого элемента И соединен с сдвигающим входом второго регистра сдвига, информационный вход которого соединен с выходом первого элемента ИЛИ, информационные выходы первого регистра соединены с входами второго сдвигателя.

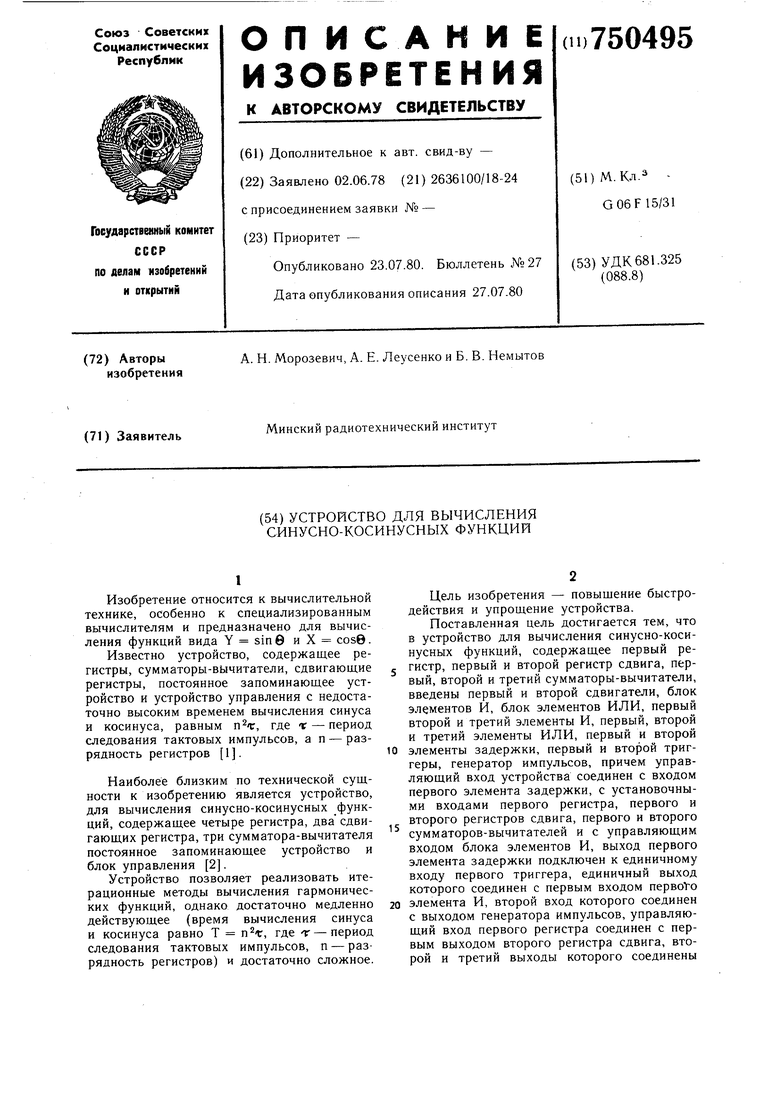

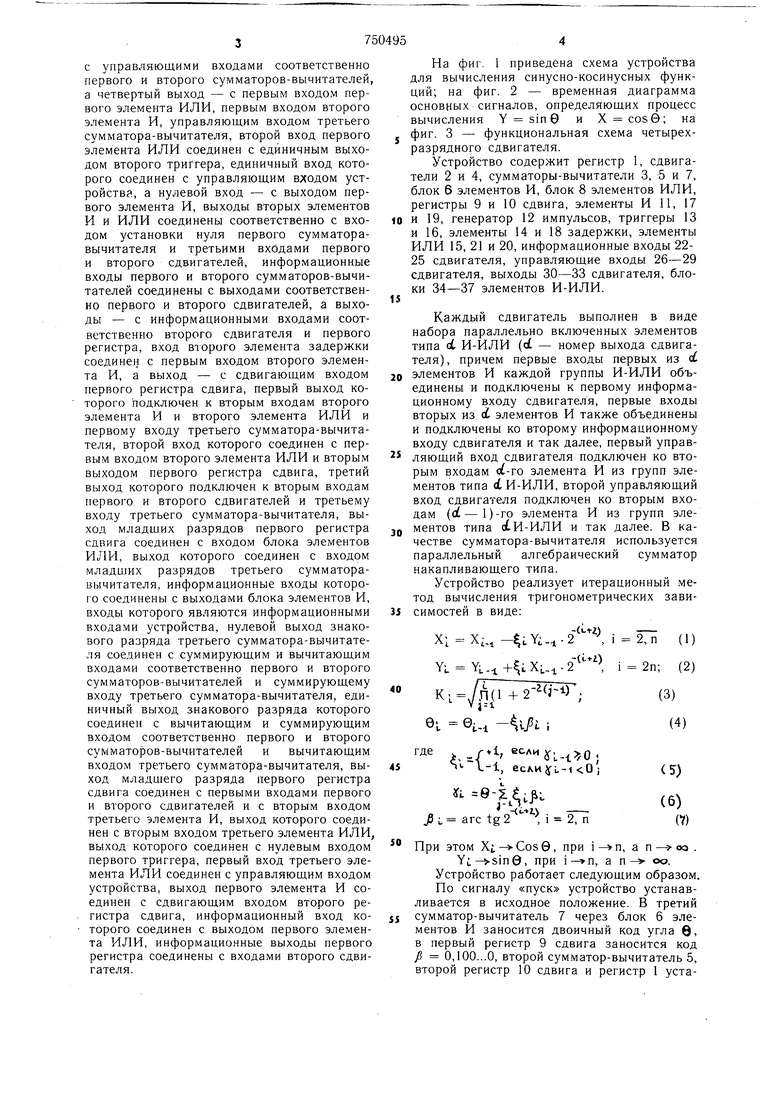

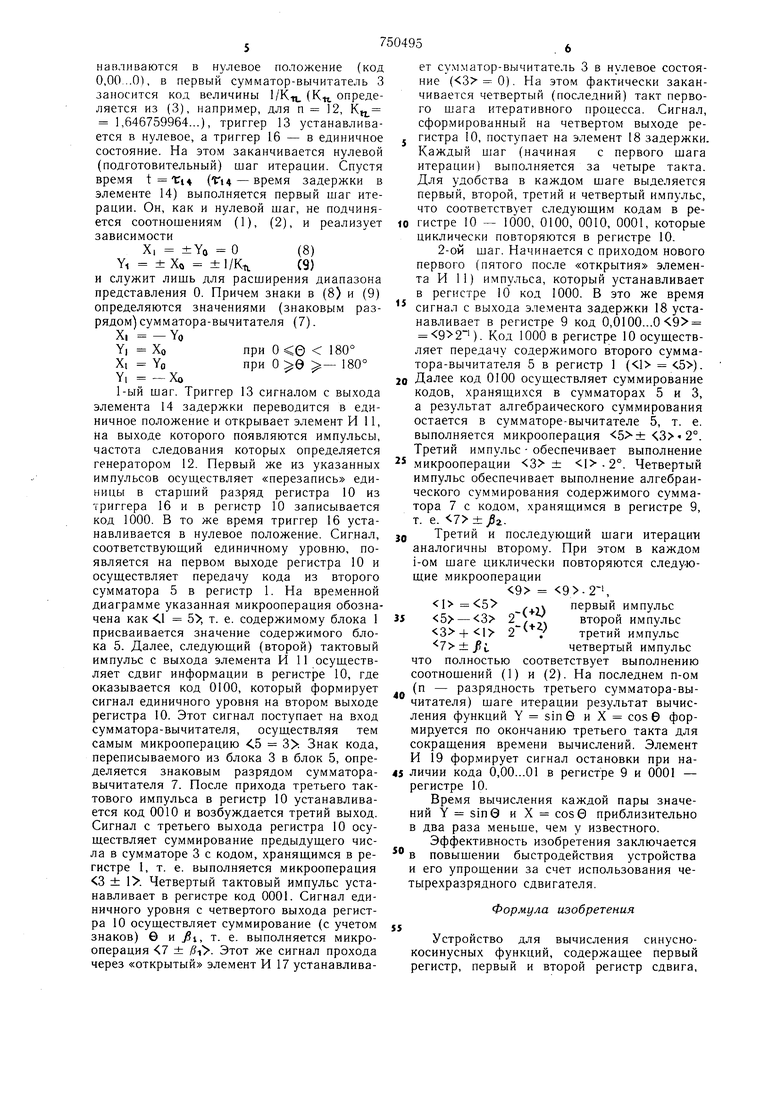

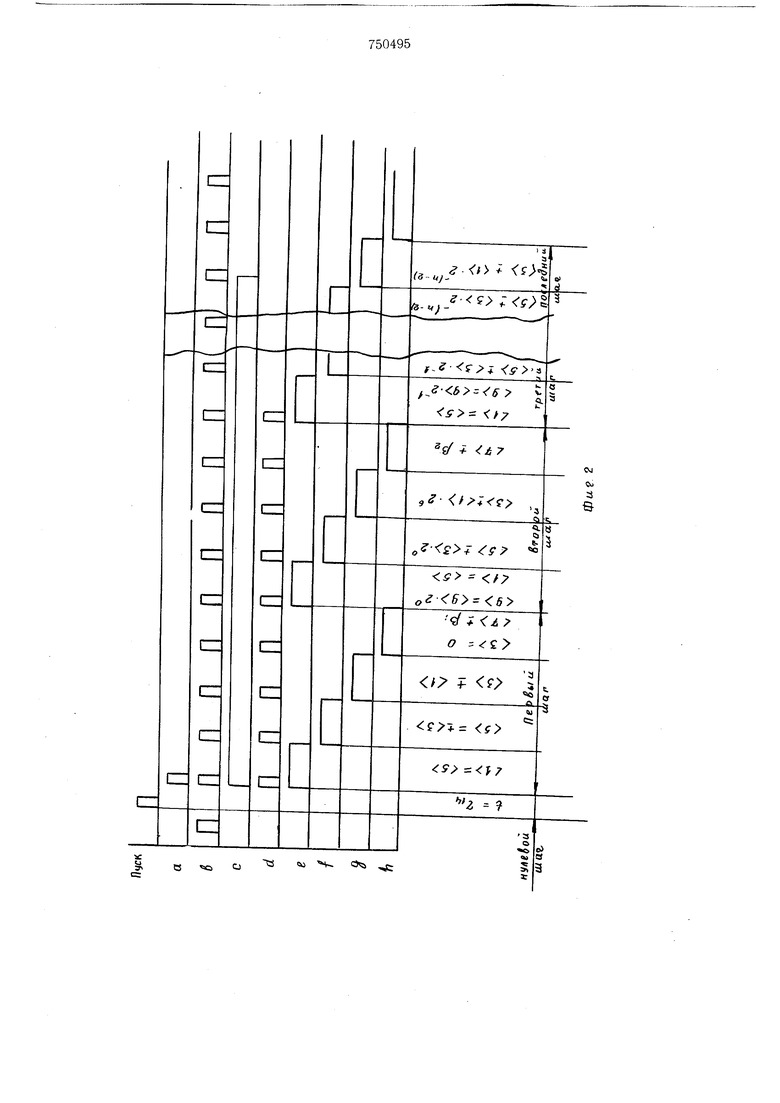

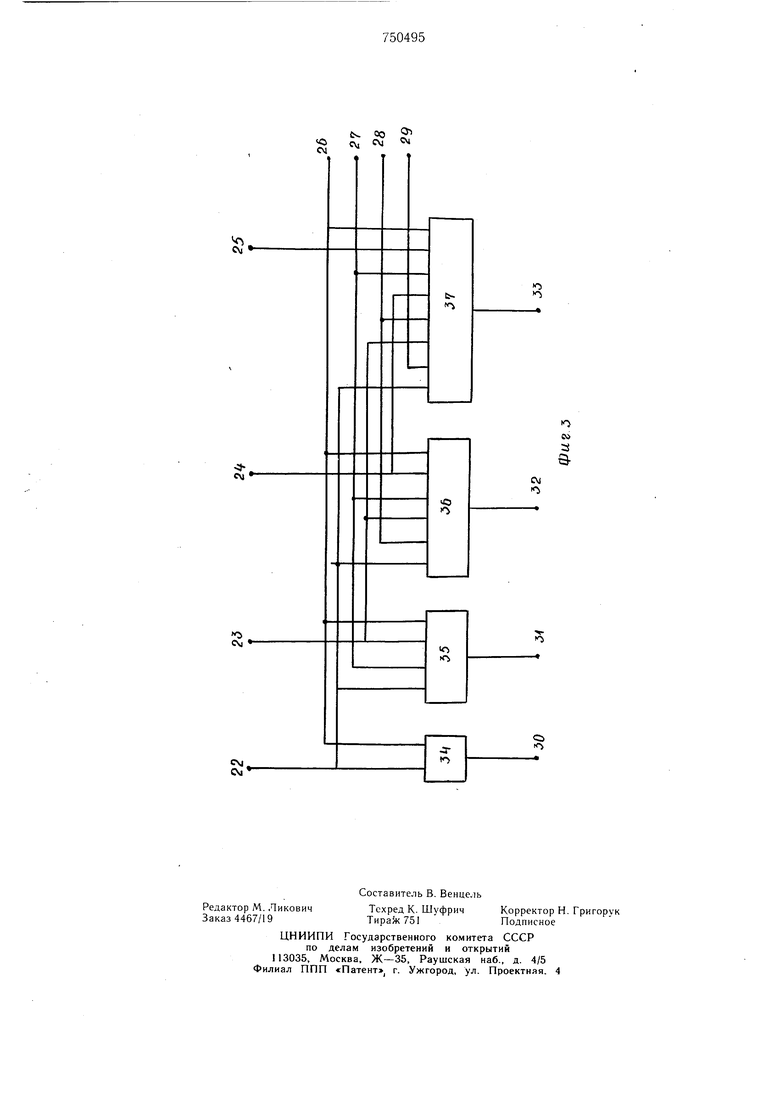

На фиг. 1 приведена схема устройства для вычисления синусно-косинусных функций; на фиг. 2 - временная диаграмма основных сигналов, определяющих процесс вычисления Y sinG и X cos0; на фиг. 3 - функциональная схема четырехразрядного сдвигателя.

Устройство содержит регистр 1, сдвигатели 2 и 4, сумматоры-вычитатели 3, 5 и 7, блок 6 элементов И, блок 8 эле.ментов ИЛИ, регистры 9 и 10 сдвига, элементы И 11, 17 0 и 19, генератор 12 импульсов, триггеры 13 и 16, элементы 14 и 18 задержки, элементы ИЛИ 15, 21 и 20, информационные входы 2225 сдвигателя, управляющие входы 26-29 сдвигателя, выходы 30-33 сдвигателя, блоки 34-37 элементов И-ИЛИ.

Каждый сдвигатель выполнен в виде набора параллельно включенных элементов типа d И-ИЛИ (с - номер выхода сдвигателя) , причем первые входы первых из ot Q элементов И каждой группы И-ИЛИ объединены и подключены к первому информационному входу сдвигателя, первые входы вторых из fit элементов И также объединены и подключены ко второму информационному входу сдвигателя и так далее, первый управляющии вход сдвигателя подключен ко вторым входам сС-го элемента И из групп элементов типа И-ИЛИ, второй управляющий вход сдвигателя подключен ко вторым входам (d - 1)-го элемента И из групп элеQ ментов типа оСИ-ИЛИ и так далее. В качестве сумматора-вычитателя используется параллельный алгебраический сумматор накапливающего типа.

Устройство реализует итерационный метод вычисления тригонометрических зависимостей в виде:

XI Х, Y:- . 2, i 2

1)

,) i 2n; (2)

YL - +v XL-I 2

К,У|5иТ НГ;

(3) (4)

01 01-1 I

.U; eoAHjf,.o

где

l-l, ec M{fL-i Q;

()

.1

(6)

J3 L arc tg , i 2, n

(7)

При этом Xi Cos G, при i - n, a n - oa . .sin0, при , a n - oo.

Устройство работает следующим образом.

По сигналу «пуск устройство устанавливается в исходное положение. В третий сумматор-вычитатель 7 через блок 6 элементов И заносится двоичный код угла Q, в первый регистр 9 сдвига заносится код / 0,100...О, второй сумматор-Бычитатель 5, второй регистр 10 сдвига и регистр 1 устанавливаются в нулевое положение (код 0,00...0), в первый сумматор-вычитатель 3 заносится код величины 1/К-п. (Ktt определяется из (3), например, для п 12, K,i 1,646759964...), триггер 13 устанавливается в нулевое, а триггер 16 - в единичное состояние. На этом заканчивается нулевой (подготовительный) шаг итерации. Спустя время (ft 4 - время задержки в элементе 14) выполняется первый шаг итерации. Он, как и нулевой шаг, не подчиняется соотношениям (1), (2), и реализует зависимости X, ±YO О(8) Y, ±Хо ±I/KU(9) и служит лишь для расширения диапазона представления 0. Причем знаки в (8) и (9) определяются значениями (знаковым разрядом)сумматора-вычитателя (7). Х| - YO YI Хопри О © 180° Xi УОпри - 180° Y, -Хо 1-ый шаг. Триггер 13 сигналом с выхода элемента 14 задержки переводится в единичное положение и открывает элемент И 11, на выходе которого появляются импульсы, частота следования которых определяется генератором 12. Первый же из указанных импульсов осуществляет «перезапись единицы в старший разряд регистра 10 из триггера 16 и в регистр 10 записывается код 1000. В то же время триггер 16 устанавливается в нулевое положение. Сигнал, соответствующий единичному уровню, появляется на первом выходе регистра 10 и осуществляет передачу кода из второго сумматора 5 в регистр 1. На вре.менной диаграмме указанная микрооперация обозначена как 1 5, т. е. содержимому блока 1 присваивается значение содержимого блока 5. Далее, следующий (второй) тактовый импульс с выхода элемента И 11 осуществляет сдвиг информации в регистре 10, где оказывается код 0100, который формирует сигнал единичного уровня на втором выходе регистра 10. Этот сигнал поступает на вход сумматора-вычитателя, осуществляя тем самым микрооперацию 5 3 Знак кода, переписываемого из блока 3 в блок 5, определяется знаковым разрядом сумматоравычитателя 7. После прихода третьего тактового импульса в регистр 10 устанавливается код 0010 и возбуждается третий выход. Сигнал с третьего выхода регистра 10 осуществляет суммирование предыдущего числа в сумматоре 3 с кодом, хранящимся в регистре 1, т. е. выполняется микрооперация 3 ± 1. Четвертый тактовый импульс устанавливает в регистре код 0001. Сигнал единичного уровня с четвертого выхода регистра 10 осуществляет суммирование (с учетом знаков) 0 и 1, т. е. выполняется микрооперация 7 ± . Этот же сигнал прохода через «открытый элемент И 17 устанавливает сумматор-вычитатель 3 в нулевое состояние (3 0). На этом фактически заканчивается четвертый (последний) такт первого шага итеративного процесса. Сигнал, сформированный на четвертом выходе регистра 10, поступает на элемент 18 задержки. Каждый шаг (начиная с первого шага итерации) выполняется за четыре такта. Для удобства в каждом шаге выделяется первый, второй, третий и четвертый импульс, что соответствует следующим кодам в рвгистре 10 - 1000, 0100, 0010, 0001, которые циклически повторяются в регистре 10. 2-ой шаг. Начинается с приходом нового первого (пятого после «открытия элемента И 11) импульса, который устанавливает в регистре 10 код 1000. В это же время сигнал с выхода элемента задержки 18 устанавливает в регистре 9 код 0,0100...0 9 ). Код 1000 в регистре 10 осуществляет передачу содержимого второго сумматора-вычитателя 5 в регистр 1 (1 5). Далее код 0100 осуществляет суммирование кодов, хранящихся в сумматорах 5 и 3, а результат алгебраического суммирования остается в сумматоре-вычитателе 5, т. е. выполняется микрооперация . Третий импульс - обеспечивает выполнение микрооперации 3 ± . Четвертый импульс обеспечивает выполнение алгебраического суммирования содержимого сумматора 7 с кодом, хранящимся в регистре 9, т. е. .. Третий и последующий шаги итерации аналогичны второму. При этом в каждом i-OM шаге циклически повторяются следу-ющие микрооперации 9 , 1 5 ,. ,1 первый импульс т второй импульс 1 2 / третий импульс 7 ±fiчетвертый импульс что полностью соответствует выполнению соотношений (1) и (2). На последнем п-ом (п - разрядность третьего сумматора-вычитателя) шаге итерации результат вычисления функций У sin 6 и X cos 6 формируется по окончанию третьего такта для сокращения времени вычислений. Элемент И 19 формирует сигнал остановки при наичии кода 0,00...01 в регистре 9 и 0001 - регистре 10. Время вычисления каждой пары значений У sin0 и X cos 6 приблизительно в два раза меньше, чем у известного. Эффективность изобретения заключается повышении быстродействия устройства и его упрощении за счет использования чеырехразрядного сдвигателя. Формула изобретения Устройство для вычисления синуснокосинусных функций, содержащее первый регистр, первый и второй регистр сдвига.

первый, второй и третий сумматоры-вычитатели, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, в него введены первый и второй сдвигатели, блок элементов И, блок элементов ИЛИ, первый, второй и третий элементы И, первый, второй и третий элементы ИЛИ, первый и второй элементы задержки, первый и второй триггеры, генератор импульсов, причем управляющий вход устройства соединен с входом первого элемента задержки, с установочными входами первого регистра, первого и второго регистров сдвига, первого и второго сумматоров-вычитателей и с управляющим входом блока элементов И, выход первого элемента задержки подключен к единичному входу первого триггера, единичный выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом генератора импульсов, управляющий вход первого регистра соединен с первым выходом второго регистра сдвига, второй и третий выходы которого соединены с управляющими входами соответственно первого и второго сумматоров-вычитателей, а четвертый выход - с первым входом первого элемента ИЛИ, первым входом второго элемента И, управляюн1,им входом третьего сумматора-вычитателя, второй вход первого элемента ИЛИ соединен с единичным выходом второго триггера, единичный вход которого соединен с управляющим входом устройства, а нулевой вход - с выходом первого элемента И, выходы вторых элементов И и ИЛИ соединены соответственно с входом установки нуля первого сумматора-вычитателя и третьими входами первого и второго сдвигателей, информационные входы первого и второго сумматоров-вычитателей соединены с выходами соответственно первого и второго сдвигателей, а выходы - с информационными входами соответственно второго сдвигателя и .первого регистра, вход второго элемента задержки соединен с первым входом второго элемента И, а выход - с сдвигающим входом первого регистра сдвига, первый выход которого подключен ко вторым вхбдам второго э.1емепта И и второго элемента ИЛИ

и первому входу третьего сумматора-вычитателя, второй вход которого соединен с первым входом второго элемента ИЛИ и вторым выходом первого регистра сдвига, третий выход которого подключен ко вторым

входам первого и второго сдвигателей и третьему входу третьего сумматора-вычитателя, выход младщих разрядов первого регистра сдвига соединен со вторыми входами первого и второго сдвигателей и с входом блока элементов ИЛИ, выход которого соединен с входом младщих разрядов третьего сумматора-вычитателя, информационные входы которого соединены с выходами блока элементов И, входы которого являются информационными входами устройства, нулеВОЙ выход знакового разряда третьего сумматора-вычитателя соединен с суммирующим и вычитающим входами соответственно первого и второго сумматоров-вычитателей и суммирующему входу третьего сумматоравычитателя, единичный выход знакового

разряда которого соединен с вычитающим и суммирующим входом соответственно первого и второго сумматоров-вычитателей и вычитающим входом третьего сумматоравычитателя, выход младщего разряда первого регистра сдвига соединен с первыми

входами первого и второго сдвигателей и с вторым входом третьего элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с нулевым входом первого триггера, первый вход третьего элемента ИЛИ соединен с управляющим входом устройства, выход первого элемента И соединен с сдвигающим входом второго регистра сдвига, информационный вход которого соединен с выходом первого элемента ИЛИ, информационные

выходы первого регистра соединены с входами второго сдвигателя.

Источники информации, п-ринятые во внимание при экспертизе

1.Байков В. Д., Смолов В. Б. Аппаратурная реализация элементарных функций

в ЦВМ, Л., 1976.

2.Оранский А. М. Аппаратные методы в цифровой вь числите,1ьпой технике, .инск, 1977, с. 102, 131 - 132.

3

&

«о

Ol

ел

С 00

Cv Oj CM

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой гармонический анализатор | 1979 |

|

SU873148A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Цифровое устройство для вычисления синусно-косинусных функций | 1980 |

|

SU868753A1 |

| Вычислительное устройство | 1983 |

|

SU1167605A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для вычисления элементарных функций по алгоритму Волдера | 1982 |

|

SU1068933A1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

о

b

1

10

K

3

aCVJ

-o

O C4j

CVJ.

о f

Авторы

Даты

1980-07-23—Публикация

1978-06-02—Подача