1

Изобретение относится к вычислительной технике и может быть использовано в устройствах аналоговой вычислительной техники, а также в устройствах передачи данных в качестве балансного модулятора и в схеме, осуществляющей автоматическую регулировку усиления.

Известны умножители аналоговых сигналов, осуществляющие предв1аритель- ное логарифмирование, суммирование, а затем антилогарифмирование |1| .

Такие умножители имеют ограниченный снизу динамический диапазон.

Известны также устройства умножения, использующие передаточную проводимость биполярных транзисторов 2. .

Основным недостатком таких перемножителей является низкий динамический диапазон, который ограничивается мак- . симальным входным сигналом.

Наиболее близким к предлагаемому является умножитель аналоговых сигналов, содержащий выходной дифференциальный усилитель и множительный

мост, в каждое плечо которого включен элемент с управляемым коэффициентом передачи, выполненный на МДП-транзисторе, при этом стоки первого и второго МДП- ранзиоторов, включенных в первое и второе плечи моста, подключены к первому входу умножителя, исток первого МДП-транзистора подключен к стоку третьего МДП-транзистора, включенного в третье плечо моста, и к инвертирую10щему входу выходного дифференциального усилителя, а исток второго МДП-транзистора подключен к стоку четвертого МДП-транзистора, включенного в четвертое плечо моста, и к неинвертирующему

15 входу выходного дифференциального усилителя, выход которого является выходом умножителя, истоки третьего и четвер- того транзисторов подключены к шине нулевого потенциала ,3J.

20

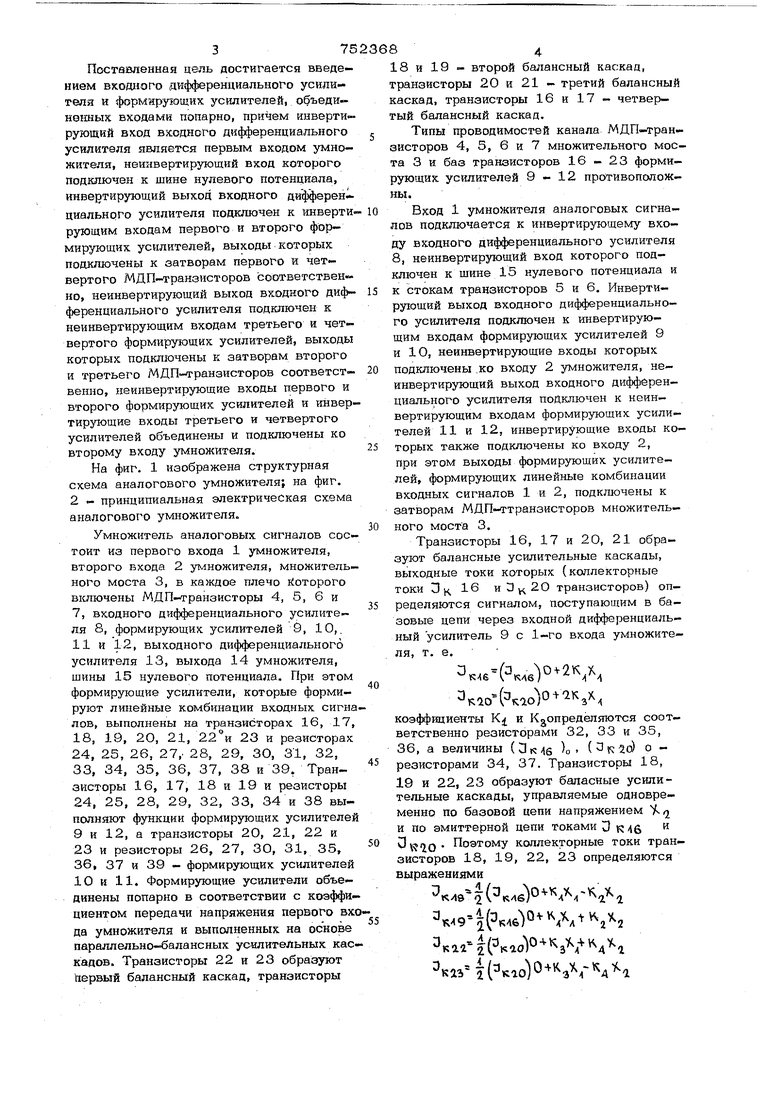

Цель изобретения - повышение тон- йости и расширение динамического диапазона. Поставленная цель достигается введением входного дифференциального усилителя и формирующих усилителей, о ъеди- венных входами попарно, причем инвертирующий вход входного дифференциального усилителя является первым входом умножителя, неинвертирующий вход которого подключен к шине нулевого потенциала, инвертирующий выход входного дифференциального усилителя подключен к инверти рующим входам первого и второго формирующих усилителей, выходы которых подключены к затворам первого и четвертого МДП-транзисторов соответствен- но, неинвертирующий выход входного дифференциального усилителя подключен к неинвертирующим входам третьего и четвертого формирующих усилителей, выходы которых подключены к затворам второго и третьего МДП-транзисторов соответственно, неинвертирующие входы первого и второго формирующих усилителей и инвертирующие входы третьего и четвертого усилителей объединены и подключены ко второму входу умножителя. На фиг. 1 изображена структурная схема аналогового умножителя; на фиг. 2 - принципиальная электрическая схема аналогового умножителя. Умножитель аналоговых сигналов состоит из первого входа 1 умножителя, второго входа 2 умножителя, множительного моста 3, в каждое плечо Которого включены МДП- ранзисторы 4, 5, 6 и 7, входного дифференциального усилителя 8, формирующих усилителей S, 10,. 11 и 12, выходного дифференциального усилителя 13, выхода 14 умножителя, шины 15 нулевого потенциала. При этом формирующие усилители, которые формируют линейные комбинации входных сигна лов, выполнены на транзисторах 16, 17, 18, 19, 20, 21, 22 23 и резисторах 24, 25, 26, 27,. 28, 29, ЗО, 31, 32, 33, 34, 35, 36, 37, 38 и 39, Транзисторы 16, 17, 18 и 19 и резисторы 24, 25, 28, 29, 32, 33, 34 и 38 выполняют функции формирующих усилителей 9и 12, а транзисторы 20, 21, 22 и 23 и резисторы 26, 27, ЗО, 31, 35, 36, 37 и 39 - формирующих усилителей 10и 11. Формирующие усилители объединены попарно в соответствии с коэффициентом передачи напряжения первого вхо да умножителя и выполненных на основе параллельно-балансных усилительных каскадов. Транзисторы 22 и 23 образуют первый балансный каскад, транзисторы 18 и 19 - второй балансный каскад, транзисторы 20 и 21 - третий балансный каскад, транзисторы 16 и 17 - четвертый балансный каскад. Типы проводимостей канала МДП-транзисторов 4, 5, 6 и 7 множительного моста 3 и баз транзисторов 16 - 23 формирующих усилителей 9-12 противоположны. Вход 1 умножителя аналоговых сигналов подключается к инвертирующему входу входного дифференциального усилителя 8, неинвертирующий вход которого подключен к шине 15 нулевого потенциала и к стокам транзисторов 5 и 6. Инвертирующий выход входного дифференциального усилителя подключен к инвертирующим входам формирующих усилителей 9 и 10, неинвертирующие входы которых подключены ,ко входу 2 умножителя, неинвертирующий выход входного дифференциального усилителя подключен к неинвертирующим входам формирующих усилителей 11 и 12, инвертирующие входы которых также подключены ко входу 2, при этом выходы формирующих усилителей, формирующих линейные комбинации входных сигналов 1 и 2, подключены к затворам МДП-ттранзисторов множительного моста 3. Транзисторы 16, 17 и 20, 21 образуют балансные усилительные каскады, выходные токи которых (коллекторные токи 3 f, 16 транзисторов) определяются сигналом, поступающим в базовые цепи через входной дифференциальный усилитель 9 с 1-го входа умножителя, т. е. к.)) ) коэффвдиенты K и К определяются соответственно резисторами 32, 33 и 35, 36, а величины ( 3 к g о . ( К 2а о резисторами 34, 37, Транзисторы 18, 19 и 22, 23 образуют баласные усилительные каскады, управляемые одновременно по базовой цепи напряжением и по эмиттерной цепи токами D к 46 1О Поэтому коллекторные токи транзисторов 18, 19, 22, 23 определяются выражениями ()0,-V4,,X, чД9-|{Эмб) Kai-fl i-wlO- aVN a ) 57 Коэффициенты К „и К «определяются соответственно резисторами 28, 29 и 30, 31. С учетом этого напряжения на резис«торных нагрузках 24, 25, 26, 27 формируются в соответствии с предлагаемыми линейными комбинациягми сигналов и имеют вид 4К1Л1 К2,Х2 для транзистора 5КЗ,Х1+ К4.02 для транзистора 6КЗ.Х1- К4,Х2 для транзистора 7Kl.Xl-i- К2.Х2 для транзистора Напряжение на выходе 14 умножителя равно К5,Х1.Х2. Таким образом, в предлагаемом устр стве напряжения на затворах МДП-транзисторов 4-7 множительного моста 3 формируются Как результат линейных преобразований входных сигналов в усилительных трактах, что позволяет расши рить динамический диапазон и снизить погрешность перемножения. Поэтому пре лагаемый перемножитеаь имеет статичес кую погрешность почти на порядок лучш известных, а динамический- диапазон сос тавляет порядка 1ООО, что почти в 10О раз больше, чем у перемножителей, использующих передаточную характеристику биполярных транзисторов и во столько же раз лучше, чем у известных аналоговых перемножителей на МДП-транзисторах. Такие высокие электрические характеристики предлагаемого устройства позволяют использовать его в качест ве балансного модулятора или схемы АРУ. Поэтому предлагаемое устройство многофункционально, что экономически выгодно в случае микроэлектронного его использования. Формула изобретения Умножитель аналоговых сигналов, содержащий выходной дифференциальный усилитель и множительный мост, в каждое плечо которого включен элемент с управляемым коэффициентом передачи, выполненный на МДП-транзисторе, при этом стоки первого и второго МДП-тран зисторов, включенных в первое и второе 8 плечи моста, подключены к первому входу умножителя, исток первого МДП-гран зйстора подключен к стоку третьего МДП-транзистора. включенного в третье плечо моста, и к гшвертирующему входу выходного Дифференциального усилителя, а Исток второго МДП- гранзистора подключен к стоку четвертого МДП-транзистора, включенного в четвертое плечо моста, и к неинвертирующему входу выходного дифференциального усилителя, выход которого является выходом умножителя, истоки третьего и четвертого транзисторов подключены к шине нулевого потенциала, отличающийся тем, что, с целью повышения точности и расширения, динамического диапазона, он дополнительно содержит входной дифференциальный усилитель и формирующие усилите ли, объединенные входами попарно, причем инвертирующий вход входного дифференциального усилителя является первым входом умножителя, неинвертирующий вход которого подключен к шине нулевого потенциала, инвертирующий выход входного дифференциального усилителя подключен к инвертирующим входам первого к второго формирующих усилителей, выходы которых подключены к затворам первого и четвертого ЛШП-транзисторов соответственно, неинвертирующий выход входного дифференциального усилителя подключен к неинвертирующим входам третьего и четвертого формирующих усилителей, выходы которых подключены к затворам второго и третьего МДП-тран- зисторов соответственно, неинвертирую- щие входы первого и второго формирующих усилителей и инвертирующие входы третьего и четвэртого усилителей объединены к подключены ко второму входу умножителя. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 586465, кл. Q 06 Q 7/16, 1977. 2.Авторское свидетельство СССР № 602955, кл. Q 06 CS 7/16, 1978. 3.Патент США Мз 3368О66, кл. 235-194, опублик. 1968 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля сопротивления резистивного элемента | 1988 |

|

SU1707789A1 |

| Множительное устройство | 1980 |

|

SU924720A1 |

| Аналоговое делительное устройство | 1980 |

|

SU957224A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| Компаратор | 1989 |

|

SU1690184A1 |

| Аналоговое множительное устройство | 1987 |

|

SU1497625A1 |

| Усилительное устройство | 1988 |

|

SU1571749A1 |

| Аналоговое множительное устройство | 1979 |

|

SU932506A1 |

| Многоканальный коммутатор | 1985 |

|

SU1246362A1 |

| Операционный усилитель | 1983 |

|

SU1118262A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-28—Подача