1

Изобретение относится к вычислительной технике и может быть использовано в радиотехнических устройствах различного назначения, в частности в детекторах, и как самостоятельная интегральная микросхема (ИМС).

Известны умножители на биполярных транзисторах, широко используемые как самостоятельные микросхемы и как узлы различных микросхем.

Получили распространение умножители на МДП-транзисторах, имеющие ряд характеристик лучше, чем умножители на биполярных транзисторах. Эти устройства используются и как самостоятельные узлы l .

Недостатком их является низкая точность умножения.

Наиболее близким к предлагаемому по технической сущности является множительное устройство, содержащее четыре одинаковых умножающих МДП-транзистора и два нагрузочных МДП-транзистора, затворы умножающих МДП-транзисторов являются первым входом устройства, попарно объединенные истоки умножающих МДП-транзисторов подключены к стокам опорных МДП-транзисторов, затворы которых являются вторым входом устройства, стоки умножающих транзисторов подключены к истокам соответствующих нагрузочных МДП-транзисторов и является выходом устройства, затворы и стоки нагрузочных МДПtoтранзисторов объединены и подключены к первой шине питания, истоки опорных МДП-транзисторов объединены и подключены к выходу стабилизатора тока, образованного двумя усилительными и

15 двумя нагрузочными МДП-транзисторами. Входы стабилизатора тока подключены к соответствующим шинам питания J/2. Недостатком этого устройства является низкая точность умножения,

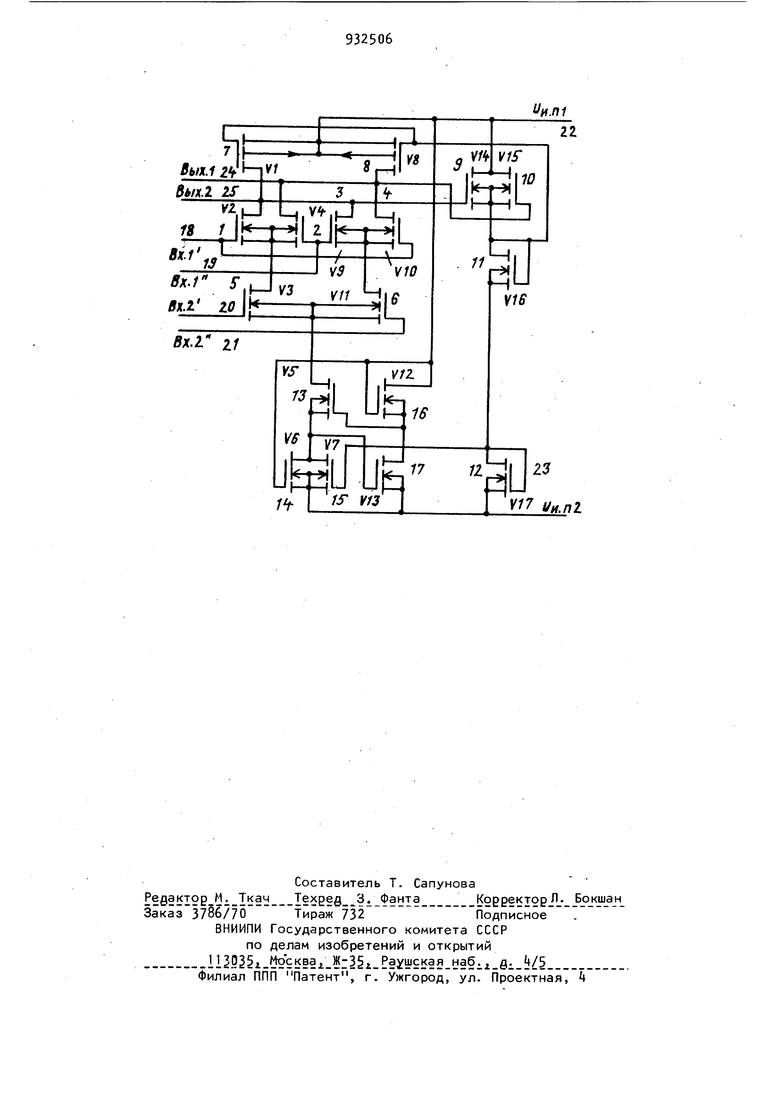

20 обусловленная недостаточно хорошей линейностью характеристики и невысоким подавлением синфазных помех, а также небольшой диапазон изменения сигналов, обусловленный недостаточны коэффициентом умножения. Цель изобретения - повышение точности и расширение диапазона изменения входных сигналов. Поставленная цель достигается тем что в аналоговое множительное устрой ство, содержащеее четыре умножающих МДП-транзистора одного типа проводимости, два опорных МДП-транзистора того же типа проводимости и два нагр зочных МДП-транзистора, истоки первого и второго умножающих МДП-транзи торов объединены и подключены к стоку первого опорного МДП-транзистора, истоки третьего и четвертого умножаю щих МДП-транзисторов объединены и подключены к стоку второго опорного МДП-транзистора, затворы первого и четвертого умножающих МДП-транзисторов объединены и подключены к первой входной шине устройства, затворы вто рого и третьего умножающихМДП-транaVicTopOB объединены и подключены ко второй входной шине устройства, первая и вторая входные шины являются первым входом устройства, затворы первого и второго опорных МДП-транзисторов являются вторым входом устройства, стоки первого и третьего умножающих МДП-транзисторов объедине ны и подключены к первой выходной ши не устройства и к стоку первого нагрузочного МДП-транзистора, стоки второго и четвертого умножающих МДПтранзисторов объединены и подключены к второй выходной шине устройства и к стоку второго нагрузочного транзис тора, первая и вторая выходные шины являются выходом устройства, затворы первого и второго нагрузочных МДП-транзисторов объединены, стоки первого и второго нагрузочных МДПтранзисторов объединены и подключены к первой шине питания, два усилитель ных МДП- транзистора, третий и четвертый нагрузочные МДП-транзисторы, затворы третьего и четвертого нагрузочных МДП-транзисторов и сток третьего нагрузочного МДП-транзистора объединены и подключены к первой шине питания, исток третьего нагрузочного МДП-транзистора, сток первого усилительного МДП-транзистора и затвор второго усилительного МДП-транзистора объединены, исток второго усилительного МДП-транзистора, сток четвертого нагрузочного МДП-транзист ра и затвор первого усилительного МДП-транзистора объединены, истоки первого усилительного и четвертого нагрузочных МДП-транзисторов объединены и подключены ко второй шине питания, сток второго усилительного МДП-транзистора и истоки первого и второго опорных МДП-транзисторов объединены, введены третий и четвертый усилительные МДП-транзисторы и пятый, шестой и седьмой нагрузочные МДП-транзисторы, первый и второй нагрузочные МДП-транзисторы имеют тип проводимости, противоположный типу проводимости умножающих МДПтранзисторов, стоки третьего и четветого усилительных МДП-транзисторов объединены и подключены к первой шине питания затворы соответственно подключены к стокам третьего и четвертого умножающих МДП-транзисторов, а исток подключен к объединенным стоку и затвору седьмого нагрузочного МДП-транзистора и к затворам первого и второго нагрузочных МДП-транзисторов, затвор пятого нагрузочного МДПтранзистора, сток и затвор шестого нагрузочного МДП-транзистора и исток седьмого нагрузочного МДП-транзистора объединены, сток и исток пятого нагрузочного МДП-транзистора подклют чены соответственно к стоку и истоку четвертого нагрузочного МДП-транзистора. На чертеже приведена принципиальная схема аналогового множительного устройства. Аналоговое множительное устройство содержит четыре умножающих МДПтранзистора I-, два опорных МДПтранзистора 5 и 6, нагрузочные МДПтранзисторы 7 и 8, усилительные МДПтранзисторы 9 и 10, нагрузочные МДПтранзисторы 11 и 12, МДП-транзисторы 9-12 образуют двухвходовый повторитель, усилительный МДП-транзистор 13, нагрузочные МДП-транзисторы Ij-lG, усилительный транзистор 17, МДП-транзисторы образуют токостабилизатор. На чертеже также обозначены первая 18 и вторая 19 входные шины, образующие первый вход устройства, третья 20 и четвертая 21 входные шины, образующие второй вход устройства, первая 22 и вторая 23 шины питания, первая и вторая 25 вь1ходные шины, образующие выход .устройства. Аналоговое множительное устройство работает следующим образом. Характеристика тока стока МДПтранзистора в режиме насыщения имеет вид (Ь{из,-изипорГ/2, () где S - удельная крутизна; Uji, - напряжение смещения затвор-исток; Uj( flop пороговое напряжение. Если на входы устройства подать два парафазных сигнала: на вх. 1 и, на вх. 1 -и и соответственно на вх. 2 U2 на вх. 2 -U2, то получим ток в каждом нагрузочном плече 1цо,г р AU J+BU +Си U2 +DU|+EU2 +F, С2 где коэффициенты А, В, С, D, Е, F функции от удельных крутизн МДП-тран зисторов 1,1,5,7,8,13,1 и 15 соответственно и напряжений смещений на их затворах , i 1,1,5,7,8,13, U,15. Полезным сигналом будет составляю щая С и и, где С - коэффициент умн жения; BUj( и EU - остаточные напряжения - нежелательные сигналы перем-. ножения; AU и Ш2 - нелинейные иска жения, также нежелательные составляю щие; F - постоянная составляющая тока. Составляющие BUvj и EU2 на выходе противофазны и подавление их можно осуществить только балансом схемы, который состоит в одинаковости удель ных крутизн МДП-транзисторов 1,2 и 1t,15 между собой т.е. PZ (14 их смещений на затворах - изи2 зин U3nt а также пороговых напряжений; баланс также требует (1 (9 зит Uw9 f Uawnop и цпорд Pia 5И1Э ЧИв SHtTOpO Uj nopeТаким образом, степень достижения ба ланса зависит от качества технологии возможность создания строго идентич ных структур) и тем самым определяет ся степень подавления остаточйых напряжений перемножителя. Составляющее Ли и Ш2 на выходе синфазны и зависят от свойств устройства подавлять синфазные помехи. Напряжение на выхо де устройства и коэффициент умножения определяется величиной сопротивлений в нагрузке плеч. Имеем UBWX нагр 2нагр и линейность умножителя определяется линейностью нагрузки. В прототипе имеем /2цагр 1(з)(1(з)(эГ вь ипорПз)У При тех же параметрах нагрузочных транзисторов, что и в прототипе (геометрических размерах, токе стока и потенциалах смещения на затворах) , величина (формула ky будет значительно больше, чем в прототипе, так как она будет определяться величиной дифференцильного выходного сопротивления нагрузочных транзисторов, а не их крутизной, известно, что поэтому коэффициент умножения будет больше. Поскольку величина значительно меньше зависит от , чем крутизна S, то предлагаемое устройство будет обладать большей линейностью. Однако такое включение нагрузочных МДП-транзисторов и следующие из этого включения преимущества можно реализовать при включении их затворов на выход двухвходового повторителя, затворы усилительных МДП-транзисторов которого подключены к разным выходным шинам устройства, а выход повторителя - к затвору одного из нагрузочных МДП-транзисторов токостабилизатора. Включение в устройство повторителя указанным способом уменьшает нестабильность и одновременно увеличивав ет подавление синфазных помех по сравнению с прототипом. Подавление синфазных помех (или что то же самое - стабилизация потенциалов) , возникших на выходных шинах вых. 1 и вых. 2 устройства, происходит под действием двух петель отрицательной обратной связи, первая через входы повторителя и затворы нагрузочных МДП-транзисторов, вторая - через входы повторителя и зат-. вор токостабилизатора 17). Эффекты . от действия этих петель суммируются и подавление синфазных помех больше, чем в прототипе, в котором петли обратной связи отсутствуют вовсе. I Преимуществом предлагаемого множительного устройства по сравнению с известным является использование в нагрузке умножающих транзисторов МДП-транзисторов с противоположным типом проводимости и повторителяТ так как улучшаются его основные характеристики: коэффициент умножения, линейность,.подавление синфазных помех, что приводит к значительно повышенной точности и расширяет динамический диапазон входных сигналов. 7 Формула изобретения Аналоговое множительное устройств содержащее четыре умножающих МДП-тра зистора одного типа проводимости, дв опорных МДП-т|Ьанзистора того же типа проводимости и два нагрузочных МД транзистора, истоки первого и второг умножающих МДП-транзисторов объеди немы и подключены к стоку первого опорного МДП-транзистора, истоки третьего и четвертого умножающих МДП-транзисторов объединены и подключены к стоку второго опорного МДП-транзисто ра, затворы первого и четвертого умножающих МДП-транзисторов объединены и подключены к первой входной шине устройства, затворы второго и третьего умножающих МДП-транзисторов объединены и подключены к второй входной шине устройства, первая и вт рая входные шины являются первым вхо дом устройства, затворы перового и второго опорных МДП-транзисторов являются вторым входом устройства, сто ки первого и третьего умножающих МДП-транзисторов объединены и подключены к первой выходной шине устройства и к стоку первого нагрузочно го МДП-транзистора, стоки второго и четвертого .умножающих МДП-транзисто ров объединены и подключены к второй выходной шине устройства и к стоку второго нагрузочного транзистора,первая и вторая выходные шины являются выходом устройства,затворы первого и вто рого нагрузочных МДП-транзисторов объединены, стоки первого и второго нагрузочных МДП-транзисторов объедин ны и подключены к первой шине питани два усилительных МДП-транзистора, третий и четвертый нагрузочные МДПтранзисторы, затворы третьего и четвертого нагрузочных МДП-транзисторов и сток третьего нагрузочного МДПтранзистора объединены и подключены к первой шине питания, исток третьего нагрузочного МДП-транзистора, сток первого усилительного МДП-тран968. зистора и затвор усилительного МДПтранзистора объединены, исток второго усилительного МДП-транзистора, сток четвертого нагрузочного МДПтранзистора и затвор первого усилительного МДП-транзистора объединен, истоки первого усилительного и четвертого нагрузочных МДП-транзисторов объединены и подключены к второй шине питания, сток второго усилительного МДП-транзистора и истоки первого и второго опорных МДП-транзисторов объединены, отличающеес я тем, что, с целью повышения точности и расширения динамического диапазона входных сигналов, в него введены третий и четвертый усилительные МДП-транзисторы и пятый, шестой и седьмой нагрузочные МДП-транзисторы, первый и второй нагрузочные МДПтранзисторы имеют тип проводимости, противоположный типу проводимости умножающих МДП-транзисторов, стоки третьего и четвертого усилительных МДП- транзисторов объединены и подключены к первой шине питания, затворы соответственно подключены к стокам третьего и.четвертого умножающих МДП-транзисторов, а исток подключен . к объединенным стоку и затвору седьмого нагрузочного МДП-транзистора и к затворам первого и второго нагрузочных МДП-транзисторов, затвор пятого нагрузочного МДП-транзистора, сток и затвор шестого нагрузочного МДПтранзистора и исток седьмого нагрузочного МДП-транзистора объединены, сток исток пятого нагрузочного МДП-транзистора подключены соответственно к стоку и истоку четвертого нагрузочного МДП-транзистора. Источники информации. Принятые во внимание при экспертизе 1.Гребен А. Б. Проектирование аналоговых интегральных схем. М., Мир, 1976. 2.Патент США № 39566 3, кл. 235-19, опублик. т 1.05-76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор импульсов,управляемый напряжением | 1980 |

|

SU902229A1 |

| Дешифратор адреса | 1981 |

|

SU966905A1 |

| Сумматор | 1983 |

|

SU1101863A1 |

| Формирователь импульсов | 1983 |

|

SU1166279A1 |

| Формирователь импульсов | 1980 |

|

SU919062A1 |

| Устройство согласования уровней напряжения /его варианты/ | 1983 |

|

SU1138940A1 |

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Умножитель аналоговых сигналов | 1978 |

|

SU752368A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| Дешифратор адреса | 1980 |

|

SU938408A1 |

Авторы

Даты

1982-05-30—Публикация

1979-12-10—Подача