Изобретение относится к вычислкгельной технике и может быть использовано при иаготовлении полупостоянных запоми нающих устройств, применяемых в систем автоматики, телемеханики и контроля функционирования радиоэлектро1шой аппаратуры. Известны полупостоянные запоминающие устройства, построенные на основе матричных схем. В качестве буферных устройств, связывающих их с внешним источником информации, служат либо регистр, либо матрица l и . В подобных запоминающих устройствах инфсрмация предварительно накапливается в регистре или матрице, а затем в нужный момент перезаписывается в основную матрицу. Недостатком упомянутых полупостоянных запоминающих устройств является ра деление во времени процесса записи и считывания и относительно большое врем перезаписи информации в основную матри цу. Кроме того, перед считыванием информации из накопителя требуется дополнительное время на проверку достоверности произведенной записи. При применении в качестве буферного устройства регистра, равного по объему памяти столбцу или строке матрицы, время, затрачиваемое на перезапись информации в матрице может увеличиваться из-за малого быстродействия внешнего источника информации. Если же в качестве буферного устройства применена матрица, то из-за присущих ей недостатков, например большое количество входов, сбой дешифратора адреса, схемная чувствительность матрицы к виду информации, запоминающее устройство в целом усложняется, а его надежность снижается. Цель изобретения - повышение надежности записи информации.. Поставленная цель достигается тем, что в полупостоянное запоминающее устройство, содержащее регистр адреса, дешифраторы адреса, входы которых подключены к соответствующим шинам управления, накопитель, входы элементов памяти KCTOpoio соединен-ы с соответствующими выходаш дешифратора, и усилитель считы1вания, входы которого подключены к сооветствуюшим выходам накопителя, ввёдёны стробируемые йлючи-формирователи, управляющие входы которых подключены к шине управления, а выходы соединены с соответствующими входами регистра адреса и элементов памяти накопителя с одинаковым адресом,

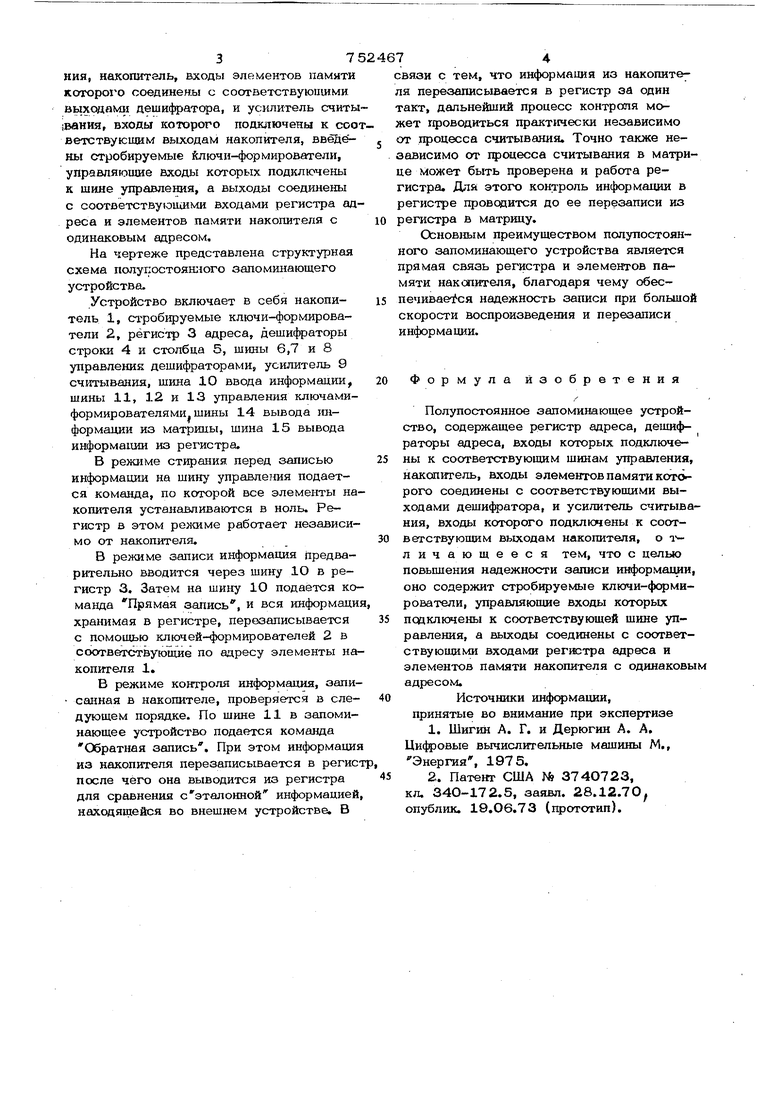

На чертеже представлена структурная схема полупостоянного запоминающего устройства.

Устройство включает в себя накопитель 1, стробируемые ключи-формирователи 2, регистр 3 адреса, дещифраторы строки 4 и столбца 5, шины 6,7 и 8 управлений дешифраторами, усилитель 9 считывания, шина 10 ввода информации, шины 11, 12 и 13 управления ключамиформирователями, шины 14 вывода 1шформации из матрицы, шина 15 вывода информа1ши из регистра,

В режиме стирания перед записью

информации на шину управле га я подается команда, по которой все элементы накопителя устанавливаются в ноль. Регистр в этом редшме работает независимо от накопителя,

В режиме записи информация предварительно вводится через шину 1О в регистр 3, Затем на шину 10 подается команда Прямая запись, и вся информаци хранимая в регистре, перезаписывается с помощью ключей-формирователей 2 в соответствующие по адресу элементы накопителя 1.

В режиме контроля информация, аапи санная в накопителе, проверяется в еледующем порядке. По шине 11 в запоминающее устройство подается команда Обратная запись. При этом информация из накопителя перезаписывается в регист после чего она выводится из регистра

для сравнения с эталонной информацией, находящейся во внешнем устройстве, В

связи с тем, что информация из накопителя перезаписывается в регистр за один такт, дальнейший процесс контроля может гфоводиться практически независимо от процесса считывания. Точно также независимо от ipotiecca считывания в матрице Может быть проверена и работа регистра. Для этого контроль информации в регистре проводится до ее перезаписи из регистра в матрицу.

Основным преимуществом полупостоянного запоминающего устройства является прямая связь регистра и элементов памяти накопителя, благодаря чему обеспечивается надежность записи при большо скорости воспроизведения и перезаписи информации.

Формула изобретения

X

Полупостоянное запоминающее устройство, содержащее регистр адреса, дешифраторы адреса, входы которых подключены к соответствующим шинам управления накопитель, входы элементов памяти которого соединены с соответствующими выходами дешифратора и усилитель счщ-ывания, входы которого подключены к соответствующим выходам накопителя, о т- личающееся тем, что с целью повьш1ения надежности записи информацл1И оно содержит стробируемые ключи-формирователи, управляющие входы которых подключены к соответствующей шине управления, а выходы соединены с соответствующими входами регистра адреса и элементов памяти накопителя с одинаковы адресом.

Источники информации, принятые во внимание при экспертизе

1,Шигин А, Г, и Дерюгин А, А, 1Ди(}5)овые вычислт-ельные машины М., Энергия, 1975.

2,Патент США N 374О723, кл. 34О-172.5, заявл, 28,12,7 О опублик, 19.О6.73 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупостоянное запоминающее устройство | 1976 |

|

SU690562A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| Многоканальное устройство для реверсирования двигателей постоянного тока | 1987 |

|

SU1573520A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287238A1 |

| Формирователь записи-считывания для запоминающих устройств | 1982 |

|

SU1035639A1 |

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Пульт учащегося для устройства обучения языкам | 1985 |

|

SU1354235A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-31—Подача