теля 7 поступает на регистр 3 адреса, где он запоминается и подается на вход дешифратора 5, в котором двоичный адрес преобразуется в униполярный код, управляющий работой формирователей 6 токов считывания - записи.

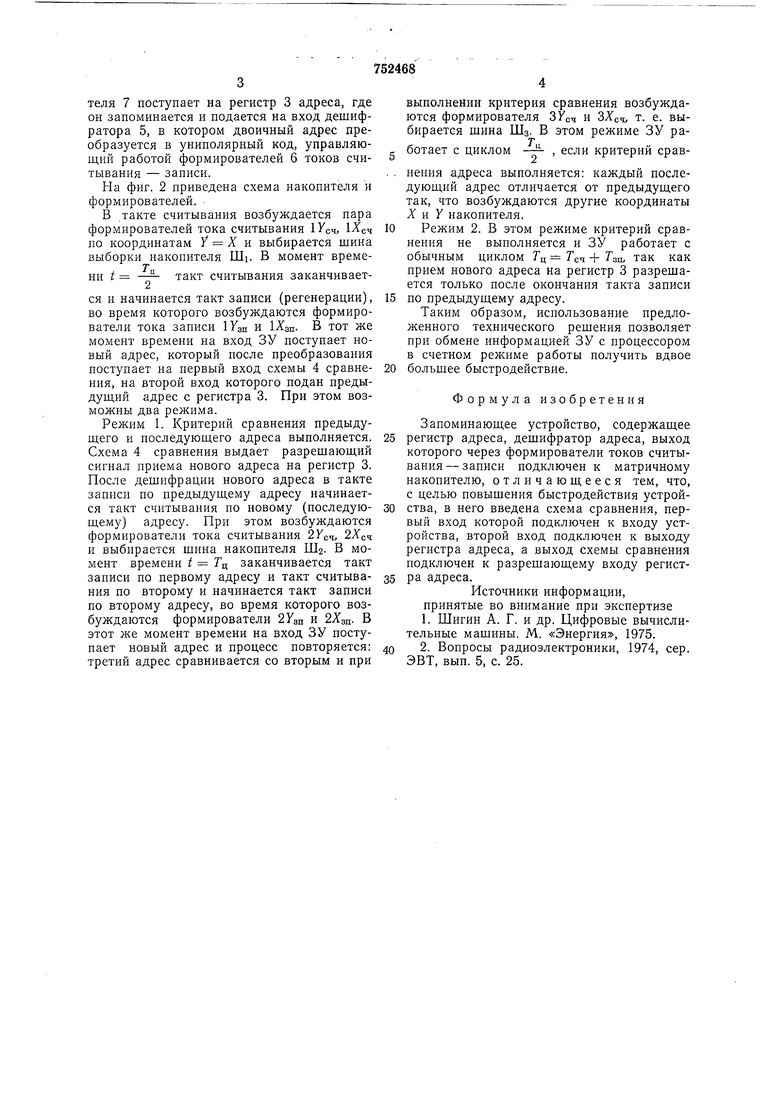

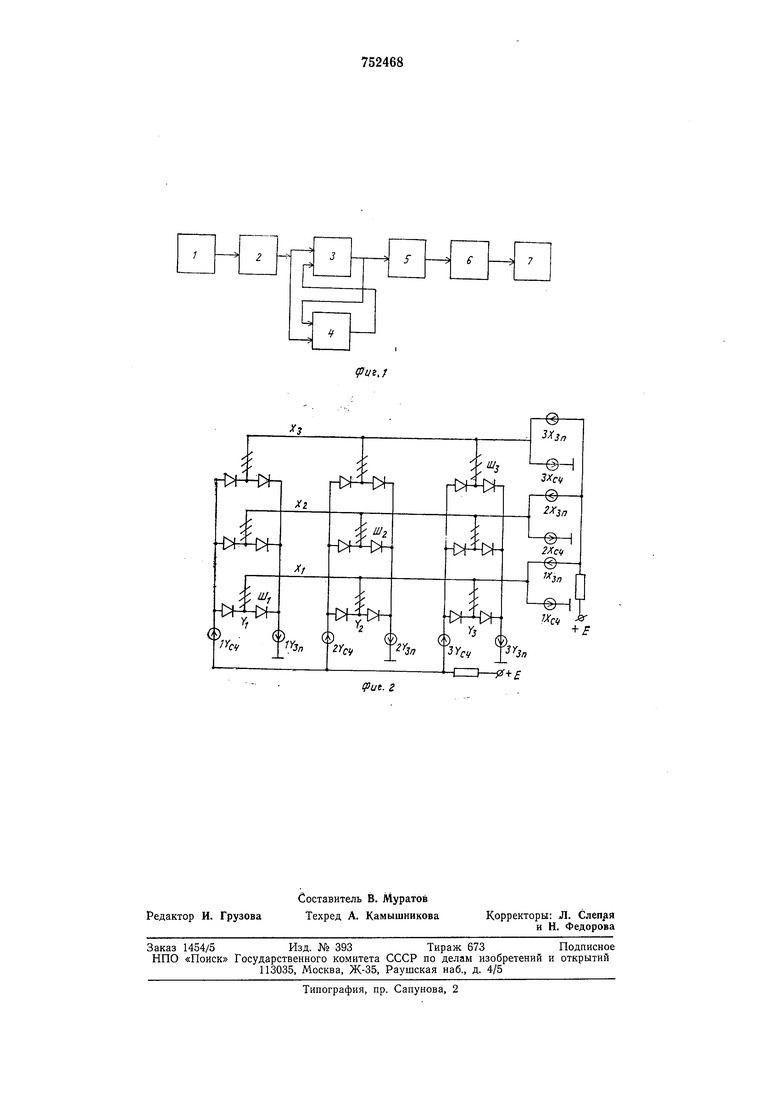

На фиг. 2 приведена схема накопителя и формирователей.

В такте считывания возбуждается пара формирователей тока считывания 1Усч, по координатам У X и выбирается шина выборки накопителя Шь В момент времеТ

ни t -- такт считывания заканчивается и начинается такт записи (регенерации), во время которого возбуждаются формирователи тока записи 1Узп и . В тот же момент времени на вход ЗУ поступает новый адрес, который после преобразования поступает на первый вход схемы 4 сравнения, на второй вход которого подан предыдущий адрес с регистра 3. При этом возможны два режима.

Режим 1. Критерий сравнения предыдущего и последующего адреса выполняется. Схема 4 сравнения выдает разрешающий сигнал приема нового адреса на регистр 3. После дешифрации нового адреса в такте записи по предыдущему адресу начинается такт считывания по новому (последующему) адресу. При этом возбуждаются формирователи тока считывания 2Yc4j 2Хсч и выбирается шина накопителя Ш2. В момент времени t Тц заканчивается такт записи по первому адресу и такт считывания по второму и начинается такт записи по второму адресу, во время которого возбуждаются формирователи 2Узп и 2Хзи- В этот момент времени на вход ЗУ поступает новый адрес и процесс повторяется: третий адрес сравнивается со вторым и при

выполнении критерия сравнения возбуждаются формирователя ЗУсч и т. е. выбирается шина Шз. В этом режиме ЗУ раТ

ботает с циклом -- , если критерий сравнения адреса выполняется: каждый последующий адрес отличается от предыдущего так, что возбуждаются другие координаты X н Y накопителя.

Режим 2. В этом режиме критерий сравнения не выполняется и ЗУ работает с обычным циклом Гц Геч + Гзц, так как прием нового адреса на регистр 3 разрешается только после окончания такта записи

по предыдущему адресу.

Таким образом, использование предложенного технического решения позволяет при обмене информацией ЗУ с процессором в счетном режиме работы получить вдвое

большее быстродействие.

Формула изобретения

Запоминающее устройство, содержащее регистр адреса, дешифратор адреса, выход которого через формирователи токов считывания-записи подключен к матричному накопителю, отличающееся тем, что, с целью повышения быстродействия устройства, в него введена схема сравнения, первый вход которой подключен к входу устройства, второй вход подключен к выходу регистра адреса, а выход схемы сравнения подключен к разрешающему входу регистра адреса.

Источники информации, принятые во внимание при экспертизе 1. Шигин А. Г. и др. Цифровые вычислительные машины. М. «Энергия, 1975. 2. Вопросы радиоэлектроники, 1974, сер. ЭВТ, вып. 5, с. 25.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1978 |

|

SU799001A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Запоминающее устройство типа 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1979 |

|

SU773731A1 |

| Полупостоянное запоминающее устройство | 1980 |

|

SU900314A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Запоминающее устройство типа 2,5 д | 1976 |

|

SU607278A1 |

| Буферное запоминающее устройство | 1981 |

|

SU993333A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОСЙ1Ч '^ | 1972 |

|

SU436389A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| Запоминающее устройство | 1978 |

|

SU769624A1 |

Авторы

Даты

1980-07-30—Публикация

1978-12-07—Подача