I

Изобретение относится к вычислительной технике и может быть использовано при построении устройств хранения дискретной информации с неразрушающнм считыванием.

Известно ЗУ типа 2Д с неразрушающим считыванием информации на многоотверстных ферритовых элементах (МЭФ), содержащее накопитель, формирователи токов записи и считывания, генераторы импул -: ,Q сов и логические элементы IJ.

Недостатком этого ЗУ является невысокая надежность.

Наиболее близким по технической сущности к изобретению является ЗУ.типа 2Д)5 с неразрушающим считыванием информации на МФЭ, которое содержит накопитель, первый вход которого соедргаен с выходом формирователя разрядных токов записи, второй вход - с выходом формирователя 20 адресных токов -записи, а третий вход с выходом формирователя адресных токов считывания, первый вход которого соединен гС выходом дешифратора адреса, а второй -

с выходом первого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов И, третий элемент И, выход которого соединен со вторым входом формирователя адресных токов записи, первый вход которого подключен к выходу дешифратора адреса, генератор импульсов, подключенный к первым входам первого и четвертого элементов И, счетчик тактов, вход которого соединен с выходом четвертого элемента И и с первыми входами второго и третьего элементов И, а первый, второй и третий выходы, подключены соответственно, ко вторым входам второго и третьего элемента И и входу дешифратора тактов, пятый,, шестой и седьмой элементы И, второй элемент ИЛИ 2.

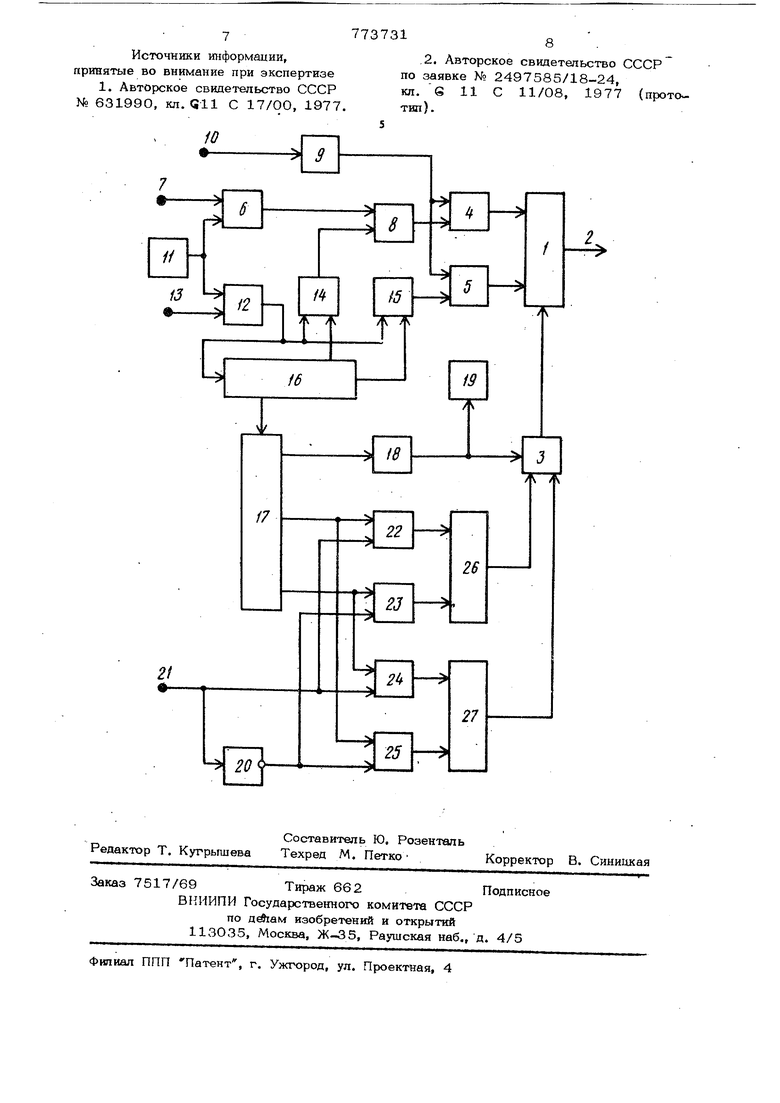

Недостатком такого устройства является большое время цикла записи,так, как, в цикле записи производится воздействие на ферритовые элементы адресным током считывания последовательно по всем адресам массива накопителя. охваченного одной разрядной штюй записи. Цель изобретения - повышение быстродействия известного ЗУ типа 2Д с неразрушаюшям считыванием информации на МФЭ. Поставленная цель достигается тем, что устройство содержит третий элемент ИЛИ, восьмой элемент И, элемент НЕ, ключ и блок накопителей энергии, первый выход дешифратора тактов подключен к управляющему входу ключа, выход которого подключен к первому входу формирователя разрядных токов записи и блоку накопителей энергии, а второй и третий выходы дешифратора тактов подключены к первым входам пятого, восьмого и шестого, седьмого эле ментов И соответственно, вторые входы шестого и восьмог элементов И подключены к выходу элемента НЕ, вход которого соединен со вторыми входами пятого и седьмого элементов И, выходы пятого и шестого элементов И подключены соответственно к первому и второму входам втордго эле мента ИЛИ, выход которого соединен со вторым входом формирователя разрядных токов, третий вход которого подключен к выходу третьего элемента ИЛИ, а первый и второй входы третьего элемента ИЛИ подключены к выходам седьмого и восьмого элементов И соотв-етственно. На чертеже изображена блок-схема предлагаемого ЗУ. Устройство содержит накопитель 1, выходные числовые шины , 2, формирователь 3 разрядных токов записи, формирователь 4 адресных токов считывания и формирователь 5 адресных токов записи, первый элемент И 6, управляющую щину Считывание 7, первый элемент ИЛИ 8, дешифратор 9 адреса, - входные адресные шины 10, генератор 11 импуль сов, четвертый элемент И 12, управляющую шину Запись 13, второй элемент И 14, третий элемент И 15, счетчик 16 тактов, дешифратор 17 тактов, ключ 18, блок 19 накопителей энергии (например, конденсатор), элемент НЕ 20, входные числовые Ш1шы 21, пятый 22, шестой 2 седьмой 24 и восьмой 25 элементы И, второй 26 и третий 27 элементы ИЛИ. Работа устройства происходит следующим образом, В режиме считывания информации при наличии на управляющей шине Считывание 7 разрешающего поте щиала, синхро импульс с генератора 11 и myльcoв чеп первый элемент И 6 и первый элемент ИЛИ 8 поступает на вход формирователя 4 адресных токов считывания, выбранного дешифратора 9 адреса, в соответствии с кодом адреса на шинах адреса 10. В результате, по избранной координате накопителя 1 протекает ток считывания; и на выходных числовых шинах 2 вырабатывается код считанного числа, В режиме записи информации на гправляющей шине Запись 13 имеется разрешающий потенциал и синхроимпульс с генератора 11 Поступает через четвертый элемент И 12 на вход счетчика 56 тактов, второй 14 и третий 15 элементы И, Вторые входы второго 14 и. третьего 15 элементов И уп{эавляются счетчиком 16 таким образом, что в течение определенного времени синхроимпульс . поочередно проходит через один из этих элементов И, а, следовательно, поочередно срабатывают формирователи адресных токов записи 5 и считывания 4. Одновременно с этим, дешифратор 17 тактов, опирающийся на счетчик 16 тактов, выдает на первом выходе сигнал включения ключа 18, который подает питание на формирователи 3 разрядных токов и заряжает блок 19 накьпителей энергии, кроме того, в это время дешифратор 17 тактов на своем втором выходе выдает опрос на пятый 22 и восьмой 25 элементы И. Код числа, присутствующий на числовых шинах 21, или его инверсия на выходе элемента НЕ 2О разрешает прохождение опроса через пятый 22 или восьмой 25 элемент И, затем через второй 26 или третий 25 элемент ИЛИ опрос поступает на второй или третий входы формирователя 3 разрядных токов, обеспечивая формирование соответствующей полярности разрядного тока накопителя 1,.В результате, по разрядным шинам накопителя 1 протекают токи, направление каждого из которых соответствует значению кода соответствующего разряда числовых шин 21, а по выбранной координатной шине накопителя 1 протекают разнополярные координатные токи, обеспечивая необходимые изменения магнитных состояний запоминающих элементов, т.е. происходит запись информации по выбранному адресу. Необходимое для этого время отсчитывается счетчиком 16 тактов, который при достижении определенной кодовой комбинации запрещает прохождение синхроимпульсов через второй 14 и третий 15 элементы И, запрещая тем сямым срабатывание формирователей адресных токов считывания 4 и записи 5. Оцновре менно дешифратор 17 raifTOB снимает сиг нал включения на ключ 18, выдает опрос на своем третьем выходе и снимает онро со Второго выхода. В соответствии скодом числа на шинах 21 или его инверсии 20, открывается шестой 23 или седьмой 24 элементы И и опрос с дешифратора 17 через третий 27 или второй 26 элемент ИЛИ поступает на третий или второй вход формирователя 3 разрядных токов, обеспечивая прот1тоположную полярность разрядного тока. В следующий момент времени деа1ифратор 17 тактов снова выдает опрос на своем втором выходе снимая его с третьего выхода, и так далее, до достижения заданного количества (3 - 7) в зависимости от типа запоминающего элемента разнополярных импуль- сов разрядного, тока. Так, как,- при прохождении этой пачки разрядных токовых импульсов ключ 18 отключен, амплитуда разрядных токов в пачке определяется потенциалом накопленной энергии в блоке 19 (например на конденсаторе), который снижается до нуля по мере расхода энергии при прохождении этих токов. Таким образом, происходит нормализация состояний запоминающих элементов по всем разрядам и адресам, что обеспечивает стабильность выходных сигналов накопителя по первому после цикла записи обращению к любому адресу в режиме считывания, кроме выбранного при записи. В последующий промежуток времени, который также определяется кодовой комбинацией счетчика 16 производится известная нормализация магнитаого состо$тия запоминающих элементов выбранного при записи адреса, воздействием на избранную координату накопителя 1 нескол; ких токов считывания, путем подачи не- скольких опросов со счетчика 16 через второй элемент И 14, первый элемент ИЛИ 8 на формирователь 4 адресных токов считывания. На этом цикл записи заканчивается. Предлагаемое запоминающее устройство отличается от известного yctpoй- ства типа 2Д на многоотверстных ферритовых элементах, имеющего стабиль- ные параметры выходных сигналов накопителя, существенно меиьщим време- нем цикла записи, что расширяет область применения подобных запоминающих устройств. 7 31 3 о б р Формула е т е н и я Запоминающее устройство типа 2Д с норазрушаюшим считыванием шгформадн на многоотверстных ферритовых элементах, содержащее накопитель, первый вход ко- торого соединен с выходом формирователя разрядных токов записи, второй вход - с выходом формирователя адресных токов записи, а третий вход - с выходом формирователя адресных токов считывания, первый вход которого соединен с выходом дешифратора адреса, а второй - с выходом первого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и втрого элемента И, третий элемент И, выход которого соединен со вторым входом форм фователя адресных токов записи, первый вход которого подключен к выходу дешифратора адреса, генератор импульсов, подключенный к первым входам первого и четвертого элеме1{тов И, счетчик тактов, вход которого соединен с выходом четвертого элемента И и с первыми входами второго и третьего элементов И, а первый, второй и третий выходы, подключены соответственно, ко вторым входам второго и третьего элемента И и входу дещифратора тактов, пятый, шестой и седьмой элементы И, второй элемент ИЛИ, отличающееся тем, что, с целью повышения быстродействия запоминающего устройства, оно содержит третий элемент ИЛИ, восьмой элемент И, элемент НЕ, ключ и блок накопителей энергии, первый выход дешифратора тактов подключен к управляющему входу ключа, выход которого подключен к первому входу формирователя разрядных токов записи и блоку накопителей энергии,. а второй и третий - выходы дешифратора тактов подключены к первым входам пятого, восьмого и шестого, седьмого элементов И соответственно, вторые входы шестого и восьмого элементов И подключены к выходу элемента НЕ, вход которого соединен со вторыми входами пятого и седьмого элементов И, выходы пятого и шестого элементов И чены соответстве1шо к первому и второму входам второго элемента ИЛИ, выход коорого соединен со вторым входом ормирователя разрядных токов, треий вход которого подключен к выоду . третьего элемента ИЛИ, а порый и второй входы третьего элеента ИЛИ подключены к выхода.чг едьмого и восьмого элеметгтов И соотетственно.

Источники информаяии, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 631990, кл. Q11 С 17/00, 1977.

773731

,2. Авторское свидетельство СССР по заявке № 2497585/18-24, кл. в 11 С 11/08, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1019495A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Голографическое постоянное запоминающее устройство со сменным носителем голограмм | 1990 |

|

SU1691889A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1100640A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

Авторы

Даты

1980-10-23—Публикация

1979-04-12—Подача