1

Изобретение относится к запоминающим устройствам.

Известны устройства для контроля памяти, содержащие блоки распределе- с ния информации по исправным разрядам блоков памяти с дефектными ячейками

м .

Недостаком этих устройст является снижение эффективной емкости на- Ю копителя.

Наиболее близким техническим решением к предлагаемому является устройство для контроля памяти, содержащее первый и второй накопители, схему сравнения, блок формирования адреса и блок управления, причем один из выходов блока формирования адреса подключен ко входу второго накопителя, выход которого соединен с первьам 2Q входом схемы сравнения, выход которой подключен ко входу блока управления и первому входу первого накопителя, управляющие входы накопителей и первый выход устройства соединены с вы- 25 ходами блока управления 2 .

Недостаток этого устройства заключается в том, что оно не позволяет использовать обнаруженные дефектны е ячейки накопителя, что снижает функ- JQ

циональные возможности устройства и ограничивает область его применения. Цель изобретения - расширение области применения устройства за счет обеспечения возможности использования дефектных ячеек контролируемой Пс1мя ти.

Поставленная цель достигается тем, что устройство содержит блок коррекции адреса, элементы ИЛИ, коммутаторы и генератор кодов коммутации, причем входы блока коррекции адреса подключены соответственно к выходам блоха формирования адреса и выходу первого накопителя, а выход блока коррекции адреса соединен со вторым выходом устройства, вход генератора i oдов коммутации подключен к одному из выходов блока управления, выход генератора кодов коммутации подключен к одним из входов элементов ИЛИ, другие эходы которых соединены с одним из выходов блока формирования адреса, выходы которых подключены ко второму входу первого накопителя, входы первого коммутатора подключены к выходам генератора кодов коммутации и второго накопителя, а выход первого коммутатора соединен с тгретьим выходом устройства, входы второго коммутатора подключены соответственн к выходам генератора кодов коммутации и первого накопителя и входу устройства, а выход второго коммутатора соединен со вторым входом схемы сравнения.

При этом блок коррекции адреса целесообразно выполнить содержащим сумматор, элементы ИЛИ и регистр,причем одни входы элементов ИЛИ подключены к выходу регистра, выходы элементы ИЛИ соединены с одним из входов сумматора, выход которого подключен к выходу блока коррекции адреса, входы которого соединены соответственно со входами регистра и другими входами сумматора и элемента ИЛИ.

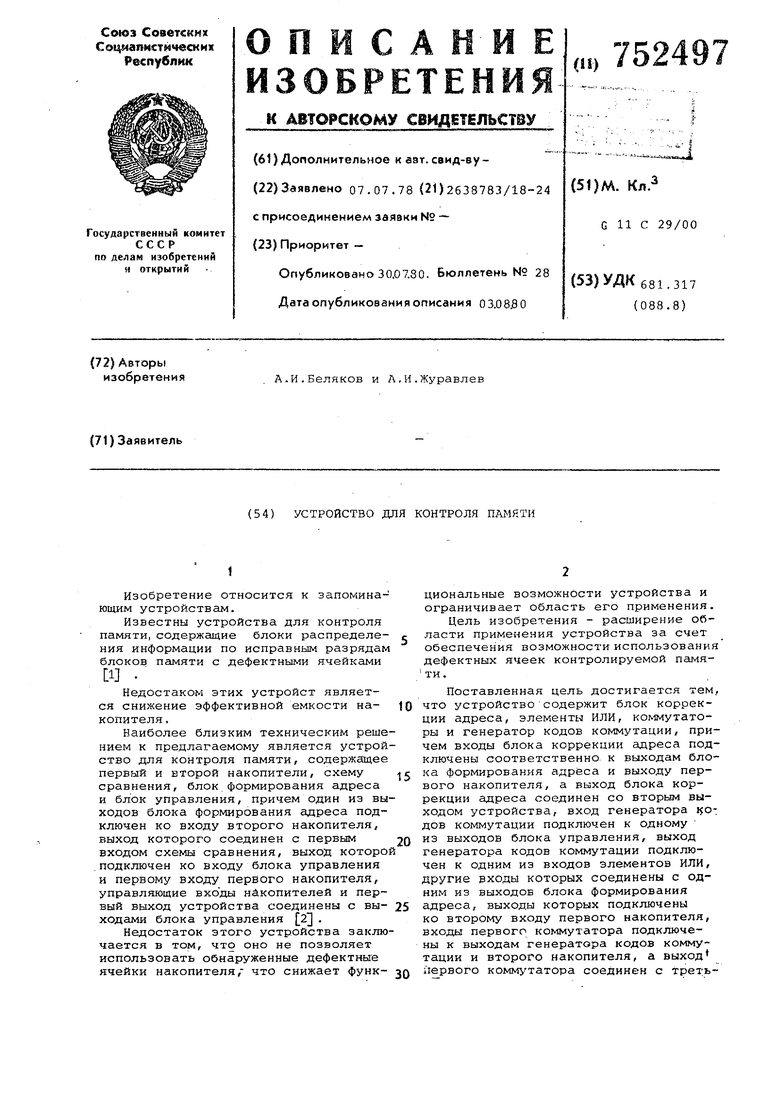

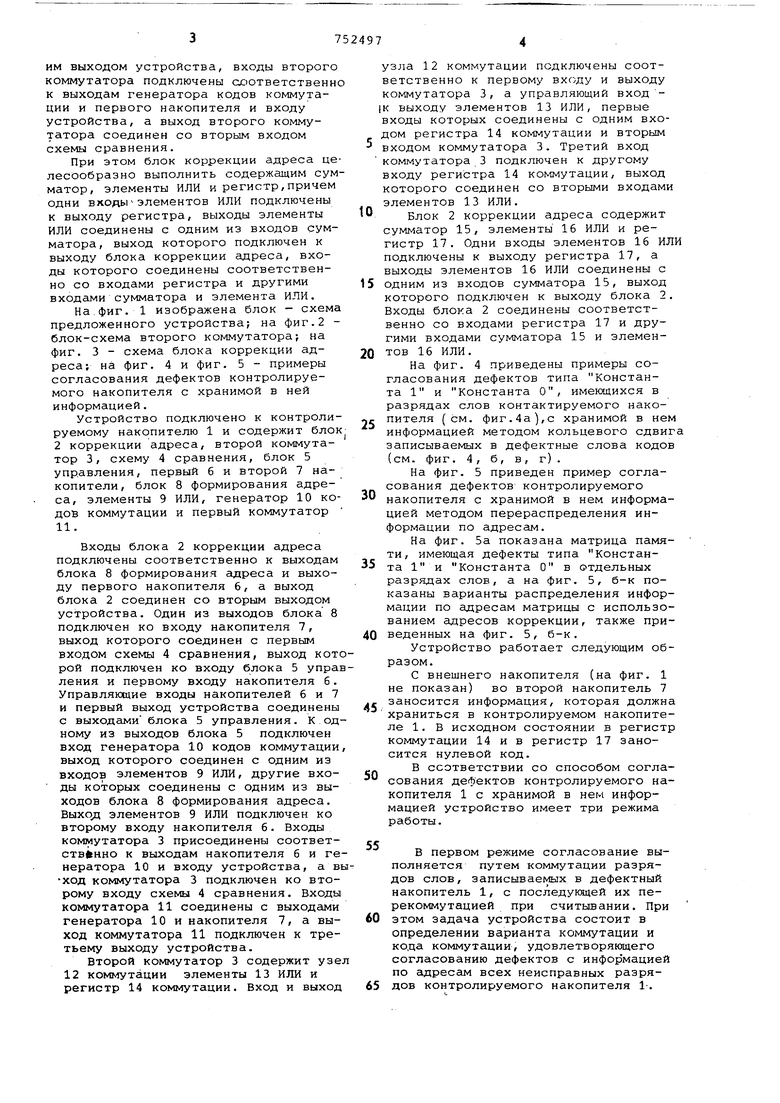

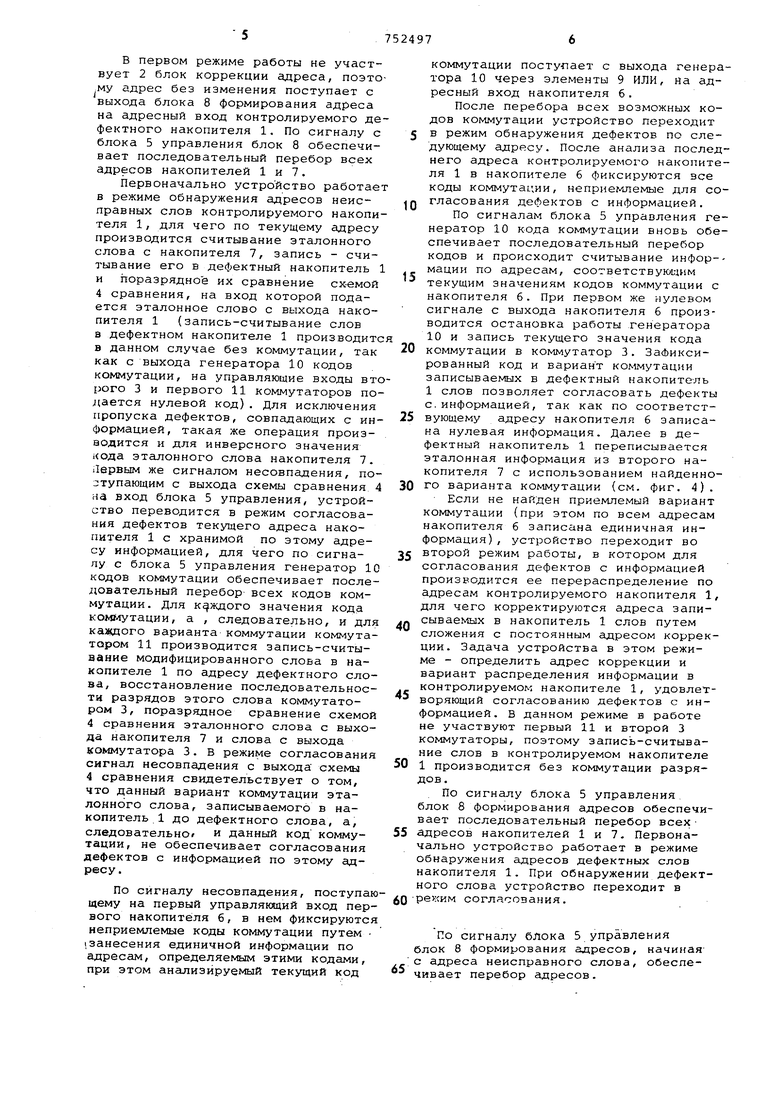

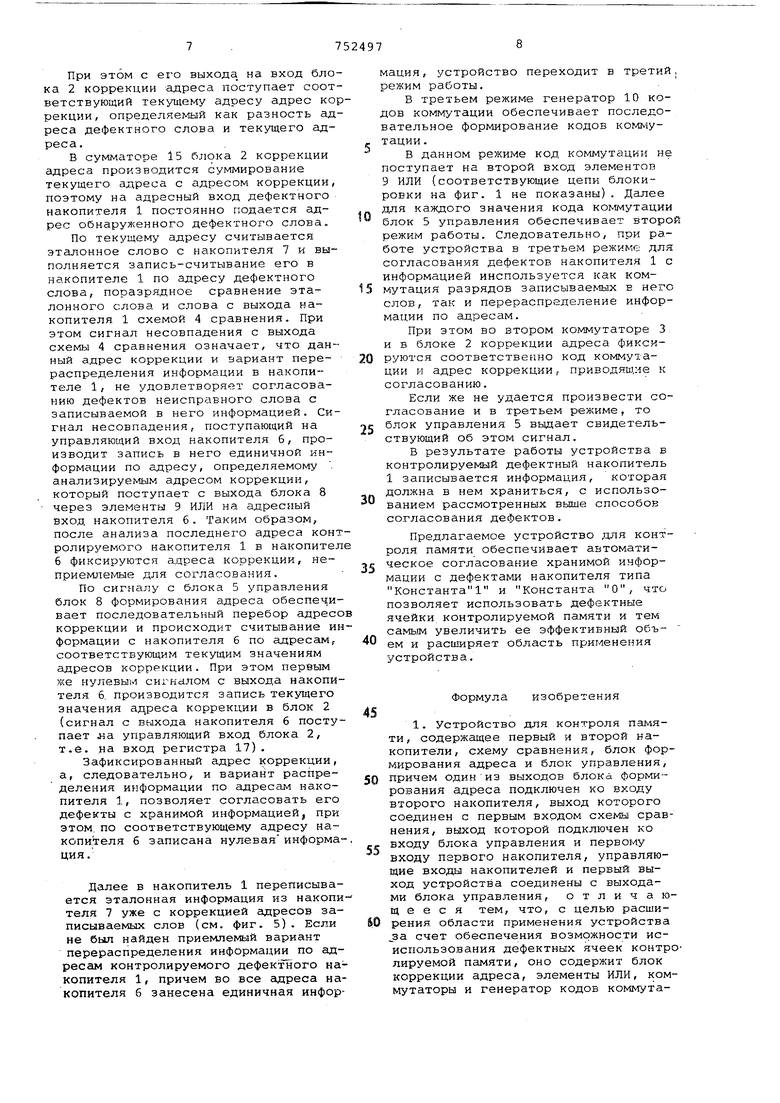

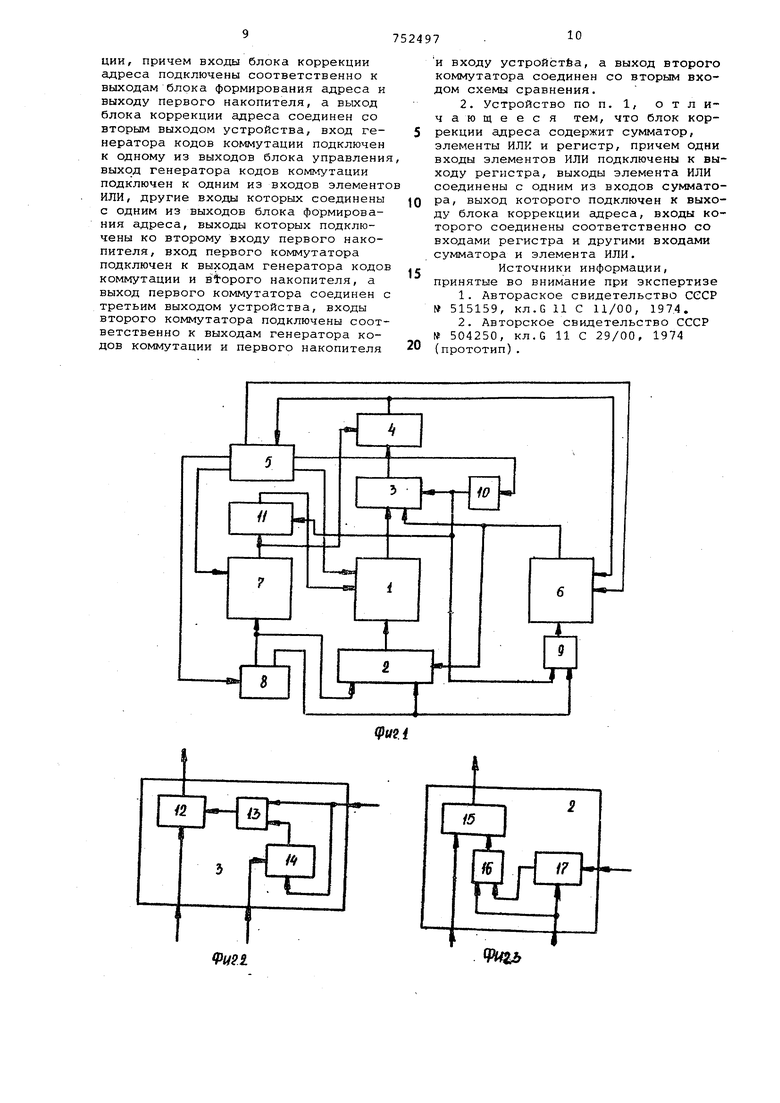

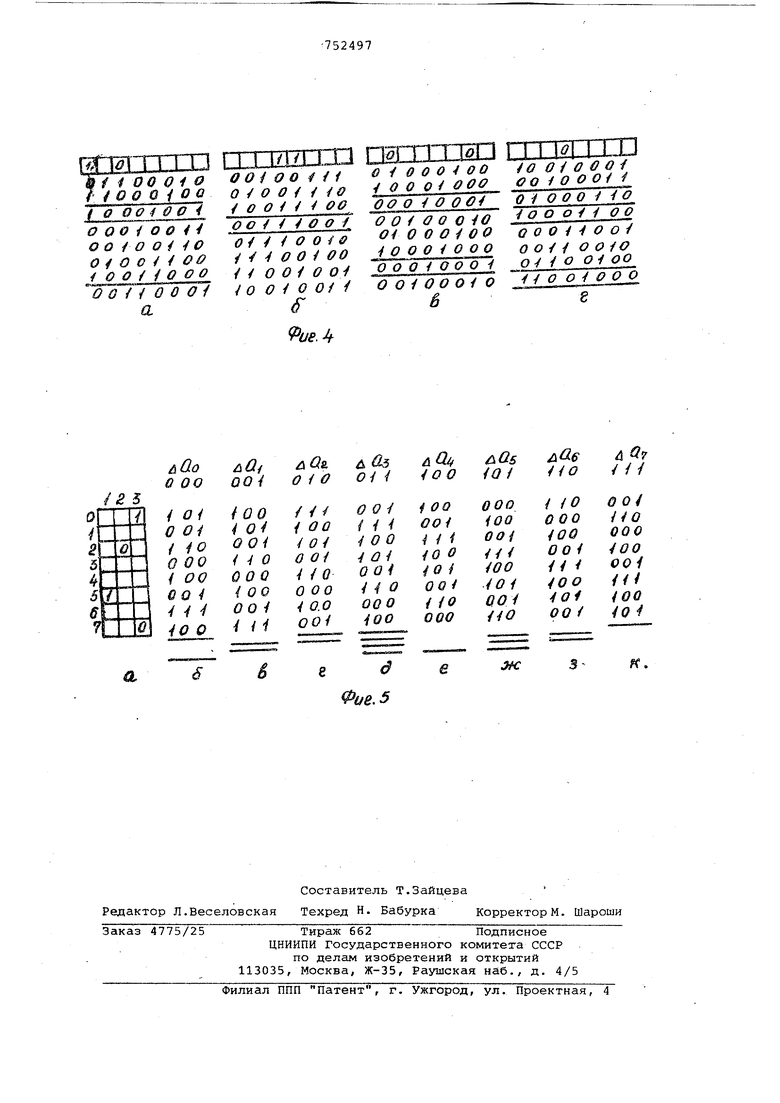

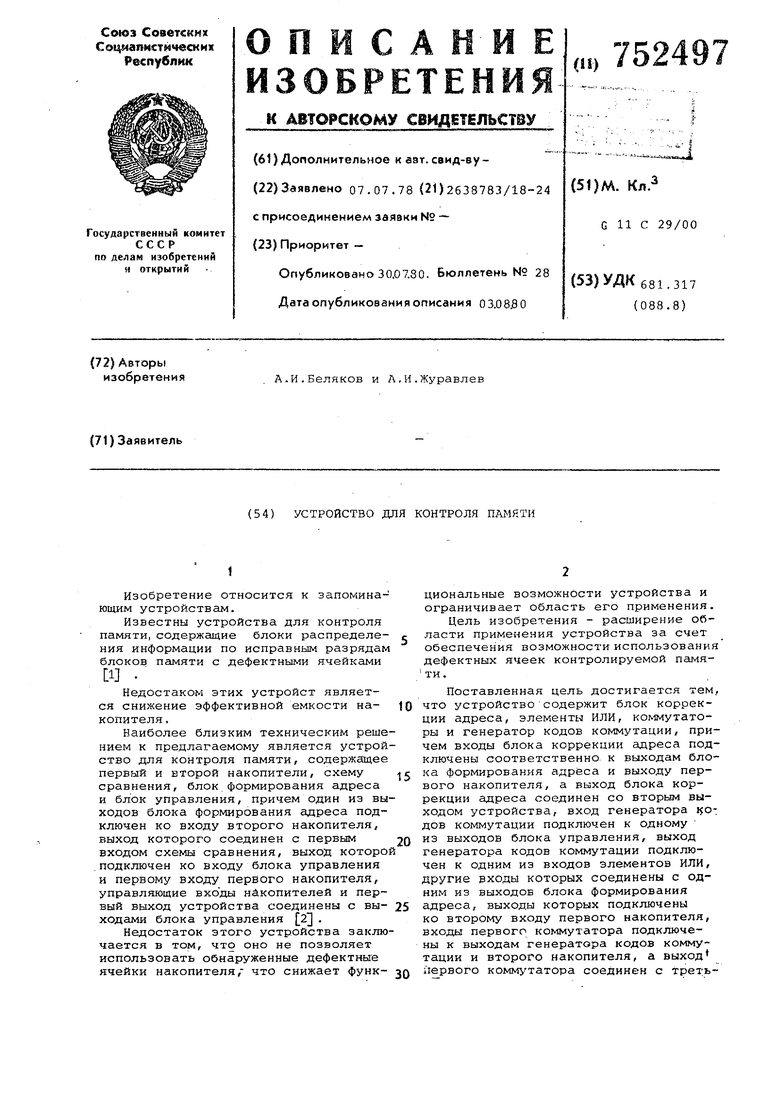

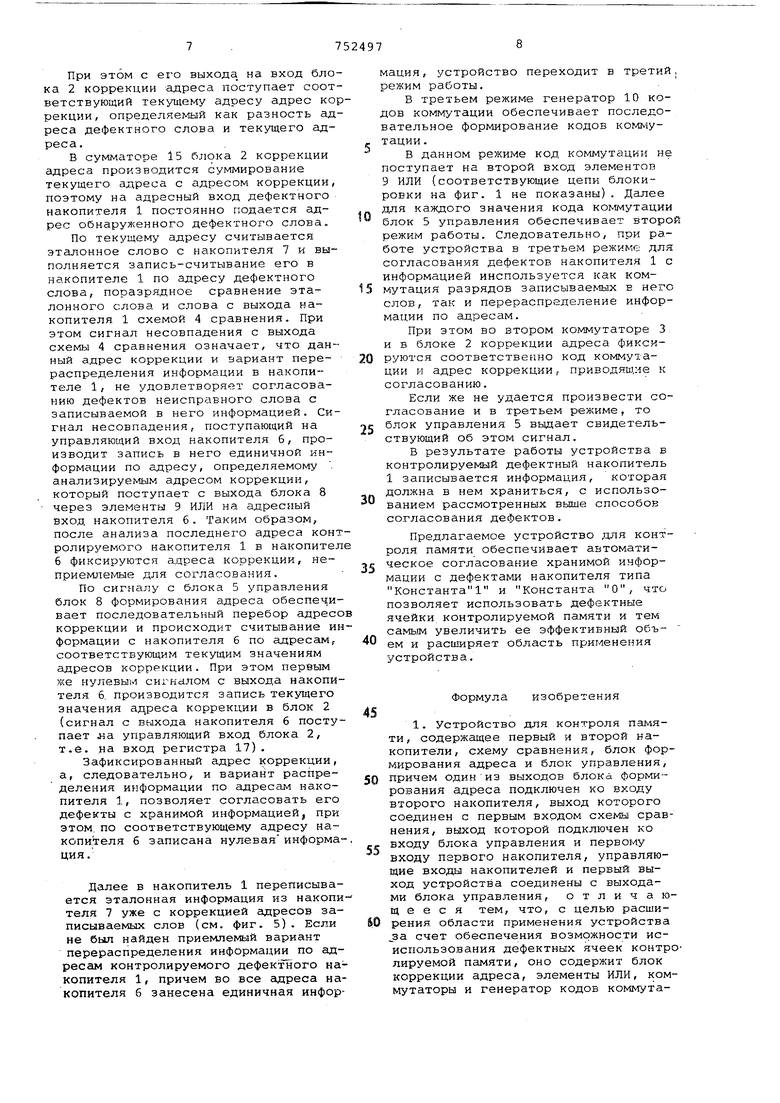

На.фиг. 1 изображена блок - схема предложенного устройства; на фиг.2 блок-схема второго коммутатора; на фиг. 3 - схема блока коррекции адреса; на фиг. 4 и фиг. 5 - примеры согласования дефектов контролируемого накопителя с хранимой в ней информацией.

Устройство подключено к контролируемому накопителю 1 и содержит блок 2 коррекции адреса, второй коммутатор 3, схему 4 сравнения, блок 5 управления, первый 6 и второй 7 накопители, блок 8 формирования адреса, элементы 9 ИЛИ, генератор 10 кодов коммутации и первый коммутатор 11.

Входы блока 2 коррекции адреса подключены соответственно к выходам блока 8 формирования адреса и выходу первого накопителя 6, а выход блока 2 соединен со вторым выходом устройства. Один из выходов блока 8 подключен ко входу накопителя 7, выход которого соединен с первым входом схемы 4 сравнения, выход котрой подключен ко входу блока 5 упраления и первому входу накопителя б. Управляющие входы накопителей 6 и 7 и первый выход устройства соединены с выходами блока 5 управления. К одному из выходов блока 5 подключен вход генератора 10 кодов коммутации выход которого соединен с одним из входов элементов 9 ИЛИ, другие входы которых соединены с одним из выходов блока 8 формирования адреса. Выход элементов 9 ИЛИ подключен ко второму входу накопителя б. Входы коммутатора 3 присоединены соответств нно к выходам накопителя б и генератора 10 и входу устройства, а вход коммутатора 3 подключен ко второму входу схемы 4 сравнения. Входы коммутатора 11 соединены с выходами генератора 10 и накопителя 7, а выход коммутатора 11 подключен к третьему выходу устройства.

Второй коммутатор 3 содержит узе 12 коммутации элементы 13 ИЛИ и регистр 14 коммутации. Вход и выход

узла 12 коммутации подключены соответственно к первому вх(;ду и выходу коммутатора 3, а управляющий вход|к выходу элементов 13 ИЛИ, первые входы которых соединены с одним входом регистра 14 коммутации и вторым входом коммутатора 3. Третий вход коммутатора 3 подключен к другому входу регистра 14 коммутации, выход которого соединен со вторыми входами элементов 13 ИЛИ.

Блок 2 коррекции адреса содержит сумматор 15, элементы 16 ИЛИ и регистр 17. Одни входы элементов 16 ИЛ подключены к выходу регистра 17, а выходы элементов 16 ИЛИ соединены с одним из входов сумматора 15, выход которого подключен к выходу блока 2 Входы блока 2 соединены соответственно со входами регистра 17 и другими входами сумматора 15 и элементов 16 ИЛИ.

На фиг. 4 приведены примеры согласования дефектов типа Константа 1 и Константа О, имеющихся в разрядах слов контактируемого накопителя (см. фиг.4а),с хранимой в нем информацией методом кольцевого сдвиг записываемых в дефектные слова кодов (см. фиг. 4, б, в, г).

На фиг. 5 приведен пример согласования дефектов контролируемого накопителя с хранимой в нем информацией методом перераспределения информации по адресам.

На фиг. За показана матрица памяти, имеющая дефекты типа Константа 1 и Константа О в отдельных разрядах слов, а на фиг. 5, б-к показаны варианты распределения информации по адресам матрицы с использованием адресов коррекции, также приведенных на фиг. 5, б-к.

Устройство работает следующим образом.

С внещнего накопителя (на фиг. 1 не показан) во второй накопитель 7 заносится информация, которая должна храниться в контролируемом накопителе 1. В исходном состоянии в регистр коммутации 14 и в регистр 17 заносится нулевой код.

В соответствии со способом согласования дефектов контролируемого накопителя 1 с хранимой в нем информацией устройство имеет три режима работы.

В первом режиме согласование выполняется путем коммутации разрядов слов, записываемых в дефектный накопитель 1, с последующей их перекоммутацией при считывании. При этом задача устройства состоит в определении варианта коммутации и кода коммутации, удовлетворяющего согласованию дефектов с информацией по адресам всех неисправных разрядов контролируемого накопителя 1-.

В первом режиме работы не участвует 2 блок коррекции адреса, поэто.му адрес без изменения поступает с выхода блока 8 формирования адреса на адресный вход контролируемого дефектного накопителя 1. По сигналу с блока 5 управления блок 8 обеспечивает последовательный перебор всех адресов накопителей 1 и 7.

Первоначально устройство работает в режиме обнаружения адресов неисправных слов контролируемого накопителя 1, для чего по текущему адресу производится считывание эталонного слова с накопителя 7, запись - считывание его в дефектный накопитель 1 и поразрядное их сравнение сх-емой 4 сравнения, на вход которой подается эталонное слово с выхода накопителя 1 (запись-считывание слов в дефектном накопителе 1 производитс в данном случае без коммутации, так как с выхода генератора 10 кодов коммутации, на управляющие входы второго 3 и первого 11 коммутаторов подается нулевой код). Для исключения пропуска дефектов, совпадающих с информацией, такая же операция производится и для инверсного значения кода эталонного слова накопителя 7. Лервым же сигналом несовпадения, по::;тупающим с выхода схемы сравнения 4 на вход блока 5 управления, устройство переводится в режим согласования дефектов текущего адреса накопителя 1 с хранимой по этому адресу информацией, для чего по сигналу с блока 5 управления генератор 10 кодов коммутации обеспечивает последовательный перебор всех кодов коммутации. Для каждого значения кода коммутации, а , следовательно, и для каждого варианта коммутации коммутатором 11 производится запись-считывание модифицированного слова в накопителе 1 по адресу дефектного слова, восстановление последовательности разрядов этого слова коммутатором 3, поразрядное сравнение схемой 4 сравнения эталонного слова с выхода накопителя 7 и слова с выхода коммутатора 3. В режиме согласования сигнал несовпадения с выхода схемы 4 сравнения свидетельствует о том, что данный вариант коммутации эталонного слова, записываемого в накопитель 1 до дефектного слова, а, следовательно и данный код коммутации, не обеспечивает согласования дефектов с информацией по этому адресу.

По сигналу несовпадения, поступающему на первый управляющий вход первого накопителя 6, в нем фиксируются неприемлемые коды коммутации путем (Занесения единичной информации по адресам, определяемым этими кодами, при этом анализируемый текущий код

коммутации поступает с выхода генератора 10 через элементы 9 ИЛИ, на адресный вход накопителя б.

После перебора всех возможных кодов коммутации устройство переходит в режим обнаружения дефектов по следующему адресу. После анализа последнего адреса контролируемого накопителя 1 в накопителе 6 фиксируются see коды коммутации, неприемлемые для согласования дефектов с информацией.

0

По сигналам блока 5 управления генератор 10 кода коммутации вновь обеспечивает последовательный перебор кодов и происходит считывание инфор-мации по адресам, соответствующим

5 текущим значениям кодов коммутации с накопителя 6. При первом же нулевом сигнале с выхода накопителя б производится остановка работы .генератора 10 и запись текущего значения кода

0 коммутации в коммутатор 3. Зафиксированный код и вариант коммутации записываемых в дефектный накопите-ль 1 слов позволяет согласовать дефекты с.информацией, так как по соответст5вующему адресу накопителя б записана нулевая информация. Далее в дефектный накопитель 1 переписывается эталонная информация из второго накопителя 7 с использованием найденного варианта коммутации (см. фиг. 4) .

0

Если не найден приемлемый вариант коммутации (при этом по всем адресам накопителя 6 записана единичная информация) , устройство переходит во второй режим работы, в котором для

5 согласования дефектов с информацией производится ее перераспределение по адресам контролируемого накопителя 1, для чего корректируются адреса записываемых в накопитель 1 слов путем

0 сложения с постоянным адресом коррекции. Задача устройства в этом режиме - определить адрес коррекции и вариант распределения информации в контролируемом накопителе 1, удовлет5воряющий согласованию дефектов с информацией. В данном режиме в работе не участвуют первый 11 и второй 3 коммутаторы, поэтому запись-считывание слов в контролируемом накопителе

0 1 производится без коммутации разрядов.

По сигналу блока 5 управления блок 8 формирования адресов обеспечивает последовательный перебор всех

5 адресов накопителей 1 и 7. Первоначально устройство работает в режиме обнаружения адресов дефектных слов накопителя 1. При обнаружении дефектного слова устройство переходит в режим согласования.

0

По сигналу блока 5 управления блок 8 формирования адресов, начиная ;с адреса неисправного слова, обеспе65чивает перебор адресов.

При этом с его выхода на вход блока 2 коррекции адреса поступает соответствующий текущему адресу адрес корекции, определяемый как разность адреса дефектного слова и текущего адреса.

В сумматоре 15 блока 2 коррекции адреса производится суммирование текущего адреса с адресом коррекции, поэтому на адресный вход дефектного накопителя 1 постоянно подается адрес обнаруженного дефектного слова.

По текущему адресу считывается эталонное слово с накопителя 7 и выполняется запись-считывание его в накопителе 1 по адресу дефектного слова, поразрядное сравнение эталонного слова и слова с выхода накопителя 1 схемой 4 сравнения. При этом сигнал несовпадения с выхода схемы 4 сравнения означает, что дан ный адрес коррекции и вариант перераспределения информации в накопителе 1, не удовлетворяет согласованию дефектов неисправного слова с записываемой в него информацией. Сигнал несовпадения, поступающий на управляющий вход накопителя 6, производит запись в него единичной информации по адресу, определяемому . анализируемым адресом коррекции, который поступает с выхода блока 8 через элементы 9 ИЛИ на годресный вход накопителя 6. Таким образом, после анализа последнего адреса контролируемого накопителя 1 в накопител 6 фиксируются а,цреса коррекции, неприемлемые для согласования.

По сигналу с блока 5 управления блок 8 формирования адреса обеспечивает последовательный перебор адресо коррекции и происходит считывание информации с накопителя 6 по адресам, соответствующим текущим значениям адресов коррекции. При этом перёым же нулевы1и сигналом с выхода накопителя 6. производится запись текущего значения адреса коррекции в блок 2 (сигнал с выхода накопителя 6 поступает 5а управляющий вход блока 2, т.е. на вход регистра 17).

Зафиксированный адрес коррекции, а, следовательно, и вариант распределения информации по адресам накопителя 1, позволяет согласовать его дефекты с хранимой информацией, при этом, по соответствующему адресу накопителя б записана нулеваяинформа ция.

Далее в накопитель 1 переписывается эталонная, информация из накопителя 7 уже с коррекцией адресов записываемых слов (см. фиг. 5). Если не был найден приемлемый вариант перераспределения информации по адресам контролируемого дефекгного накопителя 1, причем во все гщреса накопителя б занесена единичная информация, устройство переходит в третий режим работы.

В третьем режиме генератор 10 кодов коммутации обеспечивает последовательное формирование кодов коммутации .

В данном режиме код коммутации не поступает на второй вход элементов 9 ИЛИ (соответствующие цепи блокировки на фиг. 1 не показаны). Далее для каждого значения кода коммутации блок 5 управления обеспечивает второ режим работы. Следовательно, при работе устройства в третьем режиме для согласования дефектов накопителя 1 с информацией инспользуется как коммутация разрядов записываемых в него слов, так и перераспределение информации по адресам.

При этом во втором коммутаторе 3 и в блоке 2 коррекции адреса фиксируются соответственно код коммутации и адрес коррекции, приводящие к согласованию.

Если же не удается произвести согласование и в третьем режиме, то блок управления 5 выдает свидетельствующий об этом сигнал.

В результате работы устройства в контролируемый дефектный накопитель 1 записывается информация, которая должна в нем храниться, с использованием рассмотренных выше способов согласования дефектов.

Предлагаемое устройство для контроля памяти обеспечивает автоматическое согласование хранимой информации с дефектами накопителя типа Константа и Константа О, что позволяет использовать дефектные ячейки контролируемой памяти и тем самым увеличить ее эффективный объем и расширяет область применения устройства.

Формула изобретения

1. Устройство для контроля памяти, содержащее первый и второй накопители, схему сравнения, блок формирования адреса и блок управления, причем одинИЗ выходов блока формирования адреса подключен ко входу второго накопителя, выход которого соединен с первым входом схемы сравнения, выход которой подключен ко входу блока управления и первому входу первого накопителя, управляющие входы накопителей и первый выход устройства соединены с выходами блока управления, о т л и ч а ющ е е с я тем, что, с целью расширения, области применения устройства j3a счет обеспечения возможности исиспользования дефектных ячеек контролируемой памяти, оно содержит блок коррекции адреса, элементы ИЛИ, коммутаторы и генератор кодов коммутации, причем входы блока коррекции адреса подключены соответственно к выходам блока формирования адреса и выходу первого накопителя, а выход блока коррекции адреса соединен со вторым выходом устройства, вход генератора кодов коммутации подключен к одному из выходов блока управления выход генератора кодов коммутации подключен к одним из входов элементо ИЛИ, другие входы которых соединены с одним из выходов блока формирования адреса, выходы которых подключены ко второму входу первого накопителя, вход первого коммутатора подключен к выходам генератора кодов коммутации и Bloporo накопителя, а выход первого коммутатора соединен с третьим выходом устройства, входы второго коммутатора подключены соответственно к выходам генератора кодов коммутации и первого накопителя

и входу устройстба, а выход второго коммутатора соединен со вторым входом схемы сравнения,

2. Устройство по п. 1, отличающееся тем, что блок коррекции адреса содержит сумматор, элементы ИЛИ и регистр, причем одни входы элементов ИЛИ подключены к выходу регистра, выходы элемента ИЛИ соединены с одним из входов сумматора, выход которого подключен к выхо0ду блока коррекции адреса, входы которого соединены соответственно со входами регистра и другими входами сумматора и элемента ИЛИ,

Источники информации,

5 принятые во внимание при экспертизе

1.Автораское свидетельство СССР № 515159, кл,С 11 С 11/00, 197,4.

2,Авторское свидетельство СССР № 504250, кл.С 11 С 29/00, 1974

0 (прототип),

CnniEZErn

00100 11

о о о i o / g / / / 00,

ool / / / о 0 f Q

i 4 о 0 00

/ / о о 1 о oi о о о Of

(Г «г

пззшхр

10 Oi о € Oi

л f j л /i ft 4

7 g / V j. /g 00/ / Q 0 0 1 о о (7 о / / о OiO

y/ oo±oo o

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля полупроводниковой памяти | 1984 |

|

SU1170513A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1444898A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970480A1 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| Устройство контроля электромагнитных параметров гибкого магнитного диска | 1988 |

|

SU1578627A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1270799A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1564693A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU920848A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-07—Подача