блока сравнения и третьим входам элементов И второй и третьей групп.

1170513

а выход соединен с входом первого регистра числа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Запоминающее устройство | 1980 |

|

SU911614A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1244726A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для контроля блоков памяти | 1979 |

|

SU790019A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОЛУПРОВОДНИКОВОЙ ПАМЯТИ, содержащее генератор импульсов, выходом соединенный с первым входом первого элемента И, выход которого соединен с входом формирователя сигналов, первый выход этого формирователя является первым выходом устройства, регистр адреса, триггер, его выход подключен к второму входу первого элемента И, первый вход является первым входом устройства, второй вход подключен к выходу второго элемента И, первый вход последнего соединен с выходом первого блока сравнения, первый вход которого подключен к выходу первого регистра числа, блок управления, первый и второй счетчики, их выходы соединены с входами первого коммутатора, выход которого является вторым вы- . ходом устройства, накопитель, прямой и инверсный выходы накопителя . подключены к первому и второму входам второго коммутатора, выход которого является третьим выходом устройства, отличающее с я тем, что, с целью повьшения быстродействия устройства, в него введены третий счетчик, его входы и выходы подключены соответственно к первым выходам и входу блока управления, второй вход которого подключен к второму выходу формирователя сигналов, первая группа элементов И, первые входы этих элементом подключены к второму выходу блока управления, вторые входы - к выходам первого коммутатора, а выходы - к входам регистра адреса, выходы блока управления с третьего по седьмой подключены к входам первого и второго счетчиков, третьим входам коммутаторов и второму входу второго элемента И соответственно, восьмой i выход блока управления является четвертым выходом устройства, третий (Л и четвертый входы подключены к вторым выходам первого и второго счетчиков, второй блок сравнения, четвертый счетчик, пятый счетчик, вход которого подключен к девятому выходу блока управления, а выход к одному из входов второго блока сравнения, другой вход этого блока о од соединен с выходом четвертого счетчика, вход которого подключен к ЩшД первому выходу формирователя сигна&Q лов, вторая группа элементов И, их первые входы подключены к выходам второго коммутатора, вторые - к второму выходу блока управления и первым входам элементов И второй группы, а выходы подключены к входу второго регистра числа, выход которого соединен с вторым входом первого блока сравнения, третья группа элементов И, первые входы которых являются вторьм входом устройства, вторые входы подключены к десятому выходу блока управления, третьи - к выходу второго

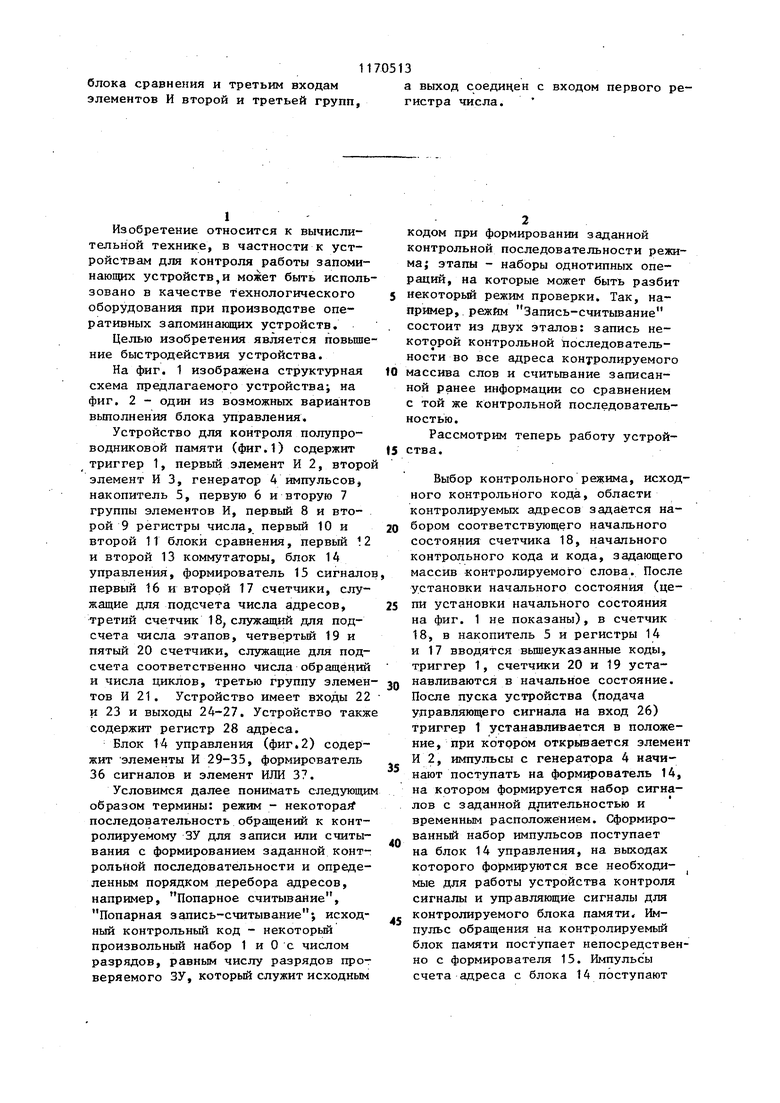

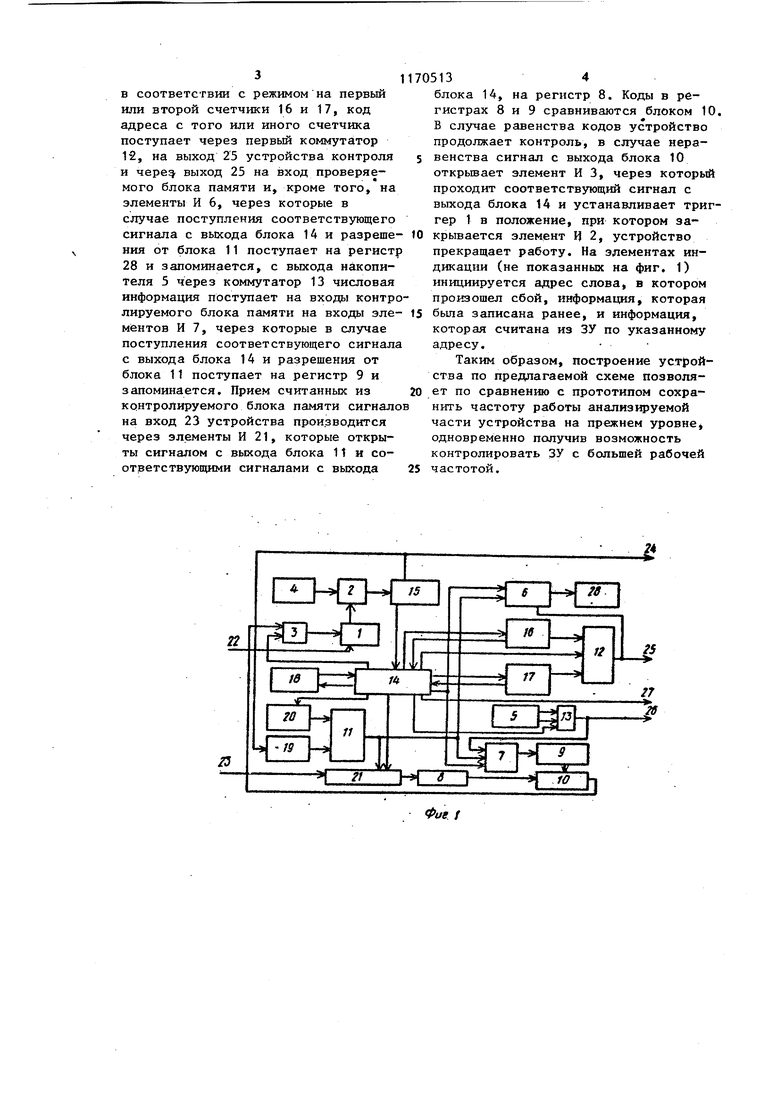

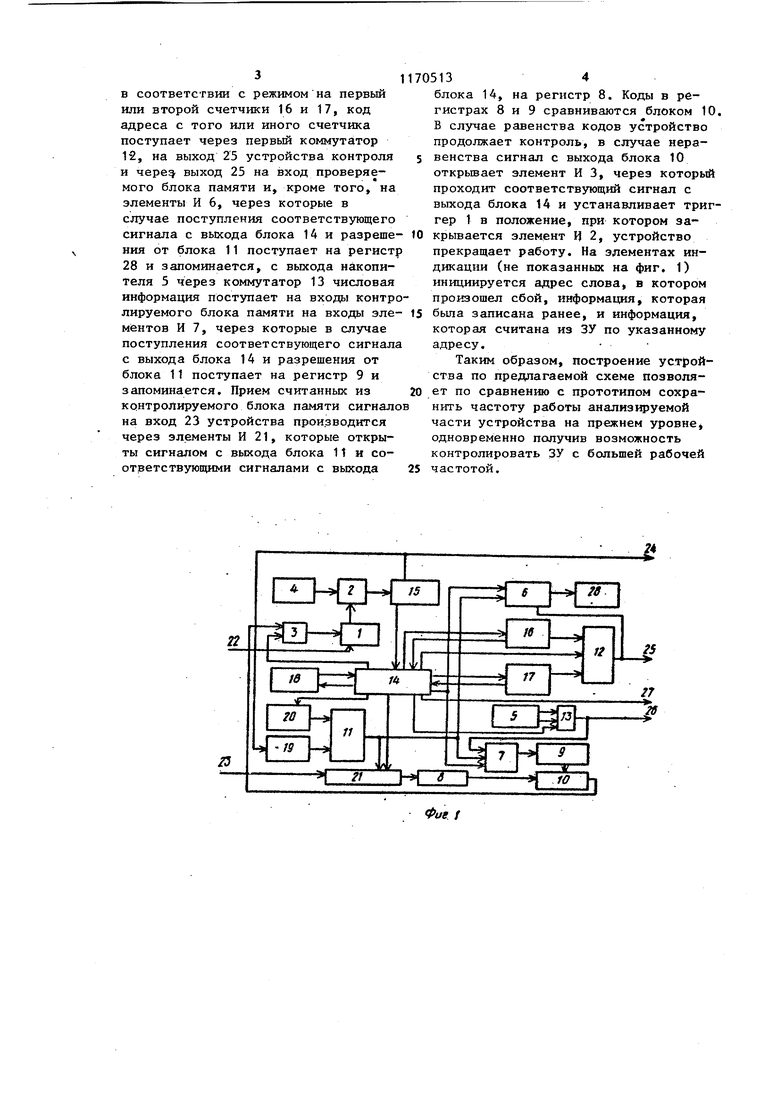

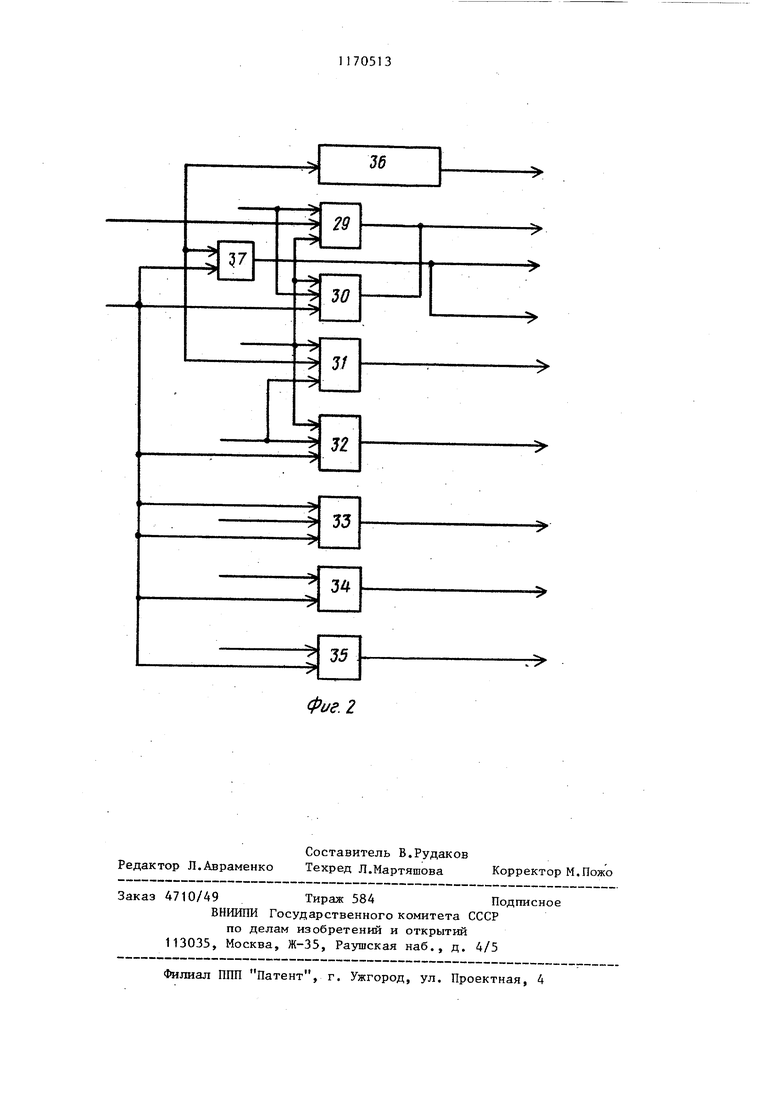

Изобретение относится к вычислительной технике, в частности к устройствам для контроля работы запоминающих устройств,и может быть исполь зовано в качестве технологического оборудования при производстве оперативных запоминающих устройств. Целью изобретения является повыше ние быстродействия устройства. На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - один из возможных вариантов вьтолнения блока управления. Устройство для контроля полупроводниковой памяти (фиг.1) содержит триггер 1, первый элемент И 2, второ элемент ИЗ, генератор 4 импульсов, накопитель 5, первую 6 и вторую 7 группы элементов И, первый 8 и второй 9 регистры числа, первый 10 и второй 1 Т блоки сравнения, первый 12 и второй 13 коммутаторы, блок 14 управления, формирователь 15 сигнало первый 16 и второй 17 счетчики, служащие для подсчета числа адресов, третий счетчик 18, служащий для подсчета числа этапов, четвертый 19 и пятый 20 счетчики, служащие для подсчета соответственно числа обращений и числа циклов, третью группу элемен тов И 21. Устройство имеет входы 22 и 23 и выходы 24-27. Устройство такж содержит регистр 28 адреса. Блок 14 управления (фиг.2) содержит элементы И 29-35, формирователь 36 сигналов и элемент ИЛИ 37, Условимся далее понимать следующи образом термины: режим - некоторая последовательность обращений к контролируемому ЗУ для записи или считывания с формированием заданной контрольной последовательности и определенным порядком перебора адресов, например, Попарное считывание, Попарная запись-считывание ; исходный контрольный код - некоторьй произвольный набор 1 и О с числом разрядов, равным числу разрядов проверяемого ЗУ, которьй служит исходным одом при формировании заданной онтрольной последовательности режиа; этапы - наборы однотипных опеаций, на которые может быть разбит екоторый режим проверки. Так, наример, режим Запись-считывание остоит из двух эталов: запись неоторой контрольной йоследовательости во все адреса контролируемого ассива слов и считьгоание записаной ранее информации со сравнением той же контрольной последовательостью. Рассмотрим теперь работу устройтва. Выбор контрольного режима, исходного контрольного кода, области контролируемых адресов задаётся набором соответствующего начального состояния счетчика 18, начального контрольного кода и кода, задающего массив контролируемого слова. После установки начального состояния (цепи установки начального состояния на фиг. 1 не показаны), в счетчик 18, в накопитель 5 и регистры 14 и 17 вводятся вышеуказанные коды, триггер 1, счетчики 20 и 19 устанавливаются в начальное состояние. После пуска устройства (подача управляющего сигнала на вход 26) триггер 1 устанавливается в положение, при котором открьюается элемент И 2, импульсы с генератора 4 начинают поступать на формирователь 14, на котором формируется набор сигналов с заданной длительностью и временным расположением. Сформиро- ванньй набор импульсов поступает на блок 14 управления, на выходах которого формируются все необходимые для работы устройства контроля сигналы и управляющие сигналы для контролируемого блока памяти Импульс обращения на контролируемьй блок памяти поступает непосредственно с формирователя 15. Импульсы счета адреса с блока 14 поступают в соответствии с режимом на первый или второй счетчики 16 и 17, код адреса с того или иного счетчика поступает через первый коммутатор 12, на выход 25 устройства контроля и чере выход 25 на вход проверяемого блока памяти и, кроме того, на элементы И 6, через которые в случае поступления соответствующего сигнала с выхода блока 14 и разреше ния от блока 11 поступает на регист 28 и запоминается, с выхода накопителя 5 через коммутатор 13 числовая информация поступает на входы контр лируемого блока памяти на входы зле ментов И 7, через которые в случае поступления соответствующего сигнал с выхода блока 14 и разрешения от блока 11 поступает на регистр 9 и запоминается. Прием считанных из контролируемого блока памяти сигнал на вход 23 устройства производится через элементы И 21, которые открыты сигналом с вькода блока 11 и соответствующими сигналами с выхода 134 блока 14, на регистр 8. Коды в регистрах 8 и 9 сравниваются блоком 10, В случае равенства кодов устройство продолжает контроль, в случае неравенства сигнал с выхода блока 10 открьшает элемент ИЗ, через который проходит соответствующий сигнал с выхода блока 14 и устанавливает триггер 1 в положение, при котором закрьшается элемент И 2, устройство прекращает работу. На элементах индикации (не показанных на фиг. 1) инициируется адрес слова, в котором произошел сбой, информация, которая была записана ранее, и информация, которая считана из ЗУ по указанному адресу. Таким образом, построение устройства по предлагаемой схеме позволяет по сравнению с прототипом сохранить частоту работы анализируемой части устройства на прежнем уровне одновременно получив возможность контролировать ЗУ с большей рабочей частотой.

Фие.2

| Патент США № 3631229, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Устройство для контроля памяти | 1977 |

|

SU739658A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-07-30—Публикация

1984-02-28—Подача