(54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

1

Изобретение относится к вычислительной технике/ в частности к ариф.метйческим устройствам, и может быть использовано в процессорах универсальных ЭВМ.5

Известны арифметические устройства однооперандного типа, содержащие регистры, сумматоры, сдвигаемые узлы Г1 и C2J .

Известные устройства позволяют tO выполнять широкий набор ари етических операций нал двоичными операндами с фиксированной и плавеиосцей запятой и логических операций.

Недостатком известных устройств 15 является невысокое быстродействие при выполнении команд неэквивалентности, вычитания операндов с фиксированной запятой, сложения и вычитания операндов с плавающей запя- 20 той, в случаях когда первым и вторым операндами является одно я то же число. Это объясняется тем, что перечисленные команды выполняются в известнЕЛх устройствах как обыч- 25 ные двухоперандные команды.

Наиболее близким по технической сущности к предложенному является арифметическое устройство .3, содержащее блок местной Пс1мяти, коммута- 30

тор, регистры первого и второго операндов, сдвигатель, сумматор, регистр результата, регистр кода операции, регистры адреса первого и второго операндов, формирователь адреса. Выход блока местной памяти .соединен с первым входом коммутатора, первый и второй выходы коммутатора соединены со входами регистров первого и второго операндов, выход регистра первого операнда соединен со вхоДом сдвигателя, выход сдвнгатёля соединен с первым входом сумматора, выход регистра второго операнда соединен со вторьм входом сумматора, выход сукматора соединен со входом регистра результата, выход регистра результата соединен со входом блока местной памяти и со вторым входом колл утатора, входы регистров кода операции, адресов первого и второго операндов соединены с выходом блока оперативной Пс1мяти, выходы этих регистров соединены соответственно с тремя входами формирователя адреса, выход формирователя адреса соединен с адресным входом блока местной памяти.

Разрядность основных узлов устройства позволяет выполнять операции

над операндами с фиксированной запятой (ФЗ) и длиной в 32 двоичных разряда и над операндами с плавающей запятой (ПЗ) с длиной характеристики - в 7 двоичных разрядов и длиной мантиссы - 56 двоичных разрядов (14 шестнадцатиричных цифр).

Рассмотрим работу устройства прототипа при выполнении команд неэквивалентности, сложения, вычита,ния операндов с фиксированной запятой и сложения, вычитания операндов с плавающей запятой.

а) Команда неэквивалентности выполняется следующим образом:

Сначала из блока оперативной памяти (оп) в регистры кода операции и адреса первого и второго операндов принимаются код команды неэквивалентности и адреса фегистров общего назначения (РОН), в-которых хранятся операнды. Затем первый операнд читается из блока местной памяти (мп) и через коммутатор передается в регистр первого операнда, далее второй операнд читается из блока МП и через коммуттор передается в регистр второго опранда. После этого первый операнд из соответствующего регистра через сдвигатель, но без сдвига принимает ся на первый вход сумматора, а второй операнд из соответствующего регистра принимается на второй вход .сумматора. В команде неэквивалентности на обоих входах сумматора включаются цепи прямой передачи. На сумматоре выполняется операция неэквивалентности (сложения по модулю два). Затем результат вычислений из сумматора принимается на регистр результата. Откуда в следующий момент времени записывается в блок МП по заданному в регистре адреса первого операнда адресу РОН.

б)Команды сложения, вычитания с ФЗ выполняются аналогично, но на втром входе сумматора включается цепь инверсной передачи (в случае команды вычитания), а в сумматоре вместо неэквивалентности производится суммирование.

в)В случае команд сложения и вычитания с ПЗ перед обработкой мантидс производятся действия над порядками: сначала из регистра с плавающей запятой (РПЗ), адрес которого определяется содержимым регистра адреса первого операнда, считывается первый операнд, но в регистр первого операнда через коммутатор принимается только порядок операнда (разряды знака мантиссы и мантиссы обнуляются). Затем в регистр второго операнда принимается из соответствующего РПЗ порядок второго операнда. На сумматоре вычисляется разность порядков операндов, котора подается на управляющий вход .сдвигателя. Если разность порядков мень ше нуля, то в РПЗ по адресу первого операнда записывается порядок второго операнда, который в этом случае , является порядком результата. .

5 После этого производятся следующие действия над мантиссами.

Из РПЗ (адрес которого сформирован в зависимости от содержимого регистров кода операции, адреса перQ вого и второго операндов) читается мантисса (разряды порядка обнулены) операнда с меньшим порядком и через коммутатор принимается на регистр первого операнда. Затем из РПЗ читается мантисса операнда с большим порядком -и через коммутатор принимается на регистр второго операнда. После этого мантисса из регистра первого операнда поступает на сдвигатель, где сдвигается вправо на количество тетрад, равное величине разности порядков, а затем принимается на первый вход сумматора. Включаются цепи прямой передачи. Мантисса из регистра второго операнда принимается на второй вход сумматора.

При сложении с ПЗ включаются цепи прямой передачи, при вычитании с ПЗ - цепи инверсной передачи. На сумматоре выполняется суммирование

JJ мантисс и, в следующий момент времени, результат вычислений из сумматора принимается на регистр результата, откуда затем записывается в блок МП, в РПЗ по адресу первого

с операнда.

Недостатком данного устройства также является невысокое быстродействие при выполнении команд неэквивалентности, вычитания операндов ФЗ и сложения, вычитания операндов с

0 ПЗ при равенстве адресов первого и второго операндов, так как эти команды выполняются как обычные двухоперандные команды.

Цель изобретения - повышение

5 быстродействия арифметического устройства.

Поставленная цель достигается тем, что в устройство, содержащее блок местно.й памяти, коммутатор, pen гистры первого и второго операндов/ сдвигатель, сумматор, регистр результата, регистр кода операции, регистры адреса первого и второго операндов, формирователь адреса, причем выход блока местной памяти соединен с первым входом коммутатора, первый и второй выходы коммутатора соединены со входами регистров первого и второго операндов соответственно, выход регистра первого операнда соединен со входом сдвигателя, выход сдвигателя соединен с первым входом сумматора, выход регистра второго операнда соединен со вторым входом сумматора, выход сумматора соединен со входом регистра результата, выход регистра результата соединен со входом блока местной памяти и со вторым входом коммутатора, входы регистров кода операции и адреса первого и. второго операндов соединены со входами устройства, первый выход регистра кода операции, выходы регистров адреса первого и второго операндов соединены соответственно с тремя входами формирователя адреса, выход формирователя адреса соединен с адресным входом блока местной памяти, введен анализатор равенства адресов, первый и второй информационные входы которого соединены с выходами регистров адреса первого и второго операндов соответственно, первьзй управляющий вход анализатора сбединен со вторым выходом регистра кода операции, второй управляющий вход анализатора соединен с третьим выходом регистра кода операции, первый выход соединен с управляющим входом сдвигателя, а второй выход - с управляющим входом регистра результата.

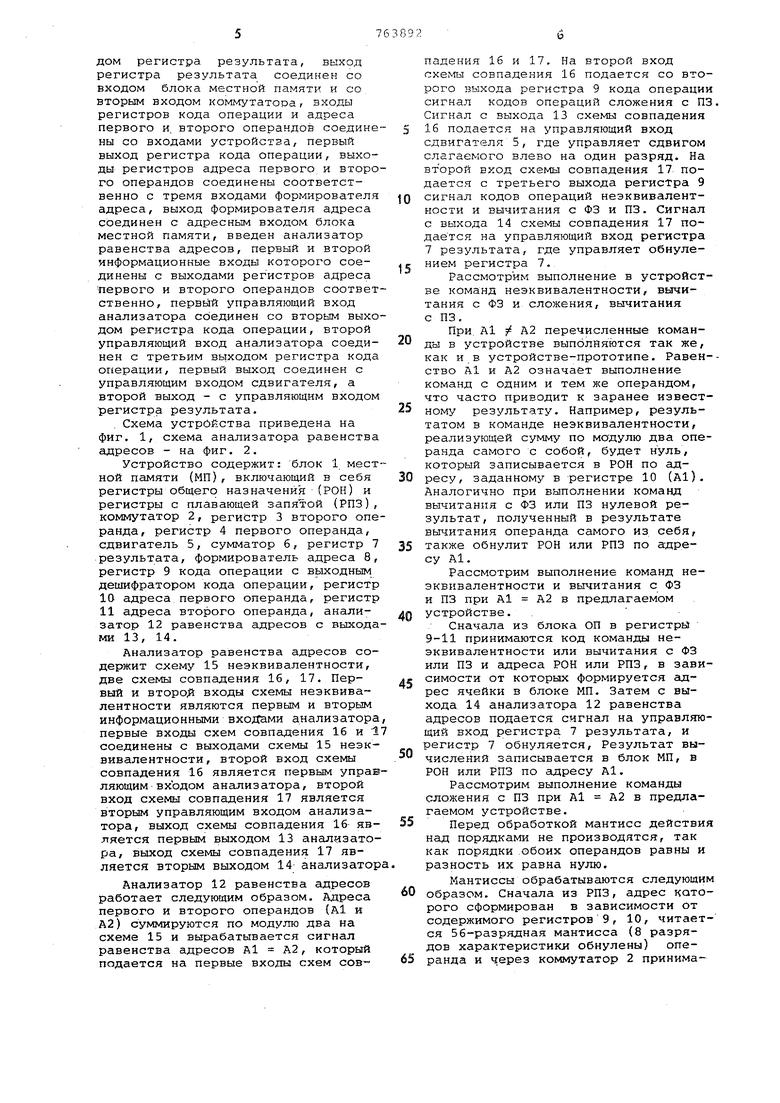

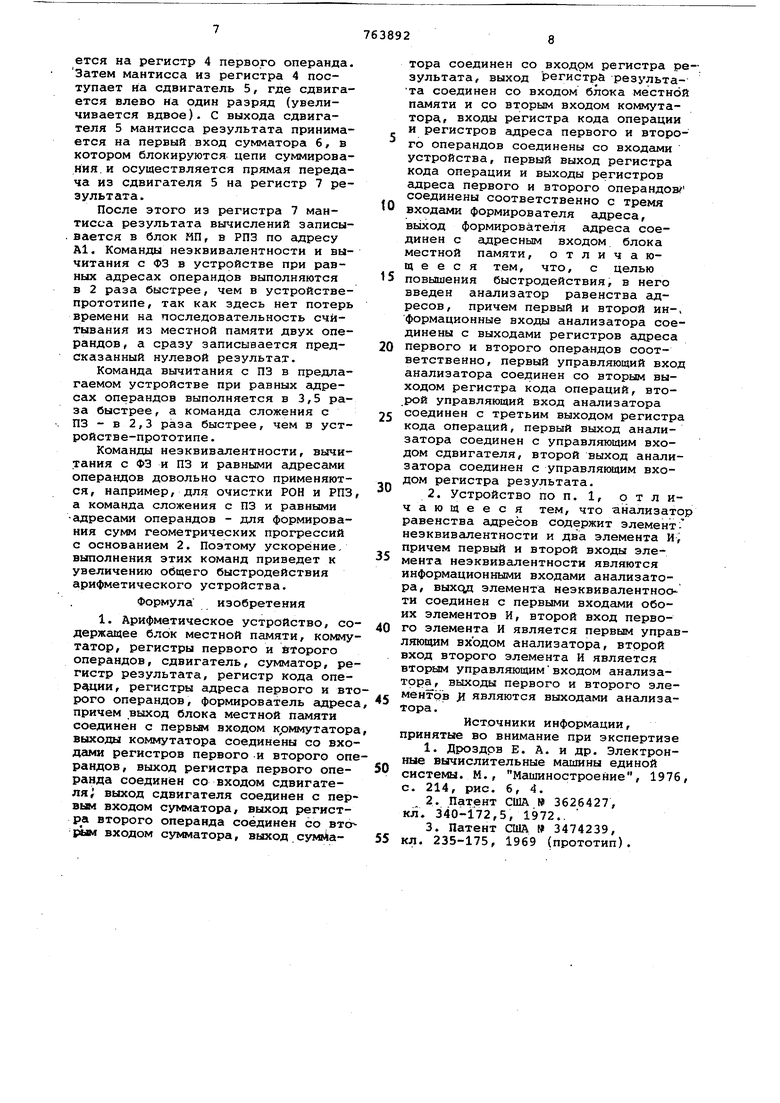

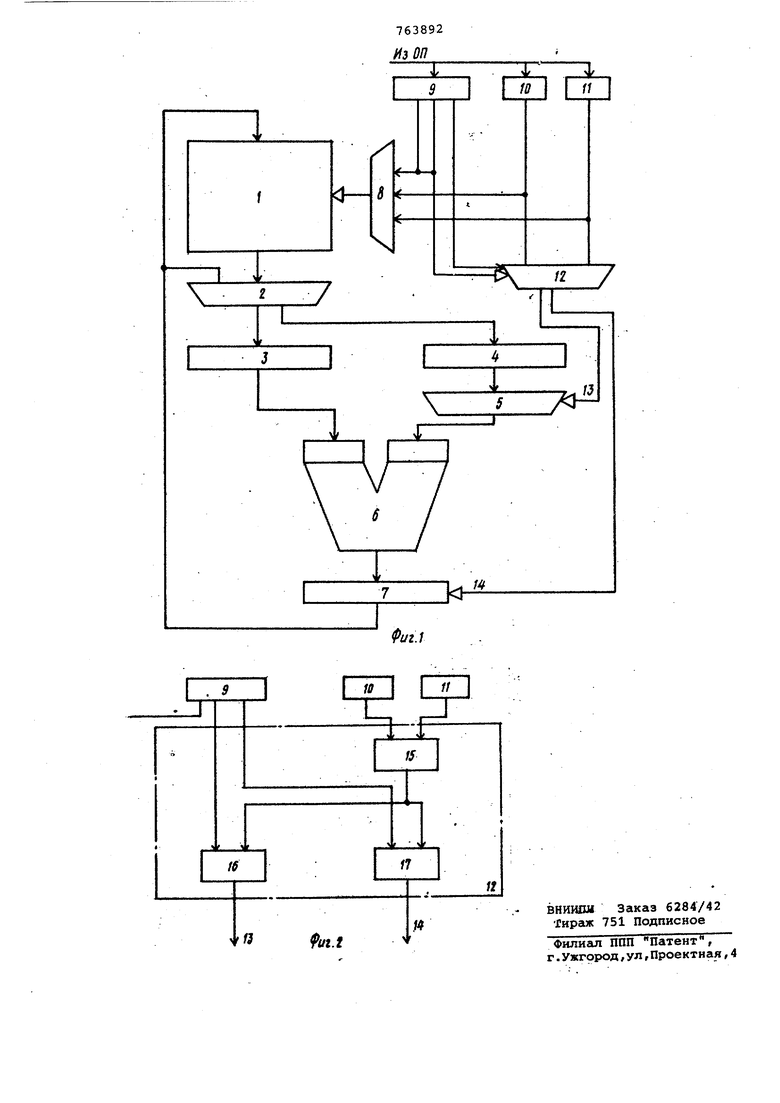

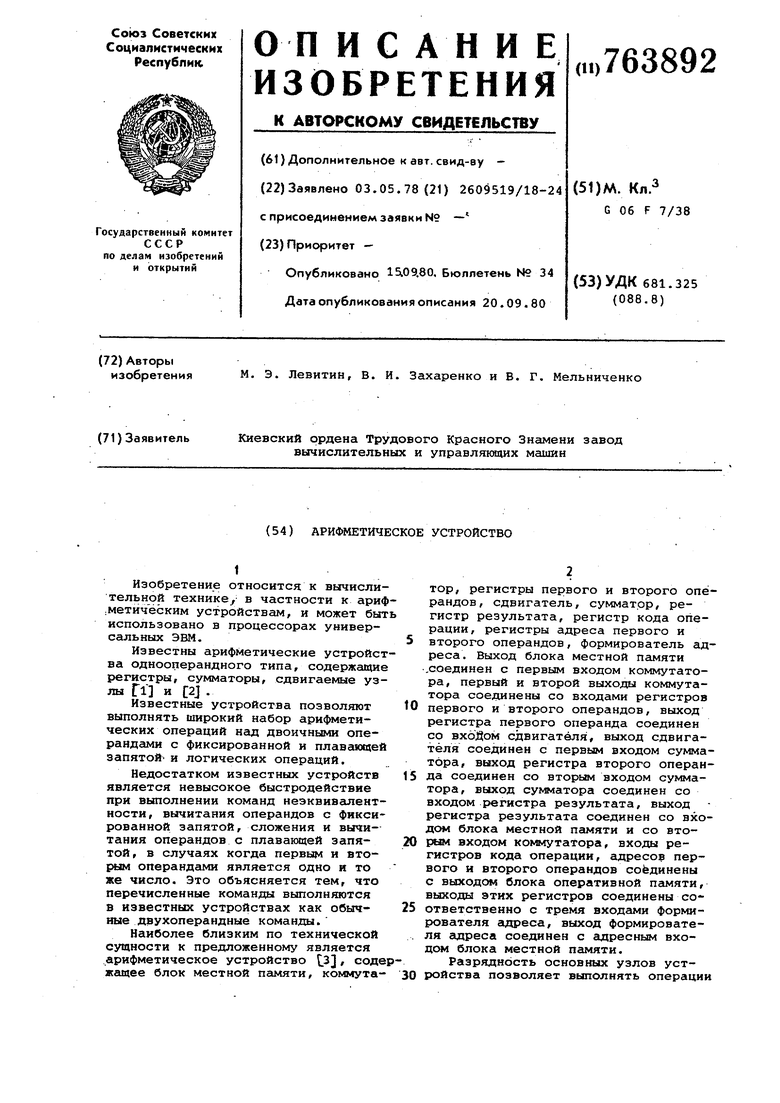

. Схема устройства приведена на фиг. 1, схема анализатора равенства адресов - на фиг. 2.

Устройство содержит: блок 1 местной памяти (МП), включающий в себя регистры общего назначения (РОН) и регистры с плавающей запятой (РПЗ), коммутатор 2, регистр 3 второго операнда, регистр 4 первого операнда, сдвигатель 5, сумматор 6, регистр 7 результата, формирователь адреса 8, регистр 9 кода операции с вь1ходным дешифратором кода операции, регистр

10адреса первого операнда, регистр

11адреса второго операнда, анализатор 12 равенства адресов с выходами 13,14.

Анализатор равенства адресов содержит схему 15 неэквивалентности, две схемы совпадения 16, 17. Первый и второЯ входы схемы неэквивалентности являются первым и вторым информационными входами анализатора первые входы схем совпадения 16 и 1 соединены с выходами схемы 15 неэквивалентности, второй вход схемы совпадения 16 является первым управляющим входом анализатора, второй вход схемы совпадения 17 является вторым управляющим входом анализатора, выход схемы совпадения 16- является первым выходом 13 анализатора, выход схемы совпадения 17 является вторым выходом 14 анализатор

Анализатор 12 равенства адресов работает следующим образом. Адреса первого и второго операндов (А и А2) суммируются по модулю два на схеме 15 и вырабатывается сигнал равенства адресов Al А2, который подается на первые входы схем совпадения 16 и 17. На второй вход схемы совпадения 16 подается со второго выхода регистра 9 кода операции сигнал кодов операций сложения с ПЗ. Сигнал с выхода 13 схемы совпадения 16 подается на управляющий вход сдвигателя 5, где управляет сдвигом слагаемого влево на один разряд. На второй вход схемы совпадения 17 подается с третьего выхода регистра 9 сигнал кодов операций неэквивалент0ности и вычитания с ФЗ и ПЗ. Сигнал с выхода 14 схемы совпадения 17 подается на управляющий вход регистра 7 результата, где управляет обнулением регистра 7.

5

Рассмотрим выполнение в устройстве команд неэквивалентности, вычитания с ФЗ и сложения, выгчитания с ПЗ.

При А1 5 А2 перечисленные коман0ды в устройстве выполняются так же/ как ив устройстве-прототипе. Равен-ство Al и А2 означает выполнение команд с одним и тем же операндом, что часто приводит к заранее извест5ному результату. Например, результатом в команде неэквивалентности, реализующей сумму по модулю два операнда самого с собой, будет нуль, который записывается в РОН по ад0ресу, заданному в регистре 10 (Al). Аналогично при выполнении команд вычитания с ФЗ или ПЗ нулевой результат, полученный в результате вычитания операнда самого из себя,

5 также обнулит РОН или РПЗ по адресу Al.

Рассмотрим выполнение команд неэквивалентности и вычитания с ФЗ и ПЗ при Al А2 в предлагаемом устройстве.

0

Сначала из блока СП в регистрй 9-11 принимаются код команды неэквивалентности или вычитания с ФЗ или ПЗ и адреса РОН или РПЗ, в зависимости от которых формируется ад5рес ячейки в блоке МП. Затем с выхода 14 анализатора 12 равенства адресов подается сигнал на управляющий вход регистра 7 результата, и регистр 7 обнуляется. Результат вы0числений записывается в блок МП, в РОН или РПЗ по адресу Al.

Рассмотрим выполнение команды сложения с ПЗ при Al А2 в предлагаемом устройстве.

5

Перед обработкой мантисс действия над порядками не производятся, так как порядки обоих операндов равны и разность их равна нулю.

Мантиссы обрабатывгиотся следующим

0 образом. Сначала из РПЗ, адрес которого сформирован в зависимости от содержимого регистров 9, 10, читается 56-разрядная мантисса (8 разрядов характеристики обнулены) опе5ранда и через коммутатор 2 принимается на регистр 4 первого операнда. Затем мантисса из регистра 4 поступает иа сдвигатель 5, где сдвигается влево ка один разряд (увеличивается вдвое). С выхода сдвигателя 5 мантисса результата принимается на первый вход сумматора 6, в котором блокируются цепи суммирования, и осуществляется прямая передача из сдвигателя 5 на регистр 7 результата.

После этого из регистра 7 мантисса результата вычислений записывается в блок НП, в РПЗ по адресу А1. Команды неэквивалентности и вычитания с ФЗ в устройстве при равных адресах операндов выполняются в 2 раза быстрее, чем в устройствепрототипе , так как здесь нет потерь времени на последовательность считывания из местной памяти двух операндов, а сразу записывается предсказанный нулевой результат.

Команда вычитания с ПЗ в предлагаемом устройстве при равных адресах операндов выполняется в 3,5 раза быстрее, а команда сложения с ПЗ - в 2,3 раза быстрее, чем в устройстве-прототипе .

Команды неэквивалентности, вычитания с ФЗ и ПЗ и равными адресами операндов довольно часто применяются, например, для очистки РОН и РПЗ, а команда сложения с ПЗ и равными ёщресами операндов - для формирования сумм геометрических прогрессий с основанием 2. Поэтому ускорение, выполнения этих команд приведет к увеличению общего быстродействия арифметического устройства.

Формула изобретения

1. Арифметическое устройство, содержащее блок местной памяти, коммутатор, регистры первого и второго операндов, сдвигатель, сумматор, регистр результата, регистр кода опер хии, регистры адреса первого и второго операндов, формирователь адреса причем выход блока местной памяти соединен с первьаи входом крммутатора выходы коммутатора соединены со входами регистров первого и второго операндов, выход регистра первого операнда соедин ен со входом сдвигателя; выход сдвигателя соединен с пер вьвл входом сумматора, выход регистр а второго операнда соединен со вто piw входом сумматора, выход сумйатора соединен со входом регистра результата, выход регистра результата соединен со входом блока местной памяти и со вторым входом коммутатора, входы регистра кода операции и регистров адреса первого и второго операндов соединены со входами устройства, первый выход регистра кода операции и выходы регистров адреса первого и второго операндов соединены соответственно с тремя входами формирователя адреса, вь1ход формирователя адреса соединен с адресным входом блока местной памяти, отличающееся тем, что, с целью повышения быстродействия, в него введен анализатор равенства адресов, причем первый и второй ин-, формационные входы анализатора соединены с выходами регистров адреса первого и второго операндов соответственно, первый управляющий вход анализатора соединен со вторым выходом регистра кода операций, второй управляющий вход анализатора соединен с третьим выходом регистра кода операций, первый выход анализатора соединен с управляющим входом сдвигателя, второй выход анализатора соединен с управляющим входом регистра результата.

2. Устройство по п. 1, отличающееся тем, что анализато равенства адресов содержит элемент: неэквивалентности и два элемента И, причем первый и второй входы элемента неэквивалентности являются информационными входами анализатора, выход элемента неэквивалентное ти соединен с первыми входами обоих элементов И, второй вход первого элемента И является первым управляющим входом анализатора, второй вход второго элемента И является вторым управляющимвходом анализатора, выходы первого и второго элементов Л являются выходами анализатора.

Источники информации, принятые во внимание при экспертизе

1.Дроздов Е. А. и др. Электронные вычислительные машины единой системы. М., Машиностроение, 1976 с. 214, рис. 6, 4.

2.Патент США 3626427, кл. 340-172,5, 1972..

3.Патент США 3474239, кл. 235-175, 1969 (прототип).

763892

flaOn

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство | 1978 |

|

SU809169A1 |

| Арифметическое устройство | 1984 |

|

SU1193661A1 |

| Устройство для сложения (I) | 1989 |

|

SU1837281A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

Ll

TTTI

//

Авторы

Даты

1980-09-15—Публикация

1978-05-03—Подача