Изобретение относится к вычислительной технике и может быть использовано при

про

ктировании арифметических устройств

высркой производительности.

Цель изобретения - повышение быстродействия.

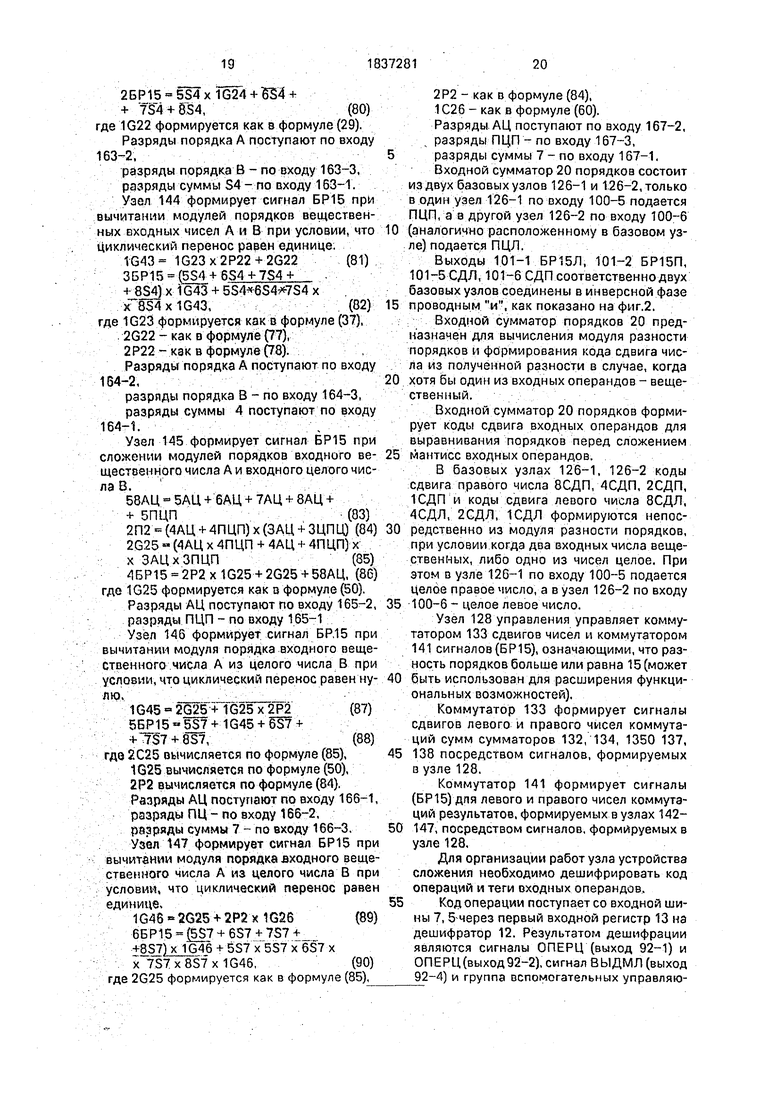

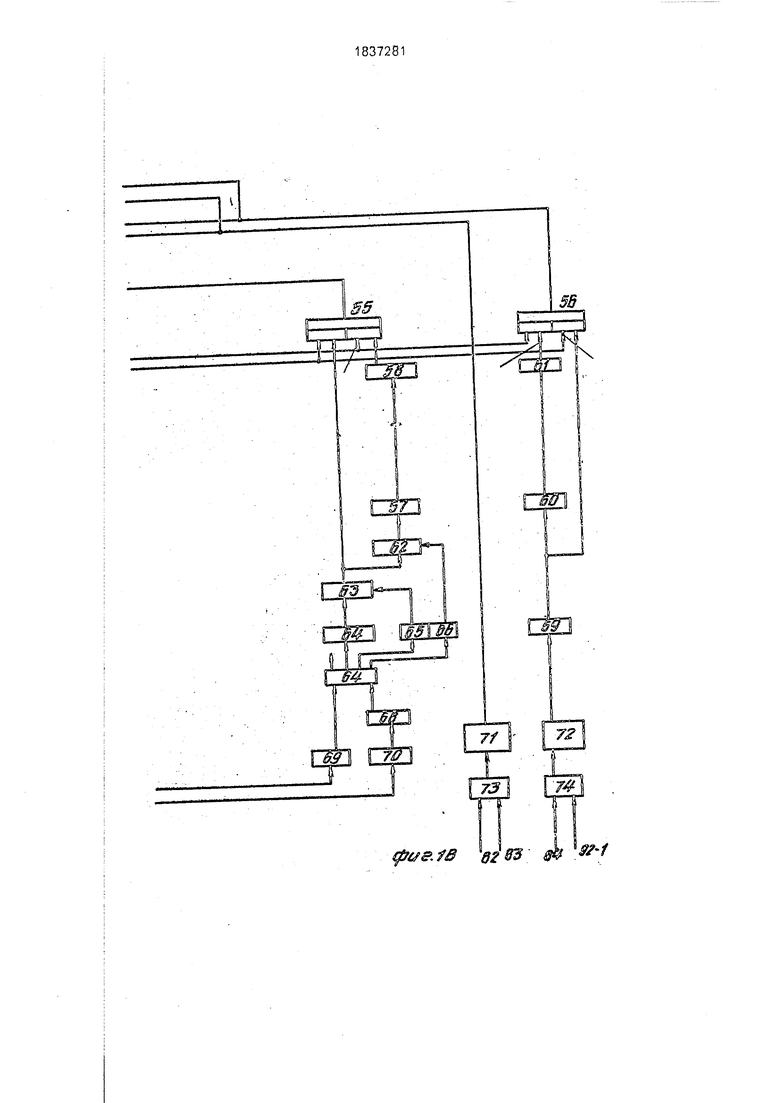

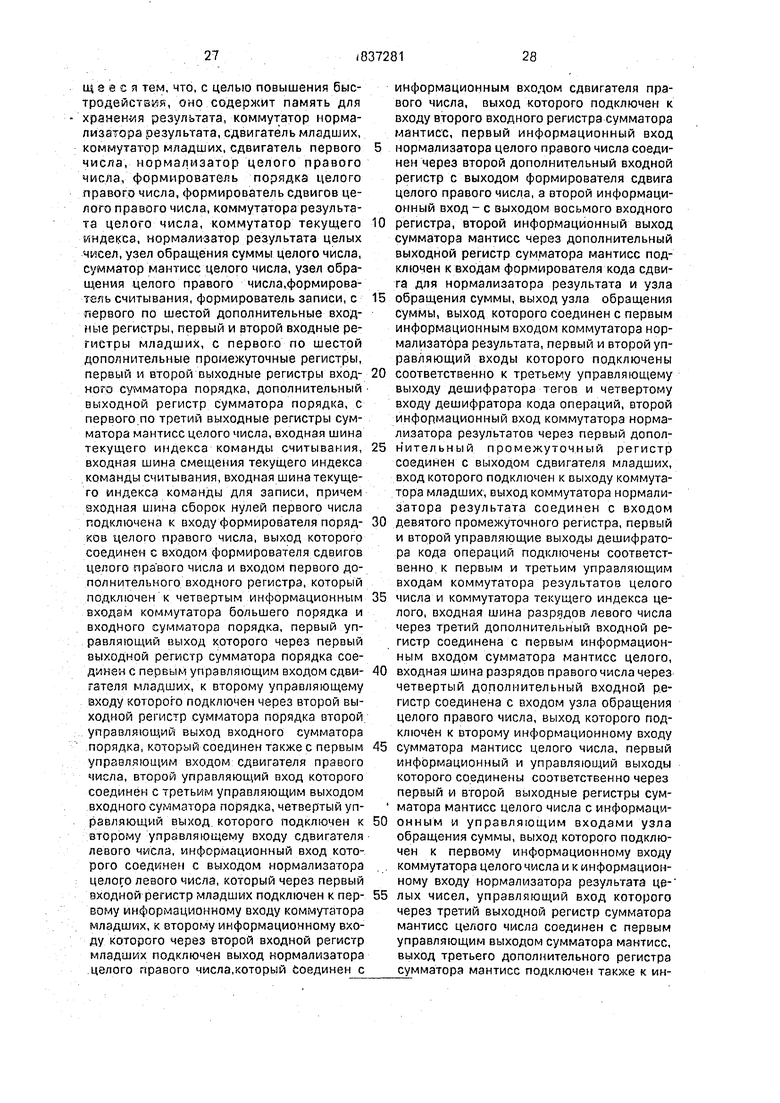

На фиг.1а-в представлена функцио- эная схема устройства для сложения; на

нал фиг

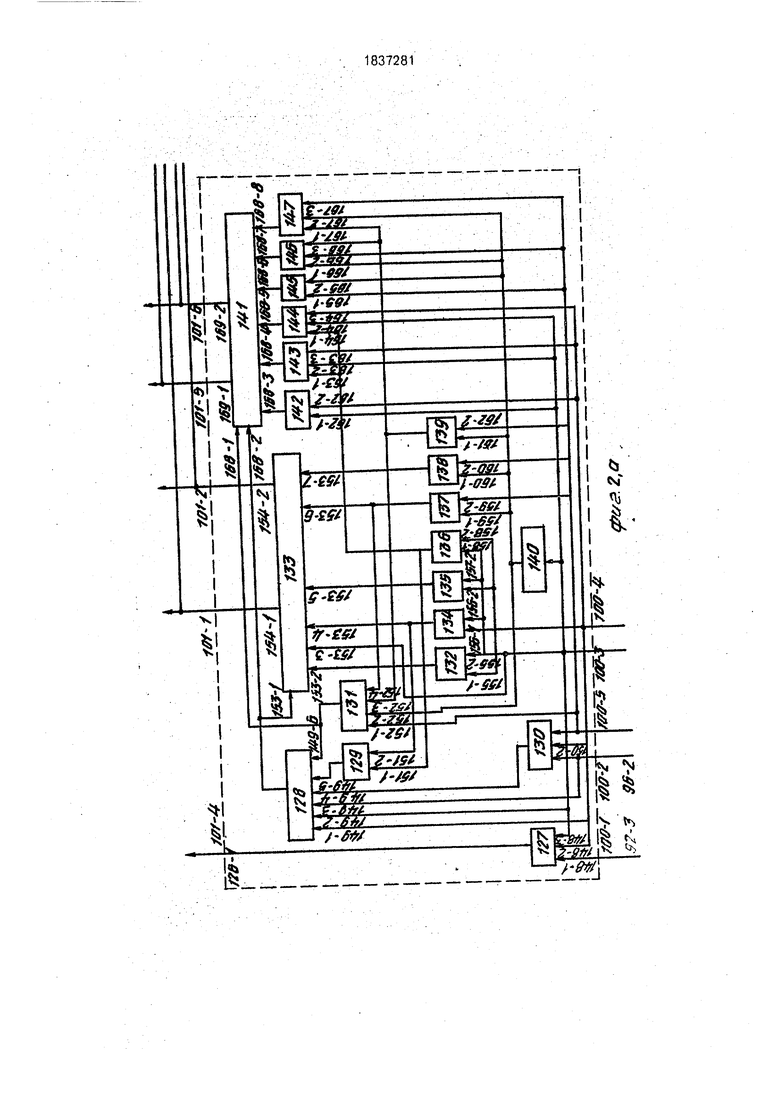

2а и 26 - функциональная электричеСКЭ5 схема входного сумматора порядТса; на

фиг

3 - схема узла управления.

|Устройство сложения содержит память

1для хранения тега результата, коммутатор

2те -а результата, выходной сумматор 3 порядков, с первого по шестой промежуточные регистры 4-9, первый и второй выходные регистры 10, 11 входного сумматора порядка, дешифратор 12 кода операций, первый и второй входные регистры 13, 14, дешифратор 15 тега, третий входной ре- гистэ 16; коммутатор 17 порядка большего, четвертый, пятый входные регистры 18, 19, входной .сумматор 20 порядков, шестой

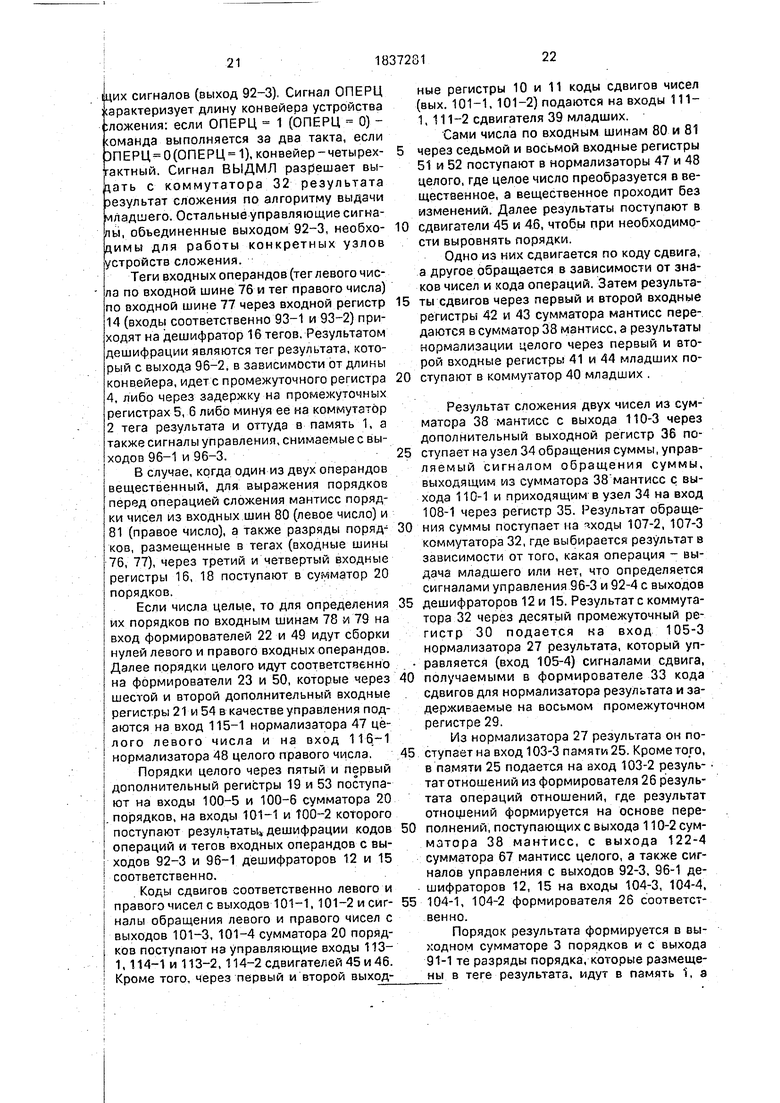

входной регистр 21, формирователь 22 порядка целого левого числа, формирователь 23 сдвигов целого левого числа, формирователь 24 номера прерываний, память 25 для хранения результата, формирователь 26 результата операций отношений, нормализатор 27 результата, седьмой, восьмой и девятый промежуточные регистры 28, 29, 30, формирователь 31 порядка коррекции, коммутатор 32 нормализатора результата, формирователь 33 кода сдвига для нормализатора результата, узел 34 обращения суммы, выходной и дополнительный выходной регистры 35, 36 сумматора мантисс, первый дополнительный промежуточный регистр 37, сумматор 38 мантисс, сдвигатель 39 младших, коммутатор 40 младших, первый входной регистр 41 младших, первый и второй входные регистры 42, 43 сумматора мантисс, второй входной регистр 44 младших, .сдвигатель 45 левого числа, сдвигатель 46 правого числа, нормализатор 47 целого левого числа, нормализатор 4.8 целого праW

00

СА)

М

Ю

00

вого числа, формирователь 49 порядка целого правого числа, формирователь 50 сдвигов целого правого числа, седьмой и восьмой входные регистры .51, 52, первый и второй дополнительные входные регистры 53, 54, коммутатор 55 результата целого числа, коммутатор 56 текущего индекса команды, со второго по шестой дополнительные регистры 57-61, нормализатор 62 результата целых чисел, узел 63 обращения суммы целого числа, первый, второй и третий выходные регистры 64, 65, 66 сумматора мантисс целого числа, сумматор 67 мантисс целого числа, узел 68 обращения целого правого числа, с третьего по шестой дополнительные входные регистры 69-72. формирователь 73 адреса считывания, формирователь 74 адреса записи, входные шины: шину 75 кода операций, шину 76 тега левого числа, шину 77 тега правого числа, шину 78 разрядов левого числа, шину 79 разрядов правого числа, шину 80 сборок нулей левого числа, шину 81 сборок нулей правого числа, шину В2 текущего индекса команд считывания, шину 83 смещения текущего индекса команды считывания, шину 84 текущего индекса команд записи, выходную шину 85 тега результата, выходную шину 86 номера прерываний, выходную шину 87 разрядов результатов,

Память 1 для хранения тега результата имеет первый и второй информационные входы 88-1, 88-2, первый и второй адресные входы 88-3, 88-4.

Коммутатор 2 тега результата - первый управляющий и первый информационный входы 89-1, 89-2, второй управлякщий и второй информационные входы 89-3, 89-4,

Выходные сумматор 3 порядков - пер- йый и второй управляющие входы 90-1, 90- 2, первый и второй информационные входы 90-3, 90-4, информационный выход 91-1, управляющий выход 91-2,

Дешифратор 12 кода операций - первый, второй, третий и четвертый управляю- . щие выходы 92-1, 92-2, 92-3, 92-4.

Второй входной регистр 14 - первый и второй информационные входы - 93-1, 93- 2, первый и второй информационные выходы - 94-1, 94-2.

Дешифратор 15 тегов - первый и второй информационные входы 95-1, 95-2, первый, второй и третий управляющие выходы 96-1,96-2,96-3.

Третий входной регистр 16 - первый и второй информационные входы 97-1, 97-2.

Коммутатор 17 большего порядка - первый, второй, третий и четвертый информационные входы 98-1, 98-2, 98-3, 98-4.

Четвертый входной регистр 18 - первый и второй информационные входы 99-1,99-2.

Входной сумматор 20 порядков - первый и второй управляющие входы 100-1, 100-2, первый, второй, третий/четвертый информационные входы 100-3, 100-4, 100- 5,100-6, первый, второй, третий, четвертый, пятый, шестой управляющие выходы 101-1, 101-2, 101-3, 101-4. 101-5, 101-6.

Формирователь 24 номера прерываний - первый, второй, третий управляющие входы 102-1, 102-2, 102-3.

Память 25 для хранения результата управляющий вход 103-1, первый, второй,

третий информационные входы 103-2, 1033, 103-4, первый и второй адресные входы

103-5,103-6.

Формирователь 26 результата операций отношения - первый и второй управляющие входы 104-1, 104-20 первый и второй информационные входы 104-3, 104-4, Нормализатор 27 результата-первый и второй управляющий входы 105-1, 105-2, первый и второй информационные входы 105-3, 105-4.

Формирователь 31 порядка коррекции - первый и второй управляющие входы 106-1, 106-2, информационный вход 106-3.

Коммутатор 32 нормализатора результата - первый информационный вход 107-1, первый и второй управляющие входы 107-2, 1Q7-3, второй информационный вход 107-4. Узел 34 обращения суммы - управляющий вход 108-1, информационный вход 108-2.

Сумматор 38 мантисс-первый и второй информационные входы 109-1, 109-2, управляющий выход 110-1, первый и второй информационные выходы 110-2, 110-3,

Сдвигатель 39 младших - первый и второй управляющие входы 111-1, 112-2, ин- формационный вход 111-3.

Коммутатор 40 младших-первый и второй информационные входы 112-1, 112-2.

Сдвигатель 45 левого числа - первый и второй управляющие входы 113-1, 113-2, информационный вход 113-3, третий управляющий вход 113-4.

Сдвигатель 46 правого числа - первый и второй управляющие входы 114-1, 114-2, информационный вход 114-3, третий управляющий вход 114-4.

Нормализатор целого левого числа - первый и второй информационные входы 115-1,115-2.

Нормализатор 48 целого правого числа - первый и второй информационные входы 116-1,116-2.

Коммутатор 55 результатов целого числа - первый управляющий вход 117-1, первый и второй информационные входы

11 11

-2, 117-3, второй управляющий вход -4.

Коммутатор 56 текущего индекса ко- майды - первый управляющий и первый инфоуп

вх4ды 118-3,118-4.

Нормализатор 62 результата целых чисел - информационный вход 119-1, управ- ляпщий вход 119-2,

Узел 63 обращения суммы - информаэмационный входы 118-1,118-2, второй авляющий и второй информационный

ци 12

пе 12

XOJ

вы ны

пе 12С

ма 124

нный вход 120-1, управляющий вход -2. . ,.

Сумматор 67 мантисс целого числа - вый и второй информационные входы 15 -1,121-2, первый информационный вы- т22-1, первый и второй управляющие оды 122-2,122-3, второй информацион- i выход 122-4.

Формирователь 76адреса считывания - 20 вый и второй информационные входы -1.123-2.

Третий выходной регистр 66 сумматора тисе целого числа - управляющий выход

25

Формирователь 74 адреса записи - пер- вы и второй информационные входы 125- 1, 25-2.

Входная шина 75 кода операций.через пер вый входной регистр 13 соединена с вхо- 30 догО дешифратора 12 кода операций, первый и второй управляющие выходы 92-1 и 92-2 которого подключены соответственно

;рвым и вторым управляющим входам

1.117-1,118-1 и89-1,117-3,118-3ком- 35

к п 89-J

мутатора 2 тега операций, коммутатора 55 результатов целого числа, коммутатора 56 текущего индекса команд, третий управля- ющ 1й выход 92-3 дешифратора 12 кода операций соединен с первыми входами 90-1. 40 100-1,102-1,104-1, 105-1, t06-1 выходного с умматора 3 порядков, входного, сумма- тора 20 порядков, формирователя 24 HOIY ера прерываний, формирователя 26 результата операций отношения, нормализа- 45 ора 27 результата, формирователя 31 порядка коррекции, четвертый управляющие выход 92-4 дешифратора 12 кода опе- рац 1й соединен со вторым управляющим XOJ (ом 107-4 коммутатора 32 нормализато- 50 pa f езультатов.

Входные шины 76, 77 тега левого и правок чисел соединены соответственное первым и вторым информационными входами

3-, 93-2 второго входного регистра 14, 55 пер; ый и второй информационные выходы

4-, 94-2 которого подключены к соответ- тв ющим входам 95-1, 95-2 дешифратора 15 тэгов, первый управляющий выход 96-1 коте рого соединен со вторыми управляю5

10

15

0

5

0

5

0 5 0

5

щими входами 90-2, 100-2, 102-2, 104-2, 105-2,106-2 выходного сумматора 3 порядков, входного сумматора 20 порядков, формирователя 24 номера прерываний, формирователя 26 результата операций отношений нормализатора 27 результата, формирователя 31 порядка коррекции, второй управляющий выход 96-2 дешифратора 15 тегов через первый промежуточный регистр 4 подключен к первому информационному входу 89-2 коммутатора 2 тега результата и входу второго промежуточного регистра 5, выход которого через третий промежуточный регистр 6 соединен со вторым информационным входом 89-4 коммутатора 2 тега результата.

Входные шины 76, 78 тега левого числа и разрядов числа подключены соответственно к первому и второму информационным входам 97-1, 97-2 третьего входного регистра 16.

Входные шины 77,79 тега правого числа и разряда правого числа подключены к первому числа подключены к первому и второму информационным входам 99-1, 99-2 соответственно четвертого входного регистра 18.

Входная шина 80 сборок нулей левого числа через формирователь 22 порядка целого левого числа соедингна со входом формирователя 23 сдвигов целого левого числа, выход которого подключен к входам пятого и шестого входных регистры 19, 21, выход шестого входного регистра 21 соединен с первым информационным входом 115-1 нормализатора 47 целого левого числа.

Входная шина 81 сборок нулевой правого числа через формирователь 49 порядка целого правого числа соединена с входом формирователя 50 сдвигов целого правого числа, выход которого подключен к входам первого и второго дополнительных входных регистров 53 и 54, выход второго дополнительного регистра 54 соединен с первым входом 116-1 нормализатора 48 целого правого числа.

Выходы третьего, четвертого, пятого входных регистров 16, 18, 19 и первого дополнительного входного регистр 53 соединены с первыми, вторыми, третьими, четвертыми информационными входами 98-1.98-2,98-3.98-4 и 100-3,100-4.100-5, 100-6 коммутатора 17 порядка большего и входного сумматора 20 порядка.

Выход коммутатора 17 порядка большего через последовательно соединенные четвертый, пятый и шестой промежуточные регистры 7, 8, 9 подключен к первому информационному входу 90-3 выходного сумматора 3 порядков.

Первый управляющий выход 101-1 входного сумматора 20 порядка соединен с первым управляющим входом 113-1 сдвигателя 45 левого числа, а через первый выходной регистр 10 сумматора порядка - с первым управляющим входом 111-1 сдвига- теля 39 младших, ко второму управляющему входу 111-2 которого подключен через второй выходной регистр.1.1 сумматора порядка второй управляющий выход 1Q1-2 входного сумматора 20 порядка, который соединен также с первым управляющим входом 114-1 сдвигатёля 46 правого числа, второй управляющий вход 114-2 которого соединен с третьим управляющим выходом 101-3 входного сумматора 20 порядка, четвертый управляющий выход 101-4 которого подключен ко второму управляющему входу 113-2 сдвигателя 45 левого числа.

Входная шина 78 разрядов левого числа и входная шина 79 разрядов правого числа подключены соответственно через седьмой и восьмой входные регистры 5.1 и 52 ко вторым информационным входам 115-2 и 116- 2 нормализаторов 47 и 48 целого левого и правого чисел, выход нормализатора 47 целого левого числа соединен с информационным входом 113-3 сдвигателя 45 левого Ч11сла и через первый входной регистр 41 младших с первым информационным входом 112-1 коммутатора 40 младших, выход нормализатора 48 целого правого числа соединен с информационным входом 114-3 сдзмгателя 46 правого числа и через второй входной регистр 44 младших со вторым информационным входом 112-2 коммутатора ; 40 младших,

Выходу сдвигателей 45 и 46 левого числа и правого числа соответственно через первый и агорой входные регистры 42, 43 сумматора мантисс соединены с первым и вторым информационными входами 109-1, 109-2 сумматора 38 мантисс, управляющий м второй информационный выходи 110-1, 110-3 которого соответственно через выходной и дополнительный выходной регистры 35, 36 подключены соответственно к управляющему и информационному входам 108-1,108-2 узла 34 обращения суммы, выход которого соединен с первым информационным входом 107-1 коммутатора 32 нормализатора результата.

Выход коммутатора 40 младших подключен к информационному входу 111-3 сдвигателя 39 младших..выход которого через первый дополнительный промежуточный регистр 37 соединен со вторым информационным еходом 107-4 коммутатора 32 нормализатора результата.

Выход дополнительного выходного регистра 36 сумматора мантисс также соединен со входом формирователя 33 кода сдвига для нормализатора результата, выход которого соединен с информационным входом 106-3 формирователя 31 порядка коррекции, выход которого через седьмой промежуточный регистр 28 подключен ко второму информационному входу 90-4 вы0 ходного сумматора 3 порядка.

Выход формирователя 33 кода сдвига для нормализатора результата кроме того соединен через восьмой промежуточный регистр 29 с первым информационным входом

5 105-3 и нормализатора 27 результата, ко второму информационному входу 105-4 которого через девятый промежуточный регистр 20 подключен выход коммутатора 32 нормализатора результата.

0 Входная шина 78 разрядов левого числа через третий дополнительный входной регистр 69 соединена с первым информационным зходом 121-1 сумматора.07 мантисс целого.

5 Входная шина 79 разрядов правого числа через четвертый дополнительный входной регистр 70 соединена с входом узла 68 обращения целого правого числа, выход которого подключен ко второму информаци0 онному входу 121-2 сумматора 67 мантисс целого числа,

Первый информационный и управляющий выходы 121-1, 122-2 сумматора 67 мантисс целого числа соединены соответ5 ственно через первый и второй выходные регистры 64, 65 сумматор мантисс целого числа с информационным и управляющими входами 120-1, 120-2 узла 63 обращения суммы целого числа, выход которого под0 ключей к первому информационному входу 117-2 коммутатора 55 целого числа и к информационному входу 119-1 нормализатора 62 результата целых чисел, управляющий вход 119-2 которого через третий выходной

5 регистр 66 сумматора мантисс целого числа соединен с первым управляющим выходом 122-3 сумматора 67 мантисс.

Выход нормализатора 62 результата целых чисел через последовательно соеди0 ненные второй и третий дополнительные

промежуточные регистры 57, 58 подключен

к второму информационному входу 117-3

коммутатора 55 результатов целого числа.

Входные шикы 82, 83 текущего индекса

5 команд считывания и смещения текущего индекса команды считывания подключены соответственно к первому и второму информационным входам 123-1, 123-2 формирователя 73 адреса считывания, выход которого через пятый дополнительный

вхсдной регистр 71 соединен с первыми адрес ными входами 88-3, 103-5 памяти 1 для хрг нения тега результата и памяти 25 хранения результата,

Входная шина 84 текущего индекса команд записи и первый управляющий выход 92т1 дешифратора 12 кода операций соединена соответственно с первым и вторым информационными входами 125-1, 125-2 фо )мирователя 74 адреса записи, выход ко- TOforo через последовательно соединенные шестой дополнительный входной регистр 72 1 четвертый, пятый, шестой дополнительны j промежуточные регистры 59, 60, 61 соединены с первым информационным вхсдом 118-2 коммутатора 56 текущего индекса команд, второй информационный вхсд которого 118-4 подключен к выходу четвертого промежуточного регистра 59.

Выход коммутатора 2 тега результата и иноормационный выход выходного сук матора 3 порядков соединены соответственно с первым и вторым, информационными входами 88-1, 88-2 памяти 1 для хрг нения тега результата, выход которого подключен к выходной шине 85 тега результата.

Управляющий выход 124 третьего выходного регистра 66 сумматора мантисс це ого числа соединен с третьим управляю щи и входом 102-3 формирователя 24 номера прерываний, выход которого подключен к вмходной шине 86 номера прерываний.

Второй информационный выход 122-4 tyiO матора мантисс соединен со вторым информационным входом 104-4 формирователя; 26 результата операций отношения, выход которого подключен к первому информационному входу 103-2 памяти 25 для хранения результата, ко второму информационному входу 103-3 которой подключен выход нормализатора 27 результата, к третьему информационному входу 103-4 - выход коммутатора 55 результата целого числа. Выход памяти 25 для хранения результата соединен с выходной шиной 87

раз

рядов результата.

Память 1 для хранения тега результата . и память 25 для хранения результата могут быть выполнены как двухпортовые памяти:

на

128 ячеек.

Формирователь 22 порядка целого левого числа и формирователь порядка целого

прг

вого числа формируют порядок целого

числа по количеству ненулевых значащих тетэад.

Формирователь 23 сдвигов целого левого и формирователь 50 сдвигов целого

прг

вого числа формируют коды сдвига для

преобразования целого числа в вещественное.

Формирователь 24 номера прерываний формирует номер прерываний по тегам опе- 5 рандов, кода операции и сигнала прерывания.

Нормализатор 27 результата - двухуровневый сдвигатель, осуществляет сдвиг право в случае переполнения вещественноо го и сдвиг влево в случае необходимости нормализации.

Формирователь 31 порядка коррекции по сборкам нулей сумматора 38 мантисс формирует величину, на которую надо изме5 нить порядок большего,

Формирователь 33 кода сдвига для нормализации результата по сборкам нулей определяет величину сдвига на нормализатор 27 результата,

0 Узел 34 обращения суммы осуществляет в случае необходимости интервирование результата сумматора 38 мантисс.

Сумматоры 38, 67 мантисс - условные сумматоры, в которых формируются две

5 суммы для каждых 16-ти разрядов. Одна для случая переноса в эту группу, равном нулю, а другая при переносе, равном единице. С помощью сигнала переноса осуществляется выбор одной из этих сумм.

0Сдвигатели 45, 46 левого и правого чисел - двухуровневые сдвигатели, вторые осуществляют либо сдвиг, либо обращение входного кода,

Нормализаторы 47, 48 целого левого и

5 целого правого чисел -двухуровневые сдвигатели.

Нормализатор 62 результата целых чисел осуществляет преобразование в случае переполнения целого в вещественное.

0 Узел 63 обращения суммы целого числа в случае необходимости осуществляет инвертирование результата сумматора 67 мантисс целого числа.

Узел 68 обращения вправо целого числа

5 в случае необходимости инвертирует MSH- тиссу правого операнда.

Формирователь 73 адреса считывания построен как сумматор, формирует по текущему, индексу команды считывания (ТИКсч)

0 и смещению текущего индекса команды считывания (Д14Р) адрес считывания, как разность между ними.

Формирователь 74 адреса записи построен как сумматор, по текущему индексу

5 команды записи ТИКэп и сигналу операции целочисленной из дешифратора 12 кода операций ОПЕРЦ (выход 92-1) формирует адрес записи. Если ОПЕРАЦ 0, адрес записи равен ТИКэп, в противном случае адрес записи равен ТИКэп + 2.

Выходной сумматор 3 порядков, дешифраторы 12,15, коммутаторы 2,17,32,40, 55,56, формирователи 22, 23, 24, 26,31, 33, 49, 50, 73, 74, нормализаторы 27, 47, 48, 62, узлы 34, 63, 68 обращения суммы, сдвигате- ли 39, 45, 46, сумматоры 38, 67, 68 мантисс могут быть выполнены как аналогичные устройства в прототипе,

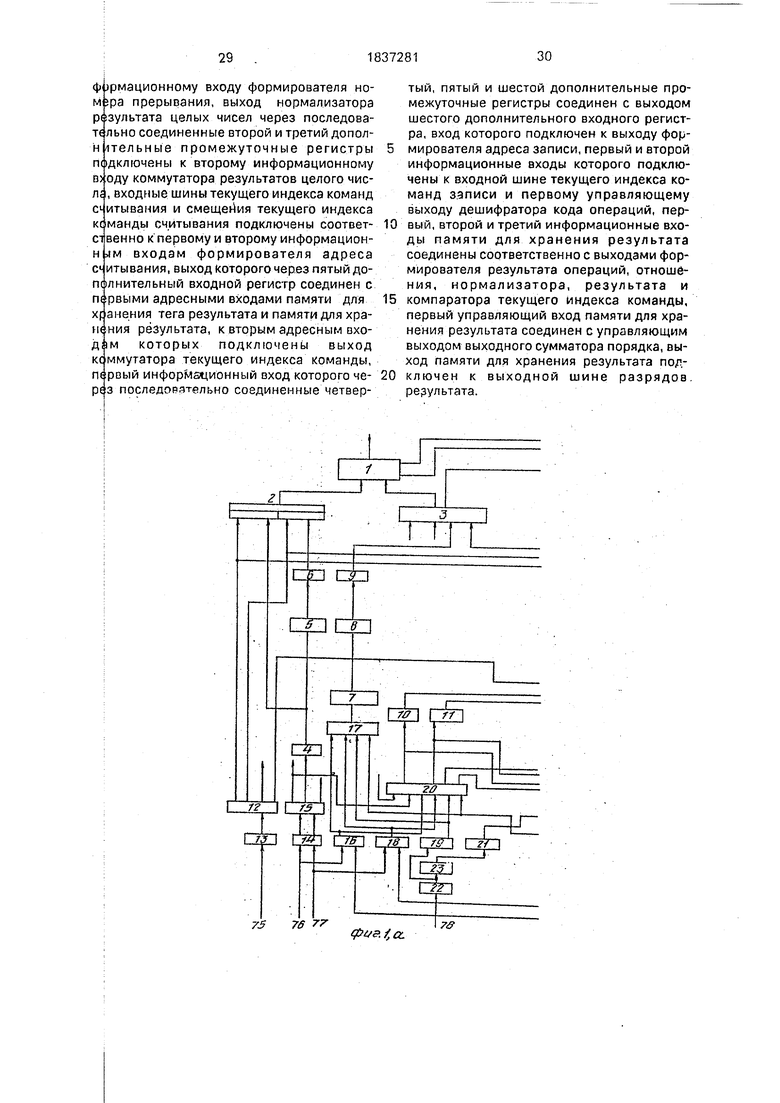

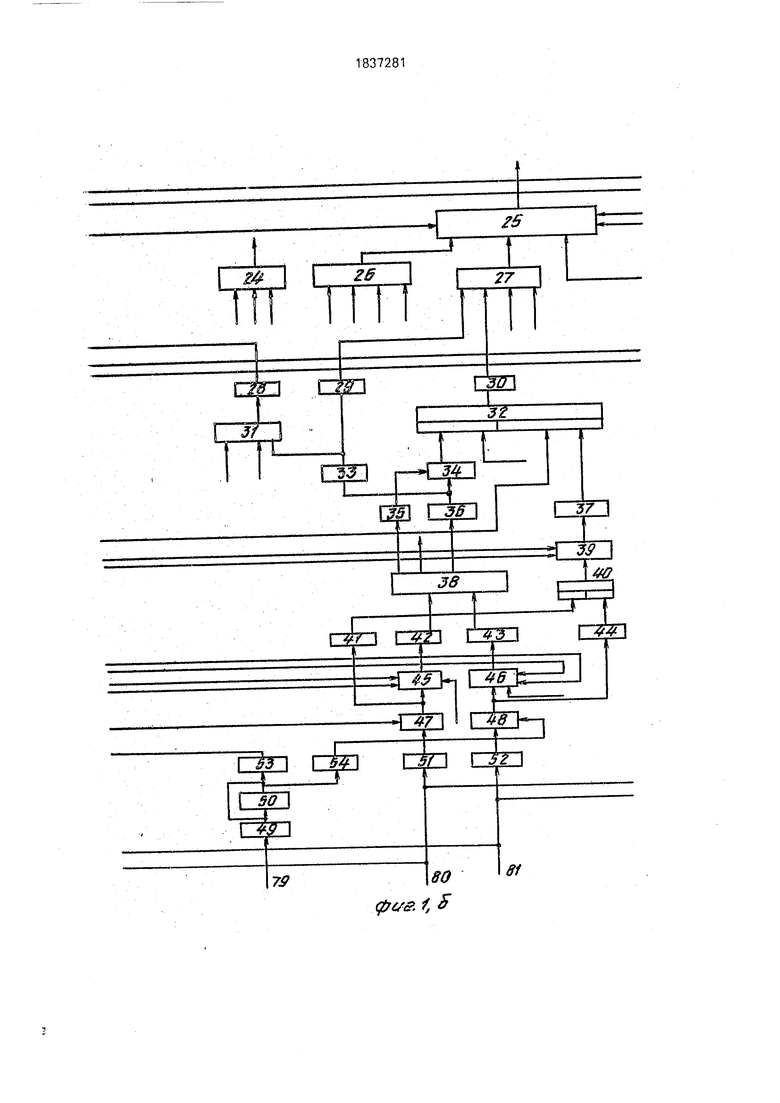

Входной сумматор 20 порядков состоит из двух базовых узлов 126-1 и 126-2, каждый из которых содержит: узел 127 формирования сигнала обращения числа, узел 128 управления, первый узел 129 формирования циклического переноса п случае, когда оба входных числа вещественные, узел 130 формирования сигнала разрешения сдвига числа, второй узел 131 формирования циклического переноса в случае, когда одно из чисел целое, первый сумматор 132, первый коммутатор 133, второй сумматор 134, третий сумматор 135, четвертый сумматор 136, пятый сумматор 137, шестой сумматор 138, седьмой сумматор 139, первый узел 140, второй коммутатор 141, второй узел 142, третий узел 143, четвертый узел 144, пятый узел 145, шестой узел 146, седьмой узел 147.

Узел 127 формирования сигнала обращения числа имеет первый, второй и третий входы 148-1, 148-2, 148-3, узел 128управлё- ния - первый, второй, третий, четвертый, пятый и шестой входы 149-1, 149-2, 149-3, 149-4, 149-5, 149-6. узел 130 формирования сигнала разрешения сдвига числа - первый, второй и третий входы 150-1, 150-2, 150-3, первыйузел 129формирования циклического переноса- первый и второй входы 151-1, 151-2, второй узел 131 формирования циклического переноса - первый, второй, третий и четвертый входы 152-1, 152-2, 152-3, 152-4, коммутатор 133 - первый, второй, третий, четвертый, пятый, шестой и седьмой входы 153-1, 153-2, 153-3, 153-4, 153-5, 153- 6, 153-7, первый и второй выходы 154-1, 154-2, первый сумматор 132-первый и второй входы 155-1,155-2, второй сумматор 134- первый и второй входы 156-1,156-2, третий сумматор 135 - первый и второй входы 157-1,157-2, четвертый сумматор 136- первый и второй входы 158-1,158-2, пятый сумматор 137 - первый и второй входы .159-1, 159-2, шестой сумматор 138 - первый и второй входы 160-1, 160-2, седьмой сумматор 139 - первый и второй входы 161-1, 161-2, второй узел 142 - первый и второй входы 162-1, 162-2, третий узел 143 - первый, второй и третий входы 163-1, 163-2, 163-3, четвертый узел 144 - первый, второй, третий входы 164-1, 164-2, 164-3, пятый узел 145 - первый и второй входы 165-1,165-2, шестой

узел 146 - первый, второй и третий входы 166-1, 166-2, 166-3, седьмой узел 147 - первый, второй и третий входы 167-1, 167-2, 167-3, первый узел 141 - первый, второй,

третий, четвертый, пятый, шестой, седьмой, восьмой входы 168-1. 168-2, 168-3, 168-4, 168-5, 168-6, 168-7, 168-8, первый и второй выходы 169-1, 169-2.

Первый управляющий вход 100-1 входного сумматора 20 порядков соединен с первым входом 148-1 узлов 127 формирования сигнала обращения числа базовыхузлов 126-1 и 126-2.

Второй управляющий вход 100-2 входного сумматора 20 порядков подключен к третьему входу 149-3 узла 128 управления и первому входу 1.50-1 узла 150 базовыхузлов 126-1 и 126-2.

Первый информационный вход 100-3

сумматора 20 порядков соединен с третьим входом 148-3 узла 127, вторым входом 149-2 узла 128, вторыми входами 155-2,156-2,157- 2 сумматоров 132, 134, 135 соответственно, первым входом 158-1 сумматора 136, входом узла 140,-первым входом 162-1 узла 42, вторыми входами 163-2 узлов 143 и 144, третьим входом 153-3 коммутатора 1-33 базового узла 126-1 и с первым входом 149-1 узла 128, вторыми входами 148-2, 150-2, узлов 127 и 130, первыми входами 155-1, 156- 1, 157-1 сумматоров 132, 134 и 135 соответственно, вторым входом 158-2 сумматора 136, вторым входом 162-2 узла 142, третьими входами 163-3 и 164-3 узлов 143 и

144 базового узла 126-2.

Второй информационный вход 100-4 входного сумматора 20 порядков соединен с первым входом 149-1 узла 128, вторыми входами 148-2, 150-2 узлов 127 и 130, первыми входами 155-1, 156-1, 157-1 сумматоров 132, 134 и 135 соответственно, вторым входом 158-2 сумматора 136, вторым входом 162-2 узла 142, третьими входами 163-3, 164-3 узлов 143 и 144 базового узла 126-1 и

с третьим входом 148-3 узла 127, вторым входом 149-2 узла 128, вторыми входами 155-2, 156-2, 157-2 сумматоров 132, 134, 135 соответственно, первым входом 158-1 сумматора 136, входом узла 140, первым вхо0 дом 162-1 узла 142, вторыми входами 163-2, 164-2 узлов 143 и 144, третьим входом 153-3 коммутатора 133 базового узла 126-2.

Третий информационный вход 100-5 входного сумматора 20 порядков подклю5 чен к третьему входу 150-3 узла 130, первому входу 152-1 узла 131, вторым входам 159-2,150-2,161-2 сумматоров 137,138,139 соответственно, первому входу 165-1 узла 145, второму входу 166-2 узла 146, третьему

входу 167-3 узла 147 базового узла 126-1.

Четвертый информационный вход 100-6 входного сумматора 20 порядков в базовом узлз 126-2 подключен к аналогичному входу 100-5 в базовом узле 126-1.

Выходузла 140соединен со вторым вхо- узла 131, с первыми входами 159- 0-1,161-1,166-1 узлов 137.138,139,146 ветственно, со вторыми входами 165-2, -2 узлов 146, 147. ;

Выход узла 128 соединен с первым вхо- florJ 153-1 коммутатора 133 и вторым входом 168-2 узла 141 Выход узла 130 соединен с чет )ертым входом 149-4 узла 128 управле- НИУ, пятый вход 149-5 которого подключен к впходуузла 129. Выходузла 131 соединен с шестым входом 149-6 уз ла 128 и первым входом 168-1 узла 141. Выход сумматора

132

мутатора 133. Выход сумматора 134 соединеь

чет ертым входом 153-4 коммутатора 133.

соединен со вторым входом 153-2 комсо вторым входом 151-2 узла 129 и

Вы

сод сумматора 135 подключен к пятому

вхоцу 153-5 коммутатора 133. Выход сумматора 136 соединен с первыми входами 151-1

и 1

4-1 узла 129 и узла 144,

Выход сумматора 137 подключен к четвертому входу 152-4 узла 131 и шестому вхоцу 153-6 коммутатора 133. Выход сумматора 138 соединен с седьмым входом. 153-7 кол мутатора 133. Выход сумматора 139 под-

клк узл вхоЬу 167-1 узла 147.

Выходы узлов 142, 143, 144, 145, 146,

чен к третьим входам 152-3 и 166-3 )в 131 и 146 соответственно и первому

147

чет мыг 7, 1

баз KON

дин вых

соединены соответственно с третьим, юртым, пятым, шестым, седьмым, вось- 1 входами 168-3,.168-4. 168-5, 168-6, 168- 58-8 узла 141.

Первый выход 154-1 коммутатора 133 эвого узла 126-1 и второй выход 154-2 мутатора 133 базового узла 126-2 объе- ены и является первым управляющим одом 100-1 входного сумматора 20 побаз

рядков.

Второй выход 154-2 коммутатора 133

эвого узла 126-1 и первый выход 154-1

коммутатора 133 базового узла 126-2 объединены и являются вторым управляющим выходом 101-2 входного сумматора 20 по- . Выходузла 127 базового узла 126-2 явл чется третьим управляющим выходом 101-3 входного сумматора 20 порядков. Выход узла 127 базового узла 126-1 является чет вртым управляющим выходом 101-4 вхо, 1ного сумматора 20 порядков.

Первый выход 169-1 узла 141 базового узл i 126 и второй выход 169-2 узла 141 базов зго узла 126-2 объединены и являются пят JM управляющим выходом 101-5 входного сумматора 20 порядков.

5

10 15

0

0

5

5

0

5

0

5

Второй выход 169-2 узла 141 базового узла 126-1 и первый выход 169-1 узла 141 базового узла 126-2 объединены и являются шестым управляющим выходом 101-6 входного сумматора 20 порядков.

Узел 127 формирования сигнала обращения числа, первый узел 129 формирования циклического переноса и второй узел 131 формирования циклического переноса могут быть выполнены как аналогичные устройства в прототипе.

Узел 128управления,узел Сформирования сигнала разрешения сдвига числа, сумматоры 132, 134, 135, 136, 137, 138, 139, первый, и второй коммутаторы 133 и 141, узлы 140, 142, 143, 144, 145, 146, 147 могут быть выполнены на элементной базе серии ИЗООБ, логические функции которых описаны ниже при работе входного сумматора 20 порядков.

Входной сумматор 20 порядков работает следующим образом.

Нз вход 100-1 поступает код операции.

На вход 100-2 поступают типы чисел:

ВЕЩЛ - левое число вещественное;

ВЕЩП - правое число вещественное;

ЦЕЛП - правое число целое;

Ф32П - правое число формата 32.

На вход 100-3 поступает вещественный порядок левого числа 8А -1 А, где 1А - младший разряд, и знак порядка знА.

На вход 100-4 поступает вещественный порядок правого числа 8В-1В, где 1В - младший разряд, и знак порядка знВ.

На вход 100-5 поступает ПЦП - порядок правого целого числа, состоящий из 5 порядков: 5ПЦП, 4ПЦП, ЗПЦП, 2ПЦП, ХПЦП, где ХПЦП - младший разряд.

На вход 100-6 поступает ПЦЛ - 5 разрядный порядок левого целого числа, где 1 ПЦЛ - младший разряд.

В узле 127 вычисляется сигнал обращения числа на основе знаков обоих входных операндов и кода операции: сложение или вычитание,

В узле 128 формируются сигналы коммутации для коммутатора 133 и узла 144:

ВВРС ВЕЩЛ х ЗЕЩПх РСД(1)

1КСП ВВРСхЗНАхЗНВ(2)

2КСП ВВРСхЗНАхЗНВ(3)

ЗКСП-ВВРСхЗНАхЗНВ...(4)

4КСП ВЕЩЛ х ЦЕЛП х ЗНА к РСД (5) 1 КСЛ ВЕЩЛ х ЦЕЛП х ЗНА х РСД (6) РАЗРП 2КСП х ЦПВ + tjOCTl + + ЗКСП х ЦПВ + 4КСП х ЦПЦ(7)

РАЗРЛ 1КСЛ к ЦПЦ + 4КСП х ЦПЦ, (8)

где РСД - сигнал разрешения сдвига, фор- мируемый в узле 130 (вход 149-4);

ЦПВ - циклический перенос в случае двух вещественных чисел, формируемый в узле 129 (вход );

ВЕЩ Л, ВЕЩП, ЦЕЛП (вход 149-3); ЗНА (вход-149-2);

ЗНВ (вход-149-1);

1КСП - 4КСП - сигналы коммутации правого Числа;

1КСЛ - сигнал коммутации левого числа;.

РАЗРП - разрешение сдвига правого числа;

РАЗРЛ разрешение сдвига левого числа.

Сигналы управления коммутатором формируются все одновременно, так как сумматор порядков работает в конвейерном режиме.

Сигналы управления 1 КСП, 2 КСП, 3 КСП, 4 КСП, РАЗ Р. П необходимы для фор- мирования сигналов сдвига правого числа, а 1КСЛ, РАЗР Л-левого числа.

Необходимость нескольких сигналов: 1 КСП, 2 КСП, 3 КСП, 4 КСП обусловлена различными ситуациями, реализуемыми сумма- торами, функции и смысл которых указаны ниже.

8 узле 130 формируется сигнал разрешения сдвига числа (РСД). Если РСД 0, то число при выравнивании порядков не сдви- гается,: РСД РСДЦхРСДФ32 (9) При анащре,.целого числа формируется: РСДЦ ПЦПх ЦЕЛП (10) При анализе вещественного числа фор- мата 32 для случая, когда порядок минимальный:,

РСДФ32 ПЦП х Ф32П х х ВЕЩПх5 В,(11)

где сигналы поступают:

ПЦП по входу 150-3; Ф32П, ВЕЩП, ЦЕЛП по входу 150-1; 5В по входу 150-2.

Обозначим: Н - полусумма; G - перенос; Р - условия переноса через разряды.

Цифра перед обозначением Н,ХЗ, Р указывает, какая пзра разрядов участвует в формировании операции, первая цифра после буквенного обозначения указывает количество разрядов, участвующих в формирова- нии операции, вторая цифра - номер сумматора.

Сумматор 132 складывает четыре младших разряда модулей порядков вещественных входных левых (А) и правых (В) чисел: 1С21 -2Ах2В+(2А + 2В)х х 1Ах1В(12)

ЗН1 ЗА Я 3В(13)

1S1« 1A & 1В(14)

2S1 2А Ф 2В Ф 1Ах1В (15)

3S1 ЗН1 © 1G21(16)

4S1 (ЗИ1 х 1G21) 4А $ ©4В . ЗАхЗВ,(17)

где разряды порядка А поступают по входу 155-1;

разряды порядка В поступают по входу 155-2.

В коммутаторе 133 формируются сигналы сдвига 8СДЛ, 4СДЛ, 2СДЛ, 1СДЛ (выход 154-1) для сдвига левого числа и 8СДП, 4СДП,2СДП,1СДП (выход 154-2)для сдвига

правого числа. j.

СТР ГкСПх 2КСПхЗКСП(18)

1СДП РАЗРх(153х2КСП + + 1S2 х 1 КСП + 1 S3 х ЗКСП + + 1S6xCTP)(19)

2СДП РАЗРП х (2S2 х 2КСП + + 2S1 х 1 КСП+ 2S3x ЗКСП+ + 2S5 х СТР)(20)

4СДП РАЗП х (3S2 х 2КСП + 1 КСП + 3S3 х ЗКСП + + 3S5xCTP)(21)

8СДП РАЗП х (4S2 + 2КСП + + 4S1 х1 КСП+ 4S3x ЗКСП+ +4S5xCTP)(22)

1СДЛ РАЗ/1 х (1S5 х ЗНА + + 1S6X3HA)(23)

2СДЛ РАЗЛ х (2S5 х ЗНА + + 2S6 х ЗНА)(24)

4СДЛ РЛЗЛ х (3S5 х ЗНА + + ЗЗбхЗНА)(25)

8СДЛ РАЗЛ х (4S5 х ЗНА+ + 4S6x3HA),(26)

где разряды суммы 1S1,2S1,3S1,4S1 поступают по входу 153-2, разряды суммы 1S2, 2S2, 3S2, 4S2 - по входу 153-4, разряды суммы 1S3, 2S3, 3S3, 4S3 - по входу 153-5, разряды суммы 1S5,2S5,3S5,4S5 - по входу 153-6, разряды суммы 1S6, 2S6, 3S6, 4S6 - по входу 153-7, ЗНА поступает по входу 153-2, 1КСП,2КСП, ЗКСП, РАЗРП, РАЗЛ по входу 153-1.

Сумматор 134 вычитает четыре младших разряда модулей порядков вещественных входных чисел А и В, при условии, что циклический перенос равен нулю:

ЗН2 ЗАФЗВ (27)

1G22.2Ax2B(2A + 2B)x1Ax1B (28).

1S2 1.А Ф JTB.(29)

252 2А е 2В 8 fAxlB(30)

3S2 ЗН2 + 1G22(31)

4S2 «(ЗН2 xTG22) Ф 4А Ф ЗА хТВ,(32)

где разряды порядка А поступают по входу 156-2, разряды порядка В - по входу 156-1. Сумматор 135 вычитает четыре младших разряда модулей порядков вещественных входных чисел А и В при условии, что циклический перенос равен 1, т.е. к млэдше

10

у разряду суммы прибавляется единица

И кличвскогдлёЩноса

1Р13 1АхШ(33)

2G13-2A--2B.(34)

ЗСН 2А Ф (35)

1Р23 (1А+1В)х(2А + 2В)(36)

1G23 j2G13jMP23(37)

1S3 1A ® 1B(38)

253 1Р13Ф2НЗ (39)

353-2С13Ф(1Р13х2НЗ)Ф ЗН2 (40) 453 (ЗН2 х 1G23) $ 4S2A,(41)

|е разряды порядка А поступают по входу

7-2. разряды порядка В - по входу 157-1. Сумматор 136 вычитает четыре старших зряда модулей порядков вещественных 15 одных чисел А и В для рпределения того, о разность порядков больше или равна 15. 3G24 6А х + (6А + 6В) х 5А хББ (42) 7Н4 7А Ф (43)

8S4A 8А а 8В ф (7А х 7В)(44) 20

5S4 5А Ф 5В(45)

6S5 6А Ф 6В © (5А х 5В)(46)

7S4 7Н4 © 3G24(47)

8S4 (7Н4 х 3G24) Ф 8S4A,(48)

25

гДе разряды порядка А поступают по входу 1 8-1, разряды порядка В - по входу 158-2. Сумматор 137 складывает или вычитает тыре младших разряда модулей порядков одных чисел вещественного А и целого В

30

и условии, что циклический перенос ран нулю.

ЗН5 ЗАЦ Ф ЗПЦП(49)

1С25 2АЦх.2ПЦП + (2АЦ + + 2ПЦП)х1АЦх 1ПЦП(50)

455С 4АЦФ4ПЦП® (ЗАЦхЗЦПЦ) (51) 35

155 1АЦ Ф 1ПЦП(52)

255 2АЦФ2ЦПЦф(1АЦх1ПЦП) (53) 355 1С25ФЗН5(54)

455 (ЗН5 х 1G35)$ 4S5C,

е разряды АЦ поступают по входу 159-1, 40 зряды П ЦП - по входу 159-2.

Сумматор 138 вычитает четыре млад- их разряда модулей порядков входных чй- л вещественного А и целого В при ловии, что циклический перенос равен 1, 45 е. к младшему разряду суммы прибавляет- единица циклического переноса:

1Р16 1АЦ + 1ПЦП(56)

2С16 2АЦх2ПЦП. (57) 50 2Н6 2АЦ Ф 2ПЦП(58)

1Р26 (1АЦ + 1ПЦП)х(2АЦ + + 2ПЦП)(59)

1G26 2G16 + 1Р26(60)

156 ГАЦ © 1ПЦП(61) 55

256 1Р16 & 2Н6(62) 356-2С16Ф (1Р16х2Н6) Ф ЗН5 (63)

456 (3H5x1G26). Ф 4S5C, (64) е разряды АЦ поступают по входу 160-1 азряды ПЦП - по входу 160-2.

0

5

0

5

0

5

0

5

0

5

Сумматор 139 вычитает четыре старших разряда модуля порядка вещественного входного числа А из старшего разряда порядка целого входного числа В,

5S7 5АЦ Ф 5ПЦЛ(65)

6S7 (5АЦ х 5ПЦП) Ф 6АЦ(66)

3627 6АЦх5ЦАх5ПЦП(67)

757 7АЦ Ф 3G27(68)

857 (7АЦ х 3G27) Ф 8АЦ,(69)

где разряды АЦ поступают по входу 161-1, разряды ПЦП - по входу 161-2.

Узел 140 обращает порядок входного левого числа А АЦ ЗНА Ф IA,

где I 1-8-(70)

В коммутаторе 141 формируются сигналы БР15Л (выход 169-1) для левого числа и БР15П (выход 169-2) для правого числа, коммутаций результатов, формируемых в узлах 142-147, посредством сигналов, формируемых в узле 128, выдвигающие число за разрядную сетку, если разность порядков больше или равна 15.

БР15П - РАЗП х (2БР15 х 2КСП + +1БР15х1КСП + ЗБР15 + ЗКСП + + 5БР15хСТР)(71)

БР15Л 4БР15х 1КСП + + 6БР15хЦПЦх4КСП + -ь ЦПЦхШСЛ,(72)

где СТР формируется по формуле (18); РАЗП - по формуле (Д ЦПЦ поступает по входу 168-1, РАЗП, 1КСП, 2КСП, ЗКСП, 4КСП, 1КСП - по входу 168-2,

1БР15 - по входу 168-3, 2БР15 - по входу 168-4, ЗБР15 - по входу 168-5, 4БР15 - по входу 168-6, 5БР15 - по входу 168-7, 6БР15 - по входу 168-8. Узел 142 формирует сигнал БР15, указывающий, что разность порядков больше или равна 15 при сложении модулей порядков вещественных входных чисел А и В.

2Р21 (ЗА + 3В) х (4А + 4В)(73)

58АВ 5А + 6А + 7А + 8А + 5В + + 6В + 7В + 85(74)

2G21 4Ax4B(4A + 4B)x3Ax3B (75) 1BP15 58AB + 2G2l+2P21x1G21, (76) где 1С21 формируется как в формуле (12).

Разряды порядка А поступают по входу 162-1,

разряды порядка В - по входу 162-2. Узел 143 формирует сигнал БР15 при вычитании модулей порядков вещественных входных чисел А и В при условии, что циклический перенос равен нулю.

2G22 4А х 4В.(4А ч- 4В) х ЗА х 3В (77) 2Р22(4А + 4В)х(ЗА + )(78)

1G42 2G22 + 2Р22 х 1G22(79)

2БР 15 554 x1G24 ч-В54

+ 754 + 854,(80)

де 1G22 формируется как в формуле (29).

Разряды порядка А поступают по входу 63-2,

разряды порядка В - по входу 163-3,

разряды суммы 54-по входу 163-1.

Узел 144 формирует сигнал БР15 при вычитании модулей порядков вещественных входных чисел Аи В при условии, что Циклический перенос равен единице.

1G43 1G23x2P22 + 2G22(81)

ЗБР15 (5 34 +654-ь754 + .

4-8S4)xiG43 + .

x 8S4x1G43,:.(82)

где 1G23 формируется как в формуле (37),

2G22 - как в формуле (77),

2 Р22-как в формуле (78).,

Разряды порядка А поступают по входу

164-2, : : - . : . ... V

разряды порядка В - по входу 164-3, разряды суммы 4 поступают по входу 164-1.

Узел 145 формирует сигнал БР15 при сложении модулей порядков входного вещественного числа А и входного целого числа В.

Б8АЦ - 5АЦ + 6АЦ + 7АЦ + 8АЦ + + 5ПЦП (83)

2П2-(4АЦ + 4ПЦП)х(ЗАЦ + ЗЦПЦ) (84) 2G25 - (4АЦ х 4ПЦП + 4АЦ + 4ПЦП) х х ЗАЦхЗПЦП(85)

4БР15 2Р2х1С25 + 2С25 + 58АЦ, (86) где 1G25 формируется как и формуле (50). Разряды АЦ поступают по входу 165-2, разряды ПЦП - по входу 165-1 Узел 146 формирует сигнал БР.15 при вычитании модуля порядка входного вещественного числа А из целого числа В при условии, что циклический перенос равен нулю-

1G45 2G25+1G25x2P2(87)

5BP15 5S7 + 1G45 + SS7 + + 857,(88)

где 2С25 вычисляется по формуле (8.5), 1G25 вычисляется по формуле (50), 2Р2 вычисляется по формуле (84). Разряды АЦ поступают по входу 166-1, разряды ПЦ-по входу 166-2, разряды суммы 7 -по входу 166-3. Узел 147 формирует сигнал БР15 при вычитании модуля порядка входного вещественного числа А из целого числа В при . условий, что циклический перенос равен единице.

1G46-2G25 + 2P2X1G26(89)

6EPi.5-(SS7 + 6S7 + 7S7+. +8S7)x 1G46 + 5S7 х 5S7 х 6S7 х х 787x857x1646.(90)

где 2G25 формируется как в формуле (№),

2 Р2-как в формуле (84), 1С26 - как в формуле (60). Разряды. АЦ поступают по входу 167-2, разряды ПЦП - по входу 167-3, разряды суммы 7-по входу 167-1.

Входной сумматор 20 порядков состоит из двух базовых узлов 126-1 и 1:26-2, только в один узел 126-1 по входу 100-5 подается ПЦП, а а другой узел 126-2 по входу 100-6 0 (аналогично расположенному в базовом узле) подается ПЦЛ.

Выходы 101-1 БР15Л, 101-2 БР15П, 101-5 СДЛ, 101-6 СДП соответственно двух базовых узлов соединены в инверсной фазе 5 проводным и, как показано на фиг.2. .- . Входной сумматор порядков 20 предназначен для вычисления модуля разности порядков и формирования кода сдвига чис- ла из полученной разности в случае, когда 0 хотя бы один из входных операндов - вещественный.

Входной сумматор 20 порядков формирует коды сдвига входных операндов для выравнивания порядков перед сложением 5 мантисс входных операндов.

В базовых узлах 126-1, 126-2 коды сдвига правого числа 8СДП, 4СДП, 2СДП, 1СДП и коды сдвига левого числа 8СДЛ, 4СДЛ, 2СДЛ, 1СДЛ формируются непос- 0 редственно из модуля разности порядков, при условии когда два входных числа вещественных, либо одно из чисел целое. При этом в узле 126-1 по входу 100-5 подается целое правое число, а в узел 126-2 по входу 5 100-6-целое левое число.

Узел 128 управления управляет коммутатором 133 сдвигов чисел и коммутатором 141 сигналов (БР15), означающими, что разность порядков больше или равна 15 (может 0 быть использован для расширения функциональных возможностей).

Коммутатор 133 формирует сигналы сдвигов левого и правого чисел коммутаций сумм сумматоров 132, 134, 1350 137, 5 138 посредством сигналов, формируемых в узле 128.

Коммутатор 141 формирует сигналы (БР15) для левого и правого чисел коммутаций результатов, формируемых в узлах 142- 0 147, посредством сигналов, формируемых в узле 128,

Для организации работ узла устройства сложения необходимо дешифрировать код операций и теги входных операндов, 5 Код операции поступает со входной шины 7,5-через первый входной регистр 13 на дешифратор 12. Результатом дешифрации являются сигналы ОПЕРЦ (выход 92-1) и ОПЕРЦ(выход92-2), сигнал ВЫДМЛ (выход 92-4) и группа вспомогательных управляющих сигналов (выход 92-3), Сигнал ОПЕРЦ характеризует длину конвейера устройства ;ложения: если ОПЕРЦ 1 (ОПЕРЦ 0) - (оманда выполняется за два такта, если }ПЕРЦ 0(ОПЕРЦ 1), конвейер-четырехтактный. Сигнал ВЫДМЛ разрешает выдать с коммутатора 32 результата эезультат сложения по алгоритму выдачи младшего. Остальные управляющие сигналы, объединенные выходом 92-3, необходимы для работы конкретных узлов устройств сложения.

Теги входных операндов (тег левого числа по входной шине 76 и тег правого числа) по входной шине 77 через входной регистр 14 (входы соответственно 93-1 и 93-2) приходят на дешифратор 16 тегов. Результатом дешифрации являются тег результата, который с выхода 96-2, в зависимости от длины конвейера, идете промежуточного регистра 4, либо через задержку на промежуточных регистрах 5, 6 либо минуя ее на коммутатор 2 тега результата и оттуда в память 1, а также сигналы управления, снимаемые с выходов 96-1 и 96-3.

В случае, когда один из двух операндов вещественный, для выражения порядков перед операцией сложения мантисс порядки чисел из входных шин 80 (левое число) и 81 (правое число), а также разряды порядков, размещенные в тегах (входные шины 76, 77), через третий и четвертый входные регистры 16, 18 поступают в сумматор 20 порядков.

Если числа целые, то для определения их порядков по входным шинам 78 и 79 на вход формирователей 22 и 49 идут сборки нулей левого и правого входных операндов. Далее порядки целого идут соответственно на формирователи 23 и 50, которые через шестой и второй дополнительный входные регистры 21 и 54 в качестве управления подаются на вход 115-1 нормализатора 47 целого левого числа и на вход 116-1 нормализатора 48 целого правого числа.

Порядки целого через пятый и первый дополнительный регистры 19 и 53 поступают на входы 100-5 и 100-6 сумматора 20 порядков, на входы 101-1 и ТОО-2 которого поступают результаты дешифрации кодов операций и тегов входных операндов с выходов 92-3 и 96-1 дешифраторов 1.2 и 15 соответственно.

. Коды сдвигов соответственно левого и правого чисел с выходов 101-1,101-2 и сигналы обращения левого и правого чисел с выходов 101-3, 101-4 сумматора 20 порядков поступают на управляющие входы 113- 1, 114-1 и 113-2, 114-2сдвигателей45и46. Кроме того, через первый и второй выходные регистры 10 и 11 коды сдвигов чисел (вых. 101-1, 101-2) подаются на входы 111- 1, 111-2 сдвигателя 39 младших.

Сами числа по входным шинам 80 и 81

5 через седьмой и восьмой входные регистры 51 и 52 поступают в нормализаторы 47 и 48 целого, где целое число преобразуется в вещественное, а вещественное проходит без изменений. Далее результаты поступают в

0 сдвигатели 45 и 4.6, чтобы при необходимости выровнять порядки.

Одно из них сдвигается по коду сдвига, а другое обращается в зависимости от знаков чисел и кода операций. Затем результа5 ты сдвигов через первый и второй входные регистры 42 и 43 сумматора мантисс передаются в сумматор 38 мантисс, а результаты нормализации целого через первый и второй входные регистры 41 и 44 младших по0 ступают в коммутатор 40 младших .

Результат сложения двух чисел из сумматора 38 мантисс с выхода 110-3 через дополнительный выходной регистр 36 по5 ступает на узел 34 обращения суммы, управляемый сигналом обращения суммы, выходящим из сумматора 38 мантисс с выхода 110-1 и приходящим в узел 34 на вход 108-1 через регистр 35. Результат обраще0 ния суммы поступает на .ходы 107-2, 107-3 коммутатора 32, где выбирается результат в зависимости от того, какая операция - выдача младшего или нет, что определяется сигналами управления 96-3 и 92-4 с выходов

5 дешифраторов 12 и 15. Результате коммутатора 32 через десятый промежуточный регистр 30 подается на вход 105-3 нормализатора 27 результата, который уп- равляется (вход 105-4) сигналами сдвига,

0 получаемыми в формирователе 33 кода . сдвигов для нормализатора результата и задерживаемые на восьмом промежуточном регистре 29.

Из нормализатора 27 результата он по5 ступает на вход 103-3 памяти 25. Кроме того, в памяти 25 подается на аход 103-2 резуль- тат отношений из формирователя 26 результата операций отношений, где результат отношений формируется на основе пере0 полпенни, поступающих с выхода 110-2 сум- матора 38 мантисс, с выхода 122-4 сумматора 67 мантисс целого, а также сигналов управления с выходов 92-3, 96-1 дешифраторов 12, 15 на входы 104-3, 104-4,

5 104-1, 104-2 формирователя 26 соответственно.

Порядок результата формируется в выходном сумматоре 3 порядков и с выхода 91-1 те разряды порядка, которые размещены в теге результата, идут в память 1, а

остальные разряды порядка с выхода 91-2 - в память 25, где хранится результат.

Выходной сумматор 3 порядков работает на принципе вычитания из порядка большего, т.е. большего из двух входных порядков, порядка коррекции.

Порядок большего формируется в коммутаторе 17 порядка большего из двух порядков вещественного и двух порядков целого и проходит через три промежуточных регистра 7, 8, 9.

Порядок коррекции формируется в формирователе 31 порядка коррекции, из сдвигов формирователя 33 кода-сдвига и через седьмой промежуточный регистр 28 проходит 8 выходной сумматор 3 порядков.

Управляют вычитанием сигналы управления с выходов 92-3 и 96-1 дешифраторов 12,15.. :- .. :- : , ;

Кроме того, в устройстве сложения формируется номер прерывания (выходная шина 86) на основе сходных сигналов: сигналы управления с выходов 92-3, 96-1 дешифраторов 12, 15, сигнал переполнения целого с выхода 122-4 сумматора 67 мантисс.

Сложение Двух целых происходит слё- . дующим .образом.

По входным шинам 80 и 81 в устройство поступают операнды, которые принимаются в третий и пятый входные регистры 69 и 70. Левый операнд поступает на вход 121-1 сумматора 67, а правый проходит через узел 68 обращения, где-в случае необходимости обращается, а затем поступает на вход 121-2 сумматора 67. С сумматора 67 с выхода 122-1 сумма поступает в регистр 64, а сигналы обращения суммы целых (вых. 122- 2) и переполнения целых (вых; 122-3) поступают в регистры 65 и 66, После первого выходного регистра 84 сумма попадает в узел 63 обращения на вход 120-1, где в случае необходимости происходит обращение суммы,

В случае целочисленной операции (время её выполнения два такта) после узла 63 обращения сумма попадает на вход 117-2 коммутатора 55, а затем в память 25 для хранения результата на вход 103-4, выходную шину 87,

В случае универсальной команды (время ее выполнения 4 такта) сумма после узла 63 обращения поступает в нормализатор 62 результата целых чисел на вход 119-1, где в случае переполнения (вход 119-2) происходит преобразование целого результата в вещественный того же формата. После этого сумма поступает на второй и третий дополнительные промежуточные регистры 57 и 58, где задерживается на 2 такта, Затем сумма поступает на вход 117-4 коммутатора

55, далее как в случае целочисленных команд.

По шине 82 в формирователь 73 адреса считывания на вход 123-1 поступает текущий индекс команды считывания, по шине 83 на вход 122-2 поступает смещение теку- . щего индекса команды считывания (ТИКСч). Полученный адрес считывания задерживается в пятом дополнительном регистре 71 и

0 поступает в память 25 для хранения результата на вход 103-5 и в память 1 для хранения тега результата на вход 88-3. В памяти 25 считывается содержимое ячейки, определяемое адресом считывания, выдается в шину

5 83 разрядов результатов.

По шине 84 в формирователь 84 адреса записи на вход 125-1 поступает текущий индекс команды записи, на вход 125-2 поступает сигнал ОПЕРЦ с выхода 92-1

0 дешифратора 12, говорящий какова длительность команды. Полученный адрес записи поступает в шестой дополнительный входной регистр 72. В случае целочисленной команды этот адрес поступает на вход

5 118-3 коммутатора 56, а затем на вход 103-6 памяти 25 для хранения результата и вход 88-4 памяти 1. В случае универсальной команды адрес записи задерживается на пятом и шестом дополнительных регистрах 60

0 и 61, а затем поступает на вход 118-2 коммутатора 56.

В памятях 25 и 1 происходит запись результата и тега результата в ячейку, определяемую адресом записи. Таким образом,

5 введение узла обращения целого правого числа, сумматора мантисс целого числа, узла обращения суммы целого числа, нормализатора результатов целых чисел, коммутатора результата целого числа, фор0 мирователя порядка целого правого числа, сдвигателя правого числа, сдвигателя младших, узла обращения суммы, регистров в указанной выше связи позволило осуществлять одновременное вычисление вещест5 венных и целых чисел. Это привело к повышению быстродействия устройства. Формула изобретения Устройство для сложения, содержащее память для хранения тега результата, ком0 мутатор тега результата, выходной сумма-. тор порядков, дешифратор кода операций, дешифратор тегов, коммутатор порядка большего, входной сумматор порядка, формирователь порядка целого левого числа,

5 формирователь сдвигов целого левого числа, формирователь номера прерываний, формирователь результата операций отношения, нормализатор результата, формирователь порядка коррекции, формирователь кода сдвига для нормализатора результата,

узел обращения суммы, сумматор мантисс, сдвигатель левого числа, нормализатор целого левого числа, восемь входных регистров, первый и второй входные регистры сумматора мантисс, девять промежуточных регистров, первый выходной регистр сумматора мантисс, входную шину кода операций, Е ходные шины тега левого и правого чисел, сходные шины разрядов левого и правого 1исел, входную шину сборок нулей левого исла, входную шину сборок нулей правого ччсла, выходную шину тега результата, выводную шину номера прерываний, выходную шину разрядов результатов, входная шина кода операций через первый входной регистр соединена с входом дешифратора кода операций, первый и второй управляющие выходы которого подключены соответ- (;твенно к первому и второму управляющим входам коммутатора тега операций, выход которого соединен с первым информацион- шм входом памяти для хранения тега ре- ультата, третий управляющий выход дешифратора кода операций подключен к тервым управляющим входам входного ;умматора порядков, выходного сумматора порядков, формирователя номера прерываний, формирователя результата операций отношения, нормализатора ре- 1ультата, формирователя порядка коррек: дни, входные шины тега левого и правого шсел соединены соответственно с первым 1 вторым информационными входами входного регистра, первый и второй информационные выходы которого подключены к соответствующим входам дешифратора те- ов, первый управляющий выход которого соединен с вторыми управляющими входами входного сумматора порядков, выходного сумматора порядков, формирователя номера прерываний, формирователя результата операций отношения, нормализатора результатов, формирователя порядка коррекции, второй управляющий выход дешифратора тегов через первый промежуточ- ный регистр подключен к перовому информационному входу коммутатора тега результата и входу второго промежуточного регистра, выход которого через третий промежуточный регистр соединен с вторым им- формационным входом коммутатора тега результата, входные шины тега левого числа и разрядов левого числа подключены соответственно к первому и второму информа- ционным входам третьего входного |регистра, выход которого соединен с пер- вым информационным входом коммутатора порядка большего и первым информацион- jubiM входом входного сумматора порядка, (второй информационный вход которого и

второй информационный вход коммутатора порядка большего соединены с выходом четвертого входного регистра, первый и второй информационные входы которого подключены соответственно к входной шине тега первого числа и входной шине разрядов первого числа, которая соединена также с входом восьмого входного регистра,входная шина сборок нулей левого числа соединена с входом формирователя порядков целого числа, выход которого соединен с входом формирователя сдвигов целого левого числа и выходом пятого входного регистра, который соединен с третьими информационными входами входного сумматора порядков и коммутатора порядка большего, выход которого через последовательно соединенные четвертый, пятый и шестой промежуточные регистры подключен к первому информационному входу выходного сумматора порядка, второй информационный вход которого соединен через седьмой промежуточный регистр с выходом формирователя порядка коррекции, информационный вход которого и вход восьмого промежуточного регистра подключены к выходу формирователя кода сдвига для нормализации результата, выходы седьмого и восьмого промежуточных регистров соединены соответственно с первым и вторым информационными входами нормализатора результата, информационный выход выходного сумматора порядка соединен с вторым информационным входом памяти для хранения тега результата, выход которой подключен к выходной шине тега результата, входная шина разрядов левого числа через седьмой входной регистр соединена с информационным входом нормализатора целого левого числа, к первому информационному входу которого подключен выход шестого входного регистра, первый управляющий вход сдвигателя левого числа соединен с первым управляющим выходом входного сумматора, вьг- од сдвигателя левого числа через первый входной регистр сумматора мантисс соединен с первым информационным входом сумматора мантисс, второй информационный вход которого подключен к выходу второго входного регистра сумматора мантисс, управляющий выход сумматора мантисс через выходной регистр сумматора мантисс соединен с управляющим входом узла обращения суммы, первый информационный выход сумматора мантисс соединен с первым информационным входом формирователя результата операций отношения, выход формирователя номера прерываний соединен с выходной шиной номера прерываний, от л и ч а ю8 е с я тем, что, с целью повышения бысродействия, оно содержит память для ранен-ия результата, коммутатор нормаизатора результата, сдвигатёль младших, оммутатор младших, сдвигатёль первого исла, нормализатор целого правого исла, формирователь порядка целого равого числа, формирователь сдвигов цеого правого числа, коммутатора результаа целого числа, коммутатор текущего индекса, нормализатор результата целых исел, узел обращения суммы целого числа, сумматор мантисс целого числа, узел обращения целого правого числа,формирова- теяь считывания, формирователь записи, с первого по шестой дополнительные входные регистры, первый и второй входные регистры младших, с первого по шестой дополнительные промежуточные регистры, первый и второй выходные регистры входного сумматора порядка, дополнительный выходной регистр сумматора порядка, с первого,по третий выходные регистры сумматора мантисс целого числа, входная шина текущего индекса команды считывания, входная шина смещения текущего индекса команды считывания, входная шина текущего индекса команды для записи, причем входная шина сборок нулей первого числа подключена к входу формирователя порядков целого правого числа, выход которого соединен с входом формирователя сдвигов целого правого числа и входом первого дополнительного входного регистра, который подключен к четвертым информационным входам коммутатора большего порядка и входного сумматора порядка, первый управляющий выход которого через первый выходной регистр сумматора порядка соединен с первым управляющим входом сдвигателя младших, к второму управляющему входу которого подключен через второй выходной регистр сумматора порядка второй управляющий выход входного сумматора порядка, который соединен также с первым управляющим входом сдвигателя правого числа, второй управляющий вход которого соединен с третьим управляющим выходом входного сумматора порядка, четвертый управляющий выход, которого подключен к второму управляющему входу сдвигателя левого числа, информационный вход которого соединен с выходом нормализатора целого левого числа, который через первый входной регистр младших подключен к первому информационному входу коммутатора младших, к второму информационному входу которого через второй входной регистр младших подключен выход нормализатора .целого правого числа,который соединен с

информационным входом сдвигателя правого числа, выход которого подключен к входу второго входного регистра сумматора мантисс, первый информационный вход

нормализатора целого правого числа соединен через второй дополнительный входной регистр с выходом формирователя сдвига целого правого числа, а второй информационный вход - с выходом восьмого входного

0 регистра, второй информационный выход сумматора мантисс через дополнительный выходной регистр сумматора мантисс подключен к входам формирователя кода сдвига для нормализатора результата и узла

5 обращения суммы, выход узла обращения суммы, выход которого соединен с первым информационным входом коммутатора нормализатора результата, первый и второй управляющий входы которого подключены

0 соответственно к третьему управляющему выходу дешифратора тегов и четвертому входу дешифратора кода операций, второй информационный вход коммутатора нормализатора результатов через первый допол5 н ительный промежуточный регистр соединен с выходом сдвигателя младших, вход которого подключен к выходу коммутатора младших, выход коммутатора нормализатора результата соединен с входом

0 девятого промежуточного регистра, первый и второй управляющие выходы дешифратора кода операций подключены соответственно к первым и третьим управляющим входам коммутатора результатов целого

5 числа и коммутатора текущего индекса целого, входная шина разрядов левого числа через третий дополнительный входной регистр соединена с первым информационным входом сумматора мантисс целого,

0 входная шина разрядов правого числа через четвертый дополнительный входной регистр соединена с входом узла обращения целого правого числа, выход которого подключен к второму информационному входу

5 сумматора мантисс целого числа, первый

информационный и управляющий выходы

которого соединены соответственно через

первый и второй выходные регистры сум1 матора мантисс целого числа с информаци0 онным и управляющим входами узла обращения суммы, выход которого подключен к первому информационному входу . коммутатора целого числа и к информационному входу нормализатора результата це5 лых чисел, управляющий вход которого через третий выходной регистр сумматора мантисс целого числа соединен с первым управляющим выходом сумматора мантисс, выход третьего дополнительного регистра сумматора мантисс подключен также к инфЬрмационному входу формирователя номера прерывания, выход нормализатора результата целых чисел через последовательно соединенные второй и третий допол- нчтельные промежуточные регистры подключены к второму информационному коммутатора результатов целого чис- м, входные шины текущего индекса команд с -итывания и смещения текущего индекса кбманды считывания подключены соответственно к первому и второму информационном входам формирователя адреса считывания, выход Которого через пятый дополнительный входной регистр соединен с первыми адресными входами памяти для хранения тега результата и памяти для хранения результата, к вторым адресным входим которых подключены выход ксммутатора текущего индекса команды, первый информационный вход которого через последовательно соединенные четвертый, пятый и шестой дополнительные промежуточные регистры соединен с выходом шестого дополнительного входного регистра, вход которого подключен к выходу формирователя адреса записи, первый и второй информационные входы которого подключены к входной шине текущего индекса команд записи и первому управляющему выходу дешифратора кода операций, первый, второй и третий информационные входы памяти для хранения результата соединены соответственно с выходами формирователя результата операций, отношения, нормализатора, результата и

компаратора текущего индекса команды, первый управляющий вход памяти для хранения результата соединен с управляющим выходом выходного сумматора порядка, выход памяти для хранения результата подключей к выходной шине разрядов, результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ И ОКРУГЛЕНИЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ | 1992 |

|

RU2018921C1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Операционное устройство | 1985 |

|

SU1367012A1 |

| Устройство для суммирования двух чисел с плавающей запятой | 1988 |

|

SU1529214A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для вычисления экспоненциальной функции | 1986 |

|

SU1465884A1 |

| Устройство для возведения в степень | 1984 |

|

SU1171788A1 |

(pt/e. 1, 5

we.fff вг 83.

m-t

fSH

юо-t №-t

%

fSS t

m-4

fSS-f

-Ш J

fOO-3

Д

1

Авторы

Даты

1993-08-30—Публикация

1989-12-29—Подача