Предлагаемое изобретение относится к вычислительной технике и может быть использовано в системах обмена информацией и для организации общей оперативной .памяти вычислительных систем и многомашинных комплексов с шинной (магистральной) архитектурой в качестве буферного или резервируемого двухканального запоминающего устройства.

Целью изобретения является повышение надежности устройства за счет увеличения достоверности обнаружения ошибок.

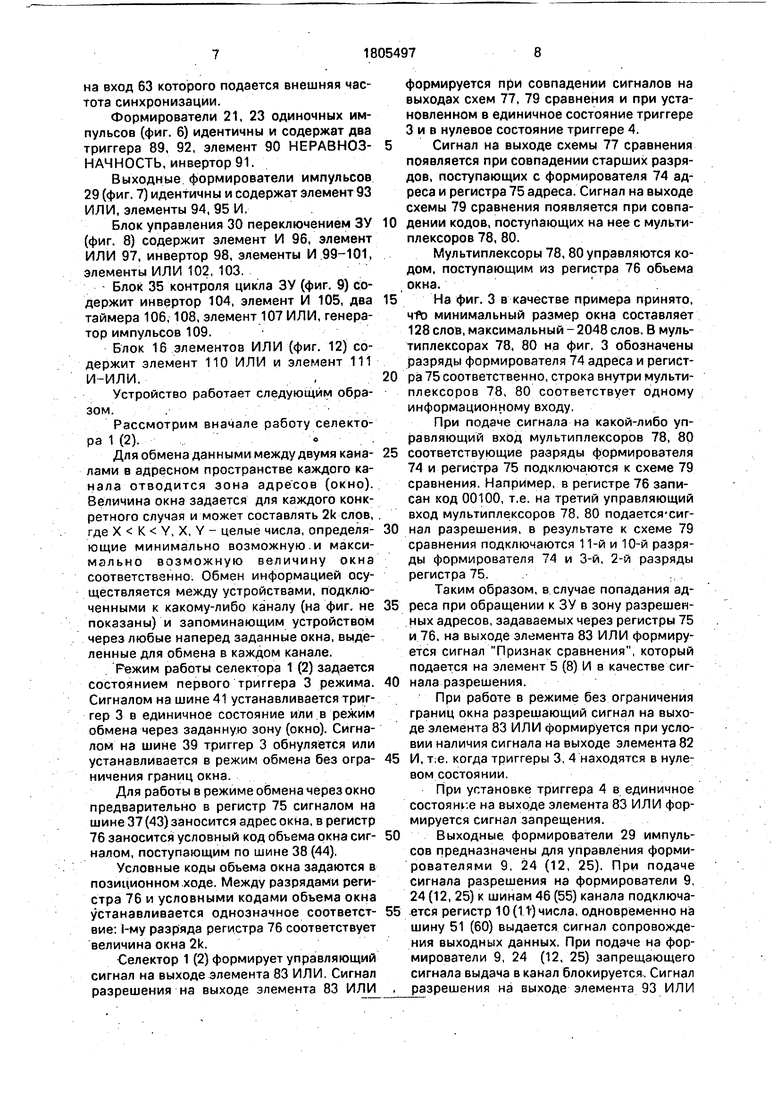

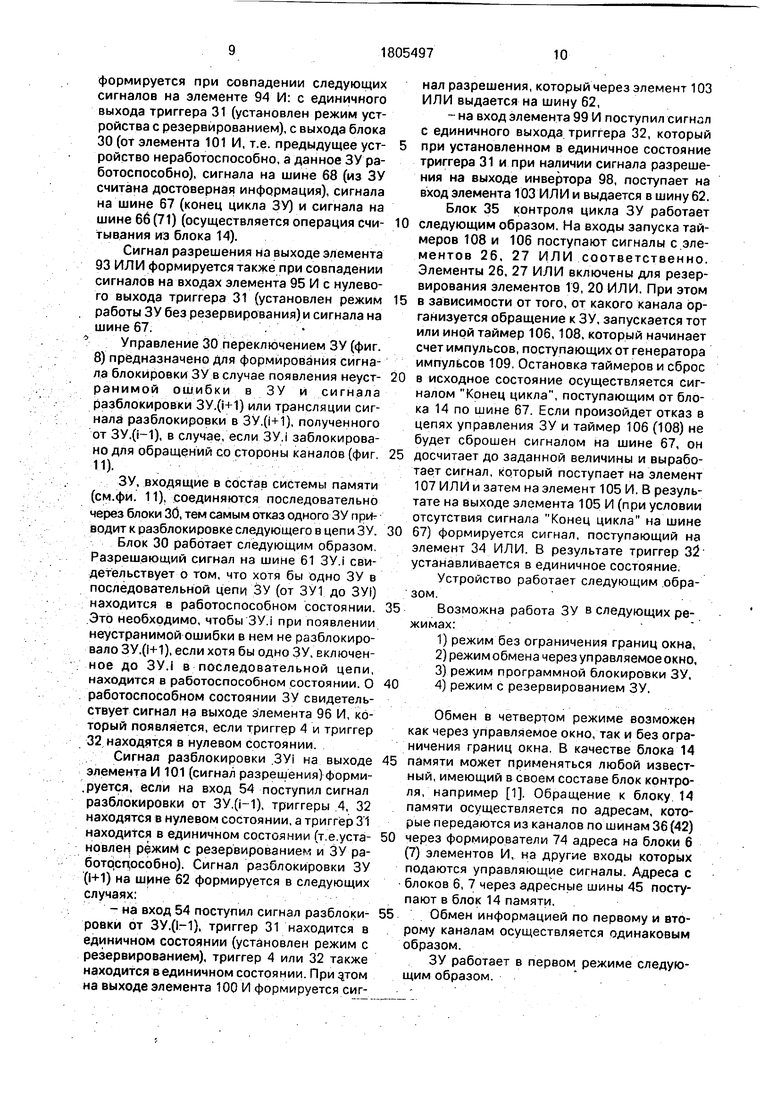

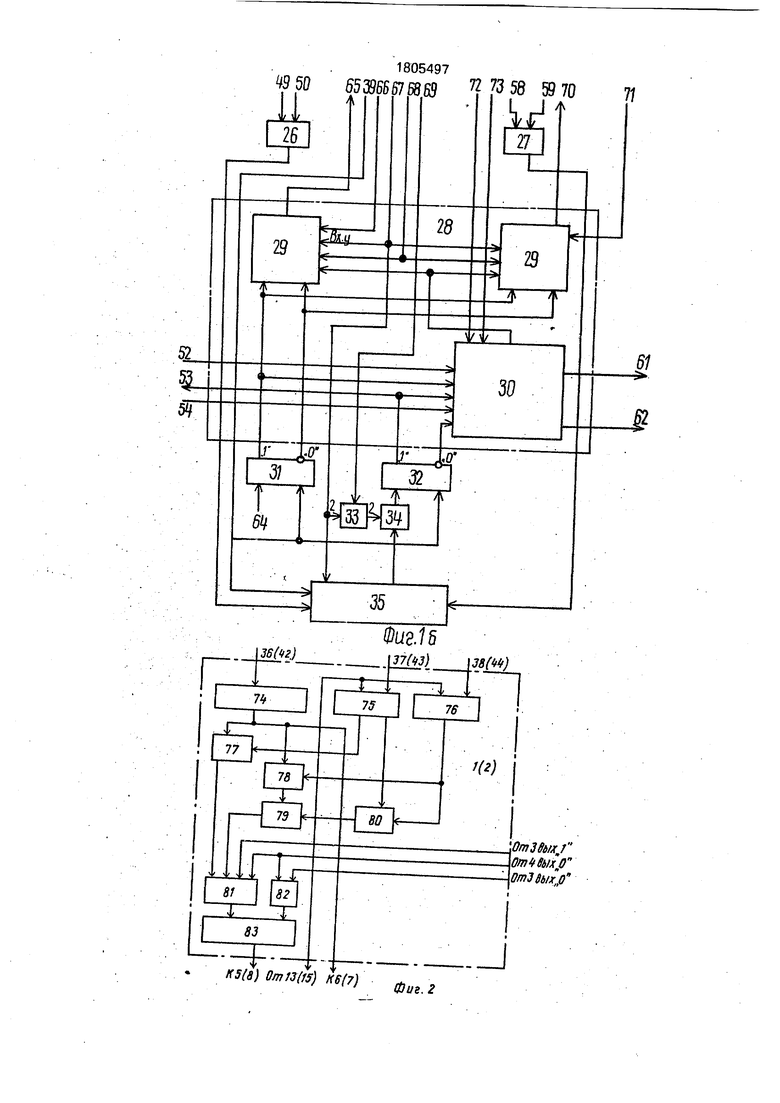

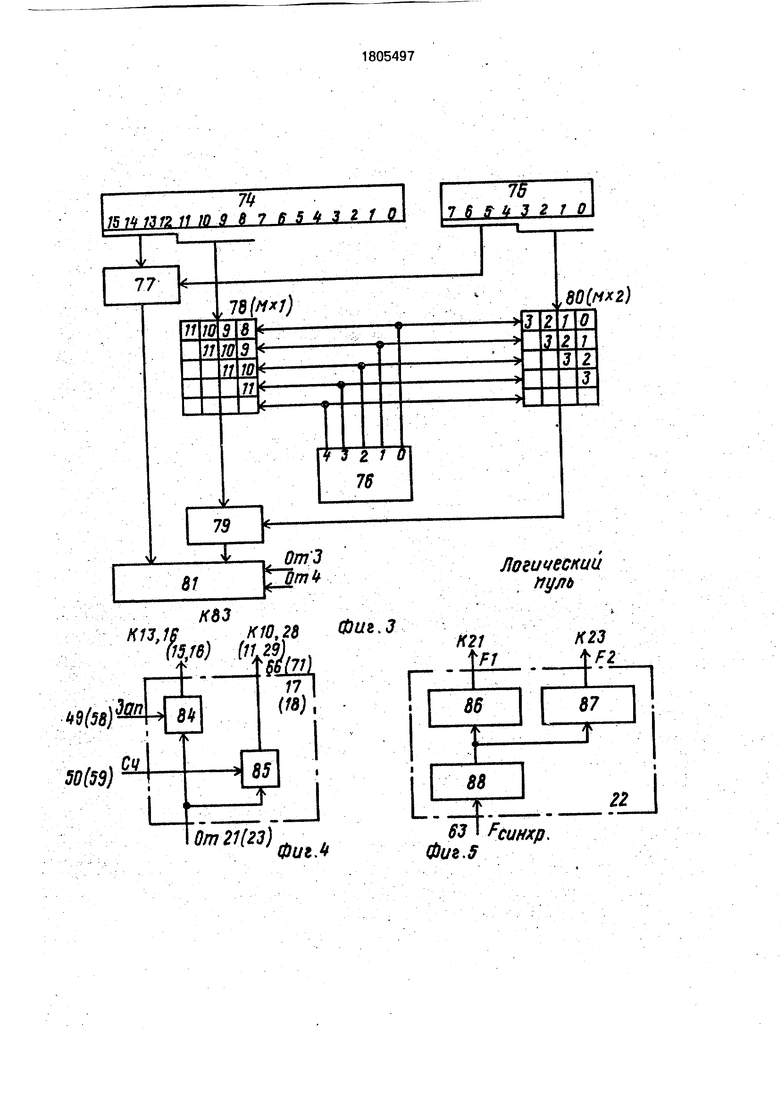

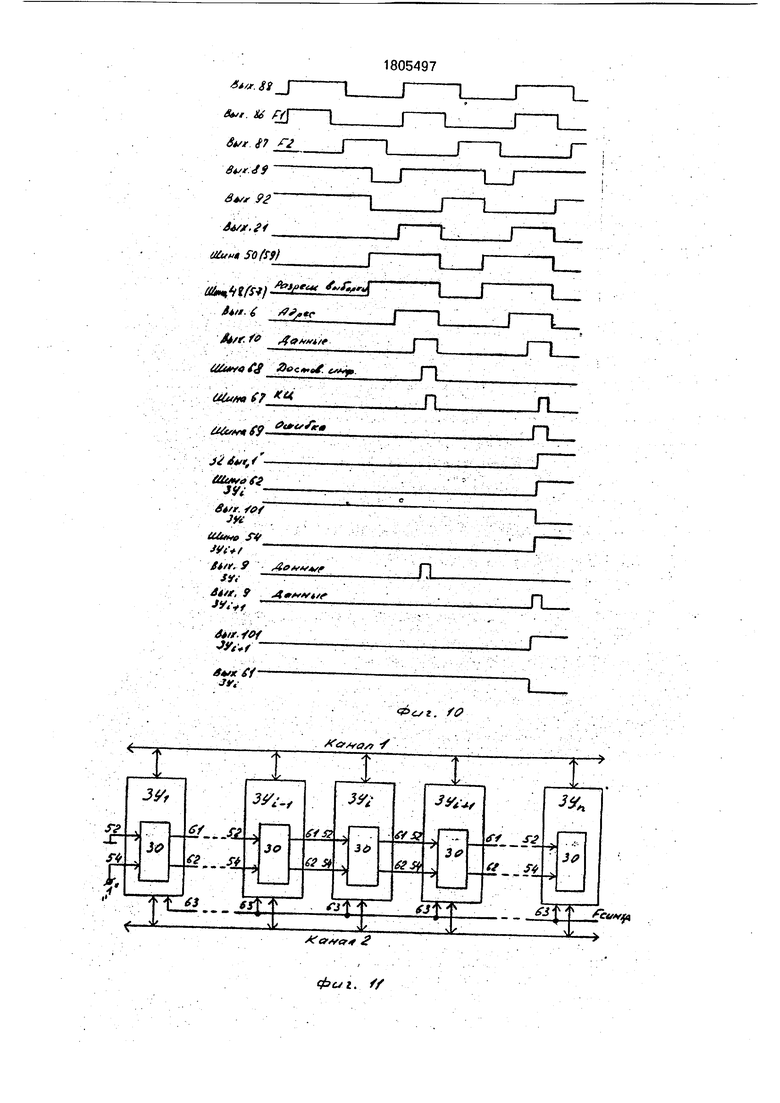

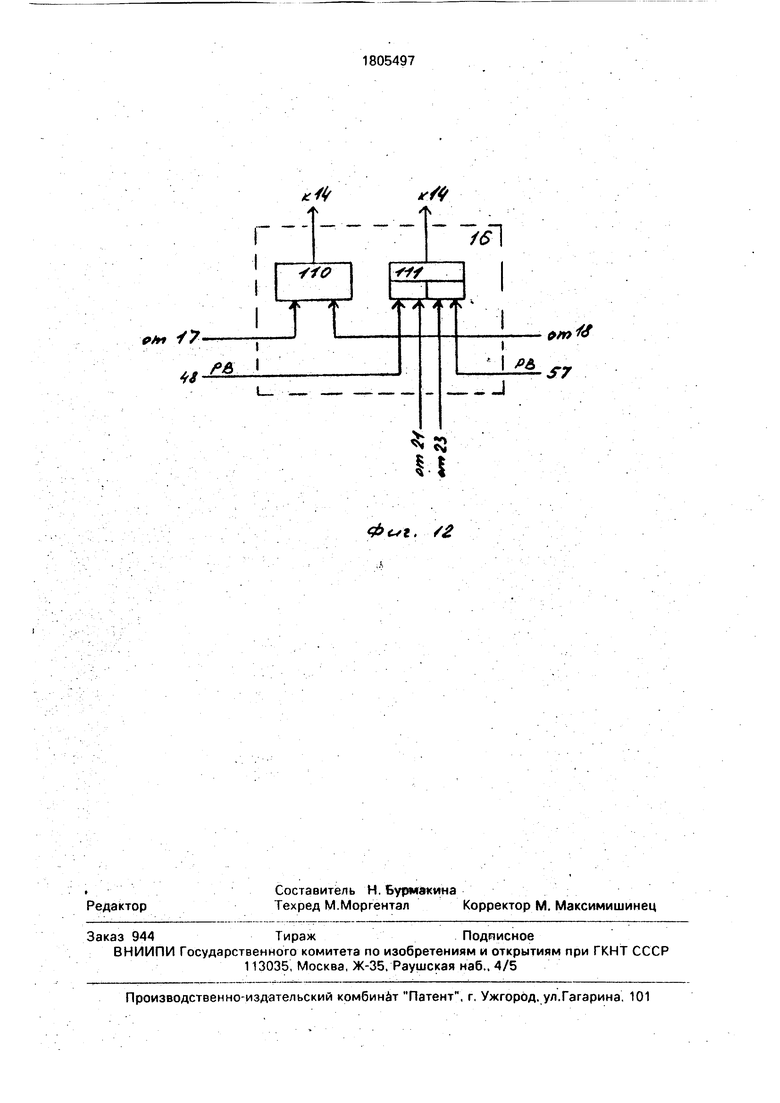

На фиг. 1 (а и б) представлена схема устройства; на фиг. 2 - схема селектора; на фиг. 3 - схема, поясняющая логику работы селектора; на фиг. 4 - схема блока элементов И; на фиг.5 - схема генератора импульсов; на фиг. 6 - схема формирователе одиночных импульсов; на фиг. 7 - схема выходного формирователя импульсов; на фиг. 8 -. схема управления переключением ЗУ; на фиг.9 - схема блока контроля цикла ЗУ; на фиг. 10 - временная диаграмма работы для одного канала; на фиг. 11 - пример построения агрегатированного ЗУ для двухмашинного комплекса; на фиг. 12 - схема блока элементов ИЛИ.

Многоканальное запоминающее устройство содержит два селектора 1, 2, первый триггер 3 режима, первый триггер 4 блокировки, элемент И 5, блоки б, 7 элементов И, элемент И 8, выходной формирователь 9 импульсов первого канала, регистры 10, 11 числа, выходной формирователь 12

00

о ел

Сь

ю

V

импульсов второго канала, входной формирователь 13 импульсов первого канала,блок 14 памяти, входной формирователь 15 импульсов второго канала, блок 16 элементов ИЛИ, блоки 17, 18 элементов И, элементы ,ИЛИ 19, 20, формирователь 21 одиночных импульсов первого канала, генератор 22 импульсов, формирователь 23 одиночных импульсов второго канала, формирователь 24, 25 сигналов сопровождения выходных данных первого и второго каналов соответственно, элементы ИЛИ 26, 27, блок 28 управления, выходные формирователи 29 импульсов, блок управления 30 переключением ЗУ, второй триггер 31 режима, второй триггер 32 блокировки, элемент И 33, элемент ИЛИ 34, блок 35 контроля цикла ЗУ, шины управления, которые включают в себя шины 36 (42) адреса, шины 37 (43) записи начального адреса, шины 38 (44) записи объема зоны, шину 39 начальной установки, шину 40 установки триггера 4 в единичное состояние, шину 41 установки триггера 3 в единичное состояние, адресные шины 45, шины 46 (55) выходных данных,,шины 47(56) входных данных, шины 48 (57) передачи сигнала Разрешение выборки, шины 49 (58) передачи управляющего сигнала, обеспечивающего запись информации в блок 14, шину 50 (5S) передачи управляющего сигнала, обеспечивающего считывание информации из блока 14, шину 51 (60) передачи сигнала сопровождения выходных данных, шину 52 (61) передачи управляющего сигнала от ЗУ(Ы) в ЗУ. (от ЗУ.) в ЗУ.(+1)), сигнализирующего о том, что ЗУ.О-1)-(ЗУ.1) находятся е состоянии Работа, шину 53 передачи управляющего сигнала, сигнализирующего об отказе данного ЗУ, обнаруженного средствами контроля данного ЗУ, шину 54 (62) передачи управляющего сигнала, сигнализирующего об отказе предыдущего (данного) ЗУ, шину 63 передачи частоты синхронизации (Рсинхр.); шину 64 установки триггера 31 в единичное состояние, шину 65

(70) передачи сигнала управления выходными формирователями 9,.24 (12, 25), шину 66

(71) управления (назначение см.в описании блока 17 И), шину 67 передачи сигнала Конец цикла, (КЦ). шину 67 передачи сигнала До стоверная информация, шину 69 передачи сигнала Неисправимая ошибка, шину 72 - единичный выход триггера 4, шину 73 - нулевой выход триггера 4. . Шины 36-38, 46-51 являются шинами первого канала, шины 42-44,55-60 являются шинами второго канала, шины 39-41, 64 являются шинами установки режима работы ЗУ и подключаются к тому каналу, к которому подключен управляющий процессор (не показан), или к пульту управления (не показан).

Вход генератора 22 импульсов является

первым управляющим входом устройства, выходы генератора 22 импульсов соединены соответственно с первыми входами формирователей 21,23 одиночных импульсов. В каждом канале устройства вторые входы

формирователя 21 (23) объединены и подключены к инверсному выходу первого триггера 4 блокировки и к первому управляющему входу селектора 1 (2). Выход формирователя 21 (23) одиночных импульсов соединен с объ5 единенными первыми входами первого элемента 5 (8) И и первого блока 17 (18) элементов И, а третий вход формирователя 21 (23) соединен с выходом первого элемента 19 (20) ИЛИ, первый вход которого и вто0 рой вход первого блока 17 (18) элементов И объединены и являются управляющим входом 50 (59) первой группы устройства, второй вход первого элемента 19 (20) ИЛИ и третий вход первого блока 17 (18) элементов

5 и объединены и являются управляющим входом 49 (58) второй группы устройства.

Первый выход первого блока 17 (18) элементов И соединен с управляющим входом регистра 10 (11) числа, а второй его выход - с

0 управляющим входом входного формирователя 13 (15) импульсов и соответствующим входом первой группы блока 16 элементов ИЛИ, первый выход которого соединен с первым управляющим входом блока 14 па5 мяти, информационные входы которого соединены с информационными входами селекторов 1, 2 и подключены к объединенным выходам входных формирователей 13, 15 импульсов каналов, входы которых явля0 ются соответствующими информационными входами 47, 56 устройства.

Выходы блока 14 памяти соединены с объединенными информационными входами регистров гО, 11 числа каналов, адрес5 ные входы блока 14 памяти соединены с объединенными выходами вторых блоков 6, 7 элементов И каналов. Первые входы второго блока 6 (7) элементов И соединены с первыми выходами селектора t (2), второй

0 вход второго блока 6 (7) элементов И соединен с выходом первого элемента 5 (8) И.

Второй вход первого элемента 5 (8) И соединен со вторым выходом селектора 1 (2). Адресные входы селекторов 1,2 являют5 ся соответствующими адресными входами 36 (42) устройства. Вторые управляющие входы селекторов 1, 2 являются соответствующими управляющими входами 37 (43) третьей группы устройства, третьи управляющие входы - соответствующими управляющими входами 38 (44) четвертой группы устройства, четвертый управляющий вход соединен с прямым выходом первого триггера 3 режима, а пятый управляющий вход - с инверсным выходом первого триггера 3 5 режима, установочный вход которого является вторым управляющим входом 41 устройства.

Входы начальной установки первого триггера 3 режима ипервоготриггера4бло- 10 кировки объединены и являются третьим управляющим входом 39 устройства.

Установочный вход первого триггера 4 блокировки является четвертым управляющим входом 40 устройства.15

Выход формирователя 24 (25) сигнала сопровождения является соответствующим управляющим выходом 51 (60) устройства.

Информационными выходами 46, 55 устройства являются соответствующие выхо- 20 ды формирователя 9, 12.

Информационный вход выходного формирователя 9 (12) соединен с выходом регистра 10(11)числа канала, Управляющий вход выходного формирователя 9 (1.2) и 25 вход формирователя 24 (25) сигнала сопровождения объединены и подключены к соответствующему выходу группы блока 28 управления.

Вход управления выходными формиро- 30 вателями 29 импульсов, второй вход второго элемента 33 .И и первый вход блока 35 контроля цикла ЗУ объединены и соединены со вторым выходом блока 14 памяти, первый выход которого соединен с первым 35 входом второго элемента 33 И, выход которого соединен со вторым входом третьего элемента 34 ИЛИ, первый вход которого соединен с выходом блока 35 контроля цикла ЗУ, второй вход которого, вход начальной 40 установки блока 14 памяти, входы сброса второго триггера 31 режима и второго триггера блокировки объединены и подключены к третьему управляющему входу 39 устройства. :..45

Первые и вторые входы второго элемен- .та 26 (27) ИЛИ соединены с соответствующими управляющими входами 49 (58), 50(59) второй и первой групп устройства. Выходы второго элемента 26 (27) ИЛИ канала под- 50 ключейы к соответствующему входу блока 35 контроля цикла ЗУ.

Установочные входы второго триггера 31 режима и второго триггера 32 блокировки соответственно являются пятым управля- 55 ющим входом 64 устройства и подключены к выходу третьего элемента 34 ИЛИ.

Прямой выход второго триггера 31 режима соединен с первым входом управления 30 переключением блока 28 управления.

Первые входы управления выходными формирователями 29 блока 28 управления соединены с инверсным выходом второго триггера 31 режима, прямой выход второго триггера 32 блокировки соединен со вторым входом управления 30 переключением блока 28 управления и является первым управляющим выходом 53 устройства, инверсный выход второго триггера 32 блокировки соединен с третьим входом управления 30 пе- реключением блока 28 управления, четвертый вход управления 30 переключением которого является шестым управляющим входом 52 устройства, седьмым управляющим входом которого является пятый вход управления 30 переключением блока 28 управления, первый выход которого является вторым управляющим выходом 61 устройства, третьим управляющим выходом которого является третий выход 62 блока 28 управления, шестой вход управления 30 переключением которого соединен с прямым выходом первого триггера А блокировки, а седьмой вход - с инверсным выходом первого триггера 4 блокировки. Вторые входы управления выходными формирователями 29 соединены с третьим управляющим выходом блока 14 памяти.

Первый выход первого блока 17 (18) элементов И канала подключен к соответствующему входу управления выходными формирователями 29 импульсов блока 28 управления.

Выход формирователя 21 (23) одиночных импульсов канала соединен с соответствующим входом второй группы блока элементов 16 ИЛИ, входы третьей группы . которого являются соответствующими управляющими входами 48 (57) пятой группы устройства.

Второй выход блока элементов 16 ИЛИ соединен со вторым управляющим входом блока 14 памяти.

Селекторы 1, 2 полностью идентичны (фиг. 2) и содержат формирователь 74 адреса, регистр 75 адреса, регистр 76 объема зоны, схемы 77, 79 сравнения, мультиплексоры 78,80, элементы И 81,82, элемент ИЛИ 83.

На фиг. 3 приведена подробная схема части селектора 1 (2), поясняющая логику его работы.

На фиг. 4 приведена схема блоков 17,18 элементов И, которые идентичны и содержат элементы 84,85 И.

Генератор 22 импульсов (фиг.5) содержит одновибраторы 86, 87 и генератор 88,

на вход 63 которого подается внешняя частота синхронизации.

Формирователи 21, 23 одиночных импульсов (фиг. 6) идентичны и содержат два триггера 89, 92, элемент 90 НЕРАВНОЗНАЧНОСТЬ, инвертор 91.

Выходные формирователи импульсов 29 (фиг. 7) идентичны и содержат элемент 93 ИЛИ, элементы 94, 95 И,

Блок управления 30 переключением ЗУ (фиг. 8) содержит элемент И 96, элемент ИЛИ 97, инвертор 98, элементы И 99-101, элементы ИЛИ 102, 103.

Блок 35 контроля цикла ЗУ (фиг. 9) содержит инвертор 104, элемент И 105, два таймера 106,108, элемент 107 ИЛИ, генератор импульсов 109.

Блок 16 элементов ИЛИ (фиг. 12) содержит элемент 110 ИЛИ и элемент 111 И-ИЛИ.

Устройство работает следующим образом. ..- .-

Рассмотрим вначале работу селекто- ра1(2).с

Для обмена данными между двумя каналами в адресном пространстве каждого канала отводится зона адресов (окно). Величина окна задается для каждого конкретного случая и может составлять 2k слов, где X К Y, X, Y - целые числа, определяющие минимально возможную.и максимально возможную величину окна соответственно. Обмен информацией осуществляется между устройствами, подключенными к какому-либо каналу (на фиг, не показаны) и запоминающим устройством через любые наперед заданные окна, выделенные для обмена в каждом канале.

Режим работы селектора 1 (2) задается состоянием первого триггера 3 режима. Сигналом на шине 41 устанавливается триггер 3 в единичное состояние или в режим обмена через заданную зону (окно). Сигналом на шине 39 триггер 3 обнуляется или устанавливается в режим обмена без ограничения границ окна.

Для работы в режиме обмена через окно предварительно в регистр 75 сигналом на шине 37 (43) заносится адрес окна, в регистр 76 заносится условный код объема окна сигналом, поступающим по шине 38 (44).

Условные коды объема окна задаются в позиционном ходе. Между разрядами регистра 76 и условными кодами объема окна устанавливается однозначное соответствие: i-му разряда регистра 76 соответствует величина окна 2k.

Селектор 1 (2) формирует управляющий сигнал на выходе элемента 83 ИЛИ. Сигнал разрешения на выходе элемента 83 ИЛИ

формируется при совпадении сигналов на выходах схем 77, 79 сравнения и при установленном в единичное состояние триггере 3 и в нулевое состояние триггере 4.

Сигнал на выходе схемы 77 сравнения появляется при совпадении старших разрядов, поступающих с формирователя 74 адреса и регистра 75 адреса. Сигнал на выходе схемы 79 сравнения появляется при совпа0 дении кодов, поступающих на нее с мультиплексоров 78, 80.

Мультиплексоры 78, 80 управляются кодом, поступающим из регистра 76 объема окна. .

5 На фиг. 3 в качестве примера принято, 4fo минимальный размер окна составляет 128 слов, максимальный - 2048 слов. В мультиплексорах 78, 80 на фиг. 3 обозначены разряды формирователя 74 адреса и регист0 ра 75 соответственно, строка внутри мультиплексоров 78, 80 соответствует одному информационному входу.

При подаче сигнала на какой-либо управляющий вход мультиплексоров 78, 80

5 соответствующие разряды формирователя 74 и регистра 75 подключаются к схеме 79 сравнения. Например, в регистре 76 записан код 00100, т.е. на третий управляющий вход мультиплексоров 78, 80 подается-сиг0 нал разрешения, в результате к схеме 79 сравнения подключаются 11-й и 10-й разряды формирователя 74 и 3-й, 2-й разряды регистра 75.

Таким образом, в случае попадания ад5 реса при обращении к ЗУ в зону разрешенных адресов, задаваемых через регистры 75 и 76, на выходе элемента 83 ИЛИ формируется сигнал Признак сравнения, который подается на элемент 5 (8). И в качестве сиг0 нала разрешения.

При работе в режиме без ограничения границ окна разрешающий сигнал на выходе элемента 83 ИЛИ формируется при условии наличия сигнала на выходе элемента 82

5 И, т;е. когда триггеры 3, 4 находятся в нулевом состоянии.

При установке триггера 4 в единичное состояние на выходе элемента 83 ИЛИ формируется сигнал запрещения.

0 Выходные формирователи 29 импульсов предназначены для управления формирователями 9, 24 (12, 25). При подаче сигнала разрешения на формирователи 9, 24 (12, 25) к шинам 46 (55) канала подключа5 ется регистр 10 (1t) числа, одновременно на шину 51 (60) выдается сигнал сопровождения выходных данных, При подаче на формирователи 9, 24 (12, 25) запрещающего сигнала выдача в канал блокируется.. Сигнал , разрешения на выходе элемента 93 ИЛИ

формируется при совпадении следующих сигналов на элементе 94 И: с единичного выхода триггера 31 (установлен режим устройства с резервированием), с выхода блока 30 (от элемента 101 И, т.е. предыдущее уст- 5 ройство неработоспособно, а данное ЗУ работоспособно), сигнала на шине 68 (из ЗУ считана достоверная информация), сигнала на шине 67 (конец цикла ЗУ) и сигнала на шине 66 (71) (осуществляется операция счи- 10 тывания из блока 14).

Сигнал разрешения на выходе элемента 93 ИЛИ формируется также при совпадении сигналов на входах элемента 95 И с нулевого выхода триггера 31 (установлен режим 15 работы ЗУ без резервирования) сигнала на шине 67.. Управление 30 переключением ЗУ (фиг. 8) предназначено для формирования сигнала блокировки ЗУ в случае появления неуст- 20 ранимой ошибки в ЗУ И сигнала разблокировки ЗУ.(1+1) или трансляции сигнала разблокировки в ЗУ.(+1), полученного от ЗУ.(|-1), в случае, если ЗУ. заблокировано для обращений со стороны каналов (фиг. 25

ЗУ, входящие в состав системы памяти

(см.фи. 11), соединяются последовательно через блоки 30, тем самым отказ одного ЗУ прй водит к разблокировке следующего в цеп и ЗУ. 30

Блок 30 работает следующим образом. Разрешающий сигнал на шине 61 ЗУ. свидетельствует о том, что хотя бы одно ЗУ в последовательной цели ЗУ (от ЗУ1 до ЗУ) находится в работоспособном состоянии. 35 .Это необходимо, чтобы ЗУ. при появлении неустранимой ошибки в нем не разблокировало ЗУ.(1+1), если хотя бы одно ЗУ, включен- ное до ЗУ. в последовательной цепи, находится в работоспособном состоянии. О 40 работоспособном состоянии ЗУ свидетельствует сигнал на выходе элемента 96 И, который появляется, если триггер 4 и триггер 32 находятся в нулевом состоянии.

Сигнал разблокировки ЗУ на выходе 45 элемента И 101 (сигнал разрешения) форми- .руется, если на вход 54 поступил сигнал разблокировки от ЗУ.(1-1), триггеры 4, 32 находятся в нулевом состоянии, а триггер 31 находится в единичном состоянии (т.е.уста- 50 новлен режим с резервированием и ЗУ ра- ботрслюсобно). Сигнал разблокировки ЗУ (i+1) на шине 62 формируется в следующих случаях:

- на вход 54 поступил сигнал разблоки- 55 ровки от ЗУ.(1-1). триггер 31 находится в единичном состоянии (установлен режим с резервированием), триггер 4 или 32 также находится в единичном состоянии. При адом на выходе элемента 100 И формируется сигнал разрешения, который через элемент 103 ИЛИ выдается на шину 62,

- на вход элемента 99 И поступил сигнал с единичного выхода триггера 32, который при установленном в единичное состояние триггера 31 и при наличии сигнала разрешения на выходе инвертора 98, поступает на вход элемента 103 ИЛИ и выдается в шину 62.

Блок 35 контроля цикла ЗУ работает следующим образом. На входы запуска таймеров 108 и 106 поступают сигналы с элементов 26, 27 ИЛИ соответственно. Элементы 26, 27 ИЛИ включены для резервирования элементов 19, 20 ИЛИ. При этом в зависимости от того, от какого канала организуется обращение к ЗУ, запускается тот или иной таймер 106,108, который начинает счет импульсов, поступающих от генератора импульсов 109, Остановка таймеров и сброс в исходное состояние осуществляется сигналом Конец цикла, поступающим от блока 14 по шине 67. Если произойдет отказ в цепях управления ЗУ и таймер 106 (108) не будет сброшен сигналом на шине 67, он досчитает до заданной величины и выработает сигнал, который поступает на элемент 107 ИЛ И и затем на элемент 105 И. В результате на выходе элемента 105 И (при условии отсутствия сигнала Конец цикла на шине 67) формируется сигнал, поступающий на элемент 34 ИЛИ. В результате триггер 32 устанавливается в единичное состояние.

Устройство работает следующим .образом.

Возможна работа ЗУ в следующих режимах:

Т) режим без ограничения границ окна,

2) режим обмена через управляемое окно,

3) режим программной блокировки ЗУ.

4) режим с резервированием ЗУ.

Обмен в четвертом режиме возможен как через управляемое окно, так и без ограничения границ окна. В качестве блока 14 памяти может применяться любой известный, имеющий в своем составе блок контроля, например 1. Обращение к блоку. 14 памяти осуществляется по адресам, которые передаются из каналов по шинам 36(42) через формирователи 74 адреса на блоки 6 (7) элементов И, на другие входы которых подаются управляющие сигналы. Адреса с блоков 6, 7 через адресные шины 45 поступают в блок 14 памяти.

Обмен информацией по первому и второму каналам осуществляется одинаковым образом.

ЗУ работает в первом режиме следующим образом.

Перед началом работы ЗУ устанавливается в исходное состояние. При этом обнуляются триггеры 3, 4. 31, 32, блок 14 сигналом на шине 39, обнуляются также таймеры 106, 108 блока 35. Генератор 22 вырабатывает две серии непересекающихся импульсов (фиг. 10), длительность которых одинакова и определяется временем цикла записи-считывания блока 14.

Рассмотрим работу первого канала (в скобках указываются блоки и шины для второго канала). Код адреса слова поступает на вход 36 (42). Одновременно на вход 49 (58) записи или вход 50 (59) считывания, а также на вход 48 (57) разрешения выборки поступают сигналы управления. Сигнал записи на шине 49 (58) или считывания на шине 50 (59) через элемент 19 (20) ИЛ И поступает на вход формирователя 21 (23) и разрешает формирование одиночного импульса из серии F1(F2), с помощью которого на выходе блока 6 (7) элементов И формируется адрес обрабатываемого слова. Сигнал на шине 48 (57) поступает на вход блока 16 элементов ИЛИ, а с его второго выхода (выход элемента 111) - на вход разрешения выборки блока 14.

Одиночный импульс с выхода формирователя 21 (23) поступает на управляющий вход блока 6 (7) элементов И через элемент 5 (8) И, на второй вход которого из селектора 1 (2) подается разрешающий сигнал, Одновременно при наличии сигнала Запись на входе 49 (58) блока 17 (18) через формирователь 13 (15) импульсов на информационный вход блока 14 памяти устанавливается обрабатываемое слово, а на управляющий вход, блока 14 через блок 16 элементов ИЛИ - код операции Запись (см.фиг. 12, элемент 110 ИЛИ).

При наличии сигнала Считывание на входе 50 (59) на управляющем входе блока 14 сохраняется код операции Считывание, а сигналом с выхода 66 (71) блока 17 (18) разрешается запись обрабатываемого слова с информационного выхода блока 14 в регистр 10 (11) числа. Если на управляющем входе выходного формирователя 9 (12) присутствует сигнал разрешения, то регистр 10 (11) подключается к каналу. Одновременно с выдачей данных в канал выдается сигнал сопровождения данных через формирователь 24 (25) на шину 51 (60).

Разрешающий сигнал на управляющем входе формирователя 13 (15) поступает из соответствующего выходного формирователя 28 импульсов, в котором в данном режиме формируется из сигнала Конец цикла (шина 67) на элементе 95 И блока 28 (29).

Устройство работает во втором режиме следующим образом.

Перед началом работы устройство устанавливается в исходное состояние: обнуляются триггеры 3,4, 31,32, блок 14 и таймеры 106, 108 блока 35 сигналом на шине 39, в селекторы 1,2 заносятся начальный адрес в регистры 75 и величина зоны в регистры 76. Затем осуществляется установка режима с

помощью сигнала на шине 41.

Алгоритм обмена данными во втором режиме полностью совпадает с описанным для первого режима. Разница заключается в следующем. Разрешающий сигнал на вторрй вход элемента 5И подается только в том случае, когда код адреса входит в разрешенную зону адресов при обращении по соответствующему каналу Разрешенная зона адресов (окно) задается регистрами 75, 76

селектора 1 (2). В данном режиме включаются в работу схемы 77, 79 сравнения, мультиплексоры 78, 80 и элемент И 81.

Рассмотрим работу ЗУ в третьем режиме. Данный режим используется для программной блокировки какого-либо ЗУ, входящего в систему памяти (см.фиг.11), Этот режим может использоваться для резервирования каких-либо подсистем вычислительных систем с программным

переключением подсистем на резерв. При этом одно ЗУ работает, другое - заблокировано (при кратности резервирования равным 2). В случае отказа первого ЗУ, разблокируется второе. При этом оно может быть настроено

на адреса первого ЗУ (см.описание селекто: ра1(2)).

Третий режим может использоваться также при работе всей системы памяти (фиг. 11) в четвертом режиме. Режим устанавливается, если при предварительном программном тестировании ЗУ перед работой зафиксирована его неработоспособность. Для установки режима по шине 41 выдается в устройство сигнал, устанавливающий

триггер 4 программной блокировки в единичное состояние. При этом в селекторах 1, 2 вырабатывается сигнал, блокирующий элементы 5, 8 И. Кроме того, блокируются формирователи 21, 23.

Таким образом, в третьем режиме ЗУ заблокировано и не участвует в работе в системе памяти (фиг. 11),

Рассмотрим работу ЗУ в четвертом режиме. Перед началом работы ЗУ приводится

в исходное состояние, как описано выше. Затем осуществляется установка режима подачей сигнала по шине 64. Кроме того, может быть установлен в единичное состояние или нет триггер 3. Обработка адреса в

селекторах 1, 2 осуществляется в данном режиме таким же образом, как в первом режиме, если триггер 3 установлен в нулевое состояние, или как во втором режиме, если триггер 3 установлен в единичное состояние.

В данном режиме все ЗУ, входящие в систему памяти (фиг. 11) настраиваются на одно адресное пространство, т.е. обрабатываемое слово записывается (считывается) во все ЗУ одновременно по одному адресу.

Работа в данном режиме осуществляется таким образом, что одно слово записывается одновременно во все ЗУ (за исключением ЗУ, которые заблокированы).

Считывание осуществляется также одновременно их всех ЗУ, только выдача слова в соответствующий канал разрешается одному ЗУ, тому ЗУ, которое имеет меньший номер (см.фиг. 11) среди всех работающих ЗУ. Таким образом, приоритет включения ЗУ убывает слева направо.

Если во время работы возникает неустранимая ошибка в работе какого-либо ЗУ, то данное ЗУ блокируется, т.е. отключается от каналов для выдачи информации в каналы, а следующее в цепочке ЗУ разблокируется, т.е. подключается к каналам при считывании данных. Если же между отказавшим в данный момент ЗУ и ближайшим работоспособным в цепочке ЗУ имеется неработающее ЗУ, то организуется обход неработающего ЗУ и подключение к каналам ближайшего работающего ЗУ.

.. Рассмотрим работу ЗУ в четвертом режиме подробнее.

Алгоритм обработки данных полностью совпадает с описанным выше для трех режимов. Особенности работы в данном режиме проявляются в случае появления при считывании неустранимой ошибки или отказе в цепях управления устройством.

При появлении неустранимой ошибки блок 14 вырабатывает сигнал на шине 69. В результате с поступлением сигнала на шине 67 Конец цикла срабатывает элемент ЗЗИ

и через элемент 34 ИЛИ. установится в единичное состояние триггер 32. Триггер 32 устанавливается в единичное состояние через элемент 34 ИЛИ с поступлением сигнала от блока 35, который вырабатывается при отказе цепей управления ЗУ.

Рассмотрим случай, когда работает ЗУ 1, т.е. разблокировано для считывания. На вход 52 подается запрещающий потенциал, на вход 54 - разрешающий.

. Сигнал с единичного выхода триггера 32 поступает на вход элемента 99 И (на других входах элемента 99 И - разрешающие- потенциалы) и через элемент 103 ИЛИ выдается по шине 62 на шину 54 ЗУ2.

Так как ЗУ1 стало не работоспособным, т.е. триггер 32 блокировки находится в еди- 5 ничном состоянии, на выходе элемента 96 И формируется запрещающий потенциал, который через элемент 97 ИЛИ выдается на шину 61 и поступает на вход 52 ЗУ2. Запрещающий сигнал с выхода элемента 96 И

0 поступает также на вход элемента 101 И, В результате на его выходе появляется запрещающий сигнал, который поступает на выходные формирователи 29 и блокирует в них элемент 94И. В результате блокируются вы5 ходные формирователи 9, 12 сигналами на шинах 65, 70.

Рассмотрим работу ЗУ2 после того, как в ЗУ1 возникла неустранимая ошибка. До возникновения ошибки данные в каналы вы0 давались из ЗУ1, ЗУ2 - заблокировано для выдачи данных. На вход 52 ЗУ2 поступает запрещающий сигнал, на вход 54-разрешающий. С поступлением в ЗУ2 сигнала на шине 54 на выходе элемента 101 И форми5 руется сигнал разрешения, т.к, на втором и третьем входах элемента 101 И - разрешающие потенциалы.

Разрешающий сигнал с выхода элемента 101 И поступает на блоки 28,29, в которых

0 разрешают прохождение сигнала Конец цикла (шина 67, фиг. 8). Таким образом, слово данных выдается в соответствующий канал (на шины 46 или 55) из ЗУ2.

Рассмотрим случай, когда произошла

5 неустранимая ошибка в ЗУ1, при этом ЗУ2 не работает (триггер 4 или триггер 32 находятся в единичном состоянии). Сигнал, сформировавшийся на выходе 62 ЗУ1, поступает на вход 54 ЗУ2, в котором через

0 элемент 1000 И и элемент 103 ИЛИ поступает на выход 62, а затем на вход 54 ЗУЗ. . Действия, проходящие в ЗУ 3, аналогичны описанным выше.

Разрешающий потенциал на шине 61

5 будет присутствовать только на выходе ЗУЗ. На временной диаграмме (фиг. 10) приведены два цикла считывания, причем один цик/i выполняется из ЗУ.1, второй - из ЗУ.0+1). Временная диаграмма приведена

0 без учета задержек элементов устройства. Необходимо учитывать, что при переключении ЗУ возможна выдача данных с задержкой. О наличии данных на шинах 46 (55) . сигнализирует сигнал сопровождения на

5 шине 51 (60).

Задержка в выдаче данных а случае появления неустранимой ошибки в каком-либо ЗУ составляет сумму задержек на элементах 33,34.32. 100,103,вЗУ1, 100,103

в ЗУ2 - ЗУ.(п-1),.Ю1 в ЗУп. В наихудшем случае время переключения составляет в зависимости от элементной базы, на которой выполняется устройство, и количества последовательно включенных через блок 30 ЗУ 100 не. не более, т.е. переключение на резервное ЗУ осуществляется практически мгновенно.

Использование предлагаемого ЗУ позволяет агрегатировать вычислительные системы унифицированным устройством, которое позволяет легко перестраивать архитектуру вычислительных систем, организовать простое резервирование запоминающих устройств и других устройств вычислительной Системы. Причем переключение на резерв осуществляется практически мгновенно без привлечения средств операционной системы, а оборудование, используемое на организацию механизма переключения составляет незначительную часть от объема всего ЗУ. Это, в свою очередь, значительно удешевляет устройство и систему памяти в целом. Известно, что в системах с резервирЪванием надежность устройств мажорирования и реконфигурации должны быть хотя бы на порядок выше надежности самих резервируемых устройств. Данное требование значительно перекрывается в предлагаемом техническом решении.

Формула изобретения

Многоканальное запоминающее устройство, содержащее первый селектор, пер- вый триггер режима, первый триггер блокировки, блок памяти, блок элементов ИЛ И генератор импульсов, причем каждый канал устройства содержит первый элемент И, первый и второй блоки элементов И, регистр числа, входной формирователь импульсов, первый элемент ИЛИ, формирователь одиночных импульсов, вход генератора импульсов является первым управляющим входом устройства, выходы генератора импульсов соединены с первыми входами соответствующих формирователей одиночных импульсов каналов, вторые входы которых объединены и подключены к инверсному выходу первого триггера блокировки и к первому управляющему входу первого селектора, выход формирователя одиночных импульсов соединен с объединенными первыми входами первого элемента И и первого блока элементов И, а третий вход формирователя одиночных импульсов соединен с выходом первого элемента ИЛИ, первый вход которого и второй вход первого блока элементов И объединены и являются

управляющим входом первой группы устройства, второй вход первого элемента ИЛИ и третий вход первого блока элементов И объединены и являются управляющим входом второй группы устройства, первый выход первого блока элементов И соединен с управляющим входом регистра числа, второй выход первого блока элементов И соединен с управляющим входом входного

формирователя импульсов и соответствующим входом первой группы блока элементов ИЛИ, первый выход которого соединен с первым управляющим входом блока памяти, информационные входы которого соедин§ны с информационными входами первого селектора и подключены к объединенным выходам вторых формирователей импульсов каналов, входы которых являются соответствующими информационными входами

устройства, выходы блока памяти соединены с объединенными информационными входами регистров числа каналов, адресные входы блока памяти - с объединенными выходами вторых блоков элементов И каналов,

первые входы второго блока элементов И первого канала соединены с первыми выходами первого селектора, второй вход второго блока элементов И соединен с выходом первого элемента И, второй вход первого

элемента И первого канала соединен с вторым выходом первого селектора, адресный вход которого является первым адресным входом устройства, второй управляющий вход первого селектора является первым управляющим входом третьей группы устройства, третий управляющий вход - первым управляющим входом четвертой группы устройства, четвертый управляющий вход - соединен с прямым выходом первого триггера

режима, пятый управляющий вход - с инверсным выходом первого триггера режима, установочный вход которого является вторым, управляющим входом устройства, входы начальной установки первого триггера

режима и первого триггера блокировки объединены и являются третьим управляющим входом устройства, установочный вход первого триггера блокировки является четвертым управляющим входом устройства, о тличающееся тем, что, с целью повышения надежности устройства за счет увеличения достоверности обнаружения ошибок, в него введены блок управления, второй триггер блокировки, второй триггер режима,

второй элемент И, третий элемент ИЛИ, блок контроля цикла ЗУ, причем в каждый канал устройства введены выходной формирователь импульсов, формирователь сигналов сопровождения, второй элемент ИЛИ и

второй селектор во все каналы, кроме первого, второй выход второго селектора соответствующего канала соединен с вторым входом первого элемента И данного канала, информационные входы второго селектора канала подключены к выходам входного формирователя импульсов, адресный вход является соответствующим адресным входом устройства, второй управляющий вход является соответствующим управляющим входом третьей группы устройства, третий управляющий вход - является соответствующим управляющим входом четвертой группы устройства, четвертый управляющий вход - соединен с прямым выходом первого триггера режима, пятый управляющий вход - с инверсным выходом первого триггера режима, выход формирователя сигнала сопровождения является соответствующим управляющим выходом устройства, информационным выходом которого является выход соответствующего выходного формирователя импульсов, информационный вход которого соединен с выходом регистра числа канала, управляющий.вход выходного формирователя импульсов и вход формирователя сигнала сопровржде- ния объединены и подключены к соответствующему выходу группы блока управления, вход управления выходными формировате- лями импульсов которого, второй вход второго элемента И и первый вход блока контроля цикла ЗУ объединены и соединены с вторым выходом блока памяти, первый выход которого соединен с первым входом второго элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, первый вход которого соединен с выходом блока контроля цикла ЗУ, второй вход которого, вход начальной установки блока памяти, входы сброса второго триггера режима и второго триггера блокировки объединены и подключены к третьему управляющему входу устройства, первые и вторые входы второго элемента ИЛИ соеди- нены с соответствующими управляющими входами второй и третьей групп устройства, выход второго элемента ИЛИ канала подключен к соответствующему входу блока

контроля цикла ЗУ, установочные входы второго триггера режима и второго триггера блокировки соответственно являются пятым управляющим входом устройства и подключены к выходу третьего элемента ИЛИ, прямой выход второго триггера режима соединен с первым входом управления переключением блока управления, первый вход управления выходными формирователями импульсов которого соединен с инверсным выходом второго триггера режима, прямой выход второго триггера блокировки соеди- нен с вторым входом управления переключением блока управления и является первым управляющим выходом устройства, инверсный выход второго триггера блокировки соединен с третьим входом управления переключением блока управления, четвертый вход управления переключением которого является шестым управляющим входом устройства, седьмым управляющим входом которого является пятый вход управления переключением блока управления, первый выход которого является вторым управляющим выходом устройства, третьим управляющим выходом которого является третий выход блока управления, шестой вход управления переключением которого соединен с прямым выходом первого триггера блокировки, инверсный выход которого соединен с первым управляющим входом второго селектора и седьмым входом управления переключением блока управления, второй вход управления выходными формирователями импульсов которого соединен с третьим управляющим выходом блока памяти, первый выход первого блока элементов И канала подключен к соответствующему входу управления выходными формирователями импульсов блока управления, выход формирователя одиночных импульсов канала соединен с соответствующим входом второй группы блока элементов ИЛИ, входы третьей группы которого являются соответствующими управляющими входами пятой группы устройства, второй выход блока элементов ИЛИ соединен с вторым управляющим входом блока памяти.

ty-глф U OLge9SUZLЈ9M Ј$9BЈS9 OS &

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема кодированного сигнала изображения | 1989 |

|

SU1686706A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1985 |

|

SU1259342A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Устройство контроля кода счетчика | 1979 |

|

SU815920A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Изобретение относится к области вычислительной техники и может быть использовано в качестве унифицированного блока памяти, предназначенного для агрегатирова- ния резервированной памяти высоконадеж- ных многомашинных вычислительных систем с магистральной архитектурой, к которым предъявляются высокие требования к времени переключения на резерв, в качестве общей оперативной памяти многомашинных систем или в качестве буферной памяти. Изобретение позволяет повысить надежность устройства за счет увеличения достоверности обнаружения ошибок. Устройство содержит селектор, два триггера режима, два триггера блокировки, блок памяти, блок элементов ИЛИ, генератор импульсов, блок управления, два элемента И, блок контроля цикла ЗУ, причем каждый ка нал устройства имеет входной и выходной формирователи импульсов, формирователь сигналов сопровождения, два элемента И, два блока элементов И регистр числа, формирователь одиночных импульсов и второй селектор, кроме первого канала, а также по два элемента ИЛИ в каждом канале. 12 ил, ел

to Zh lb Q h ЈЈ 9Ј Li 9Ј

LMsm

л таъшо j Mgetuo

(Mjitf (ёЩёл 91 ГПф

(гьЩ

LGbSOSl.

фу г..6.

Ы

4

I

ОгпЗПых„1 От Фиг.7

К 9,24 (12,25) 65(70}

9f

4#;W/7«

ШЕ-«Лл

доегад инф. 16В Dm /

Om3Q

(101)

.игтуи. I.

шо

JL

901

(вг)агя

/) n U

Фиг. /2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1417041A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Многоканальное запоминающее устройство | 1984 |

|

SU1251176A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-03-30—Публикация

1990-08-01—Подача