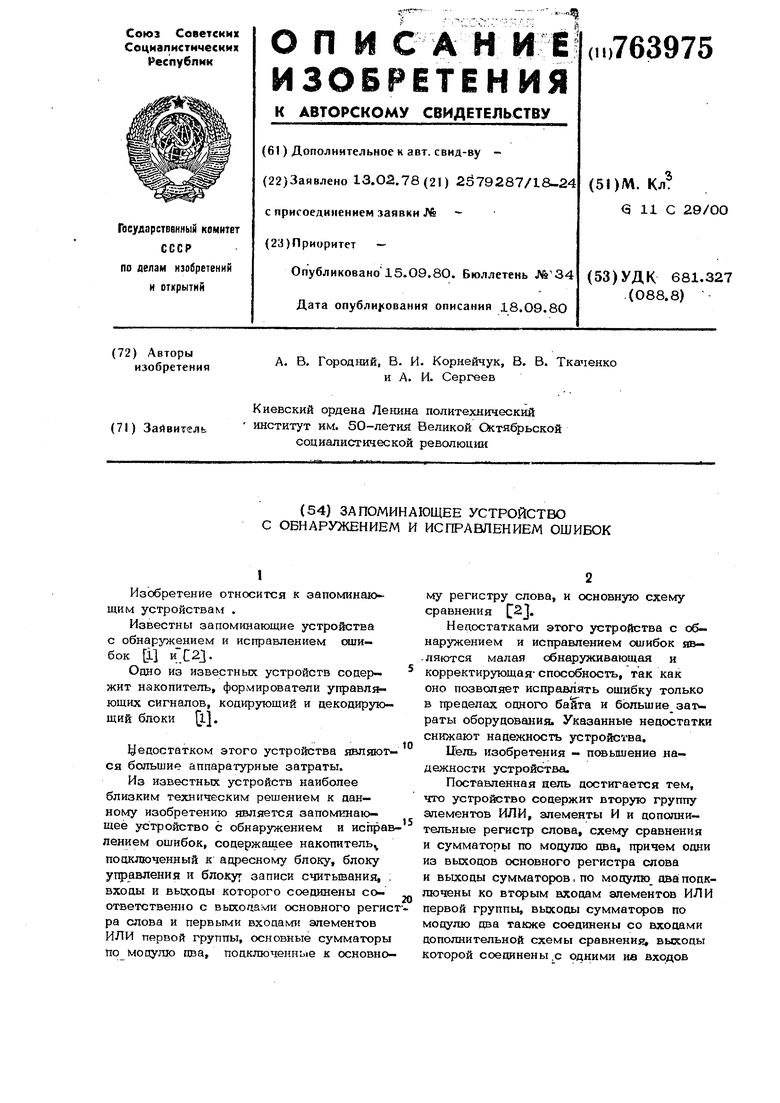

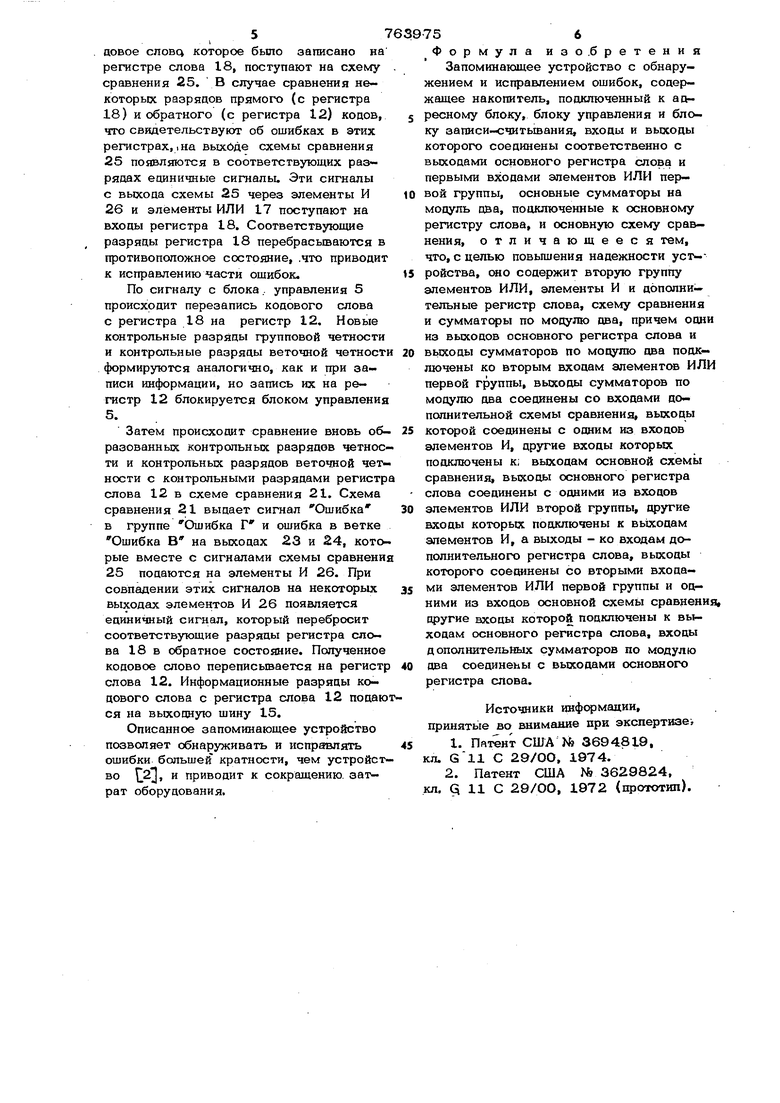

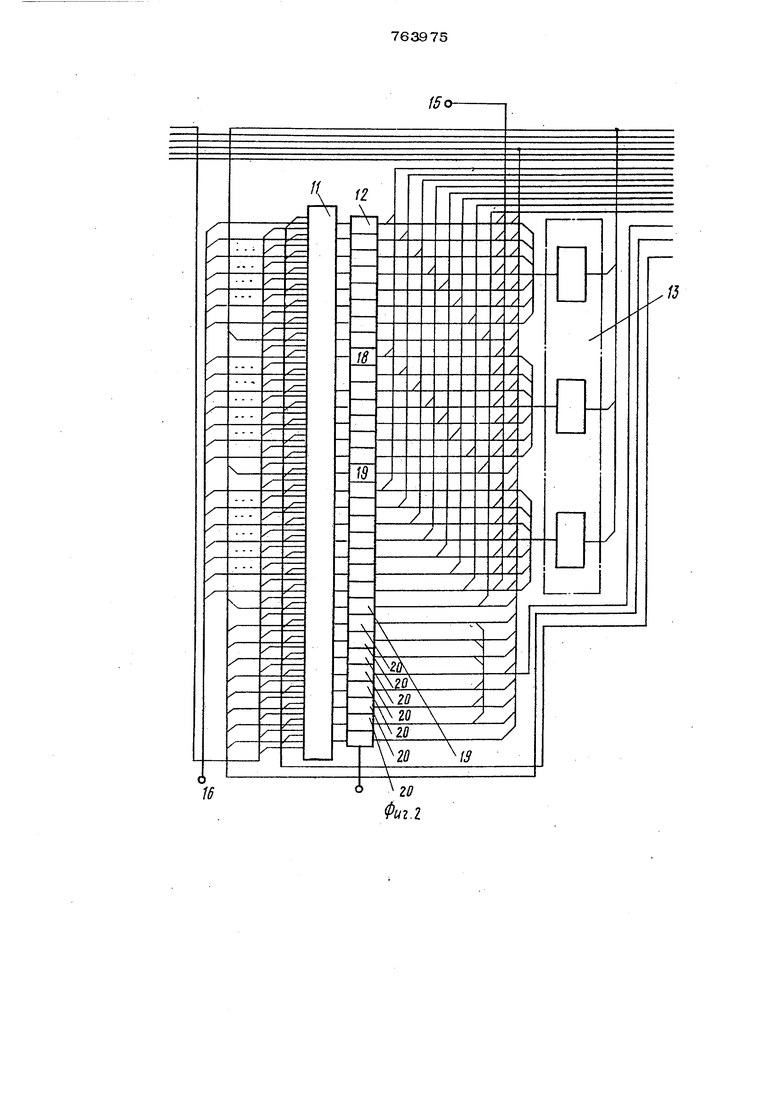

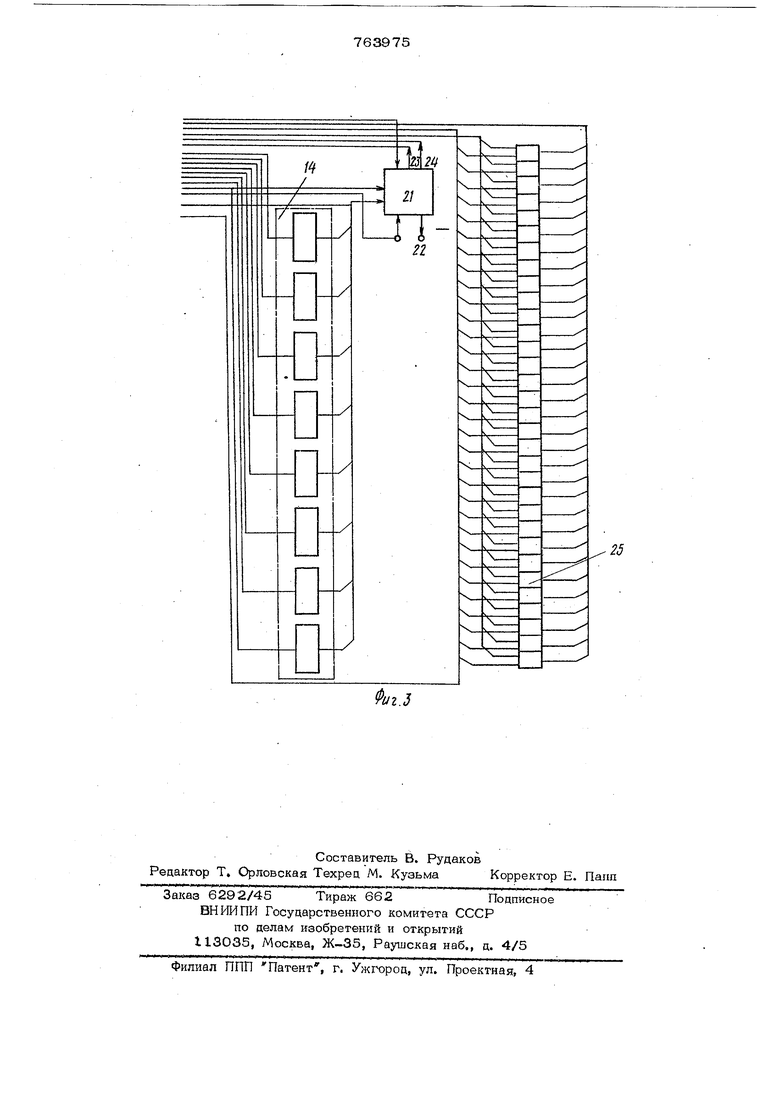

Изобретение относится к аапомина щим устройства 1 . Известны запоминающие устройства с обнаружением и исправлением ошибок i . Одно из известных устройств соцер- жит накопитель, формирователи управляющих сигналов, кодирующий и декодирую щий блоки l. Недостатком этого устройства jmnsnoT ся большие аппаратурные затраты. Из известных устройств наиболее близким техническим решением к данному изобретению является запоминающее устройство с обнаружением и испра лением ошибок, содержащее накопитель поцключенный к адресному блоку, блоку утфавления и блокуг записи считьюания, входы и выходы которого соединены соответственно с выходами основного реги ра слова и первыми входами элементов ИЛИ первой группы, основные сумматоры по модулю два, подключеиньш к основно му регистру слова, и основную схему сравнения . Недостатками этого устройства с обнаружением и исправлением ошибок яв- ляются малая обнаруживающая и корректирующая-способность, так как оно позволяет исправлять ощибку только в пределах одного байта и большие затраты оборудования. Указанные недостатки снижают надежность устройства. Цель изобретения - псюьпиенив надежности устройства. Поставленная цель достигается тем, что устройство содержит вторую группу элементов ИЛИ, элементы И и дополнительные регистр слова, схему сравнения и сумматоры по модулю два, причем одни из выходов основного регистра слова и выходы сумматоров, по модулю два подключены ко втфым входам элементов ИЛИ первой группы, выходы сумматоров по модулю два также соединены со входами дополнительной схемы сравнения, выходы которой соединены.с одними иа входов элементов И, другие входы которых поцк- лючены к выходам основной схемы сравнения, выходы основного регистра слова соединены сг одними из входов элементов ИЛИ второй группы, другие входы которы подключены к выходам элементов И, а вы ходы - ко входам дополнительного регист ра слова, выходы которого соединены со вторыми входами элементов ИЛИ первой группы и одними из входов основной СХе- мы сравнения, другие входы которой подключены к выходам основного регист ра слова, входы дополнительных сумматоров по модулю два с выходами основного регистра слова, На фиГ. 1-3 изображена структурная схема предложенного устройства. Запоминающее устройство содержит (см.фиг. 1-3) накопитель 1, вход 2 которого подключен к выходу адресного блока3, имеющего информационный вход 4, блок управления 5, имеющий входы 6-9, блок 10 записи-считывания, первую группу элементов ИЛИ 11, основ ной регистр слова 12, основные сумма- торы 13 по модулю два, дополнител1эные сумматоры 14 по модулдо два, шину 15 выход информационного слова) шину 16 вход информационного слова, вторую группу элементов ИЛИ 17, дополнительный регистр слова 18. В регистре слова 12 имеются контрольнъю разряды 19 групповой четности и контрольные разряды 2 О веточной четности. ycTpojicTBO также содержит дОпблнительную схему сравнения 21, имеющую выходы 22-24, основную схему сравнени 25, элементы И 26. Выходы блока 10 с первыми входами элементов ИЛИ 11. Одни из выходов регистра слова 12 и выходы сумматоров 13 и 14 подключены ко вторым входам элементов ИЛИ 11. Выходы сумматоров 13 и 14 соединены со входами схемы сравнения 21, выходы которой соединены с одними из входов элементов И 26, сругие входы которых подключены к выходам схемы сравнения 25. Выходы регистра слова 12 соединены с одними из входов эле- , ментов ИЛИ 17, другие входы которых подключены к выходам элементов И 26, а выходы - ко входам регистра 18, выходы которых соединены со вторыми входами элементов ИЛИ 11 и одними из входов схемы сравнения 25, другие входы которой подключены к выходам регистра слова 12. Входы сумматора 14 соединены с выходами регистра слова 12. Запоминающее устройство работает следующим образом. °В режиме записи на шину 16 поступает информационное слово, которое через элементы ИЛИ 11 записывается в информационных разрядах регистра слова 12. Информационные разряды этого регистра условно разделены на группьи Значения каждой из групп поступают на соответствующий сумматор 13, где формируются значения контрольных разрядов 19 групповой четности. Значения четности для каждой из групп разрядов записьшаются через элементы ИЛИ 11 в соответствующие разряды 19 регистра слова 12. Одновременно значения j -X разрядов каждой группы поступают на соответствующий д -и сумматор 14. Значение бита четности для каждой -и ветви подается через элементы ИЛИ 11 в j -и разряд 2О веточной четности . По сигналу с блока управления 5 осуществляется запись закодированного слова (кодового слова) через блок 10 в ячейку накопителя 1, номер которой задан кодом адреса на выходе блока 3. При считывании информации образование всех контрольных разрядов групповойчетности и веточной четности происходит так же.как и при записи, только блок управления 5 блокируетзапись этих разрядов с сумматоров 13 и 14 на регистр слова 12. ftioBiTобработанные контрольные разряды групповой четности и контрольные разряды веточной четности подаются в схему сравнения 21, где осуществляется сравнение образованньк контрольных разрядов групповой четности и веточной четности с первоначальными значениями, которые были записаны в соответствующих разрядах регистра слова 12 при чтении из накопителя 1. несовпадении считанных и вновь образованных контрольных разрядов групповой и веточной четности схема сравнения 21 выдает сигнал Ошибка на выход 24. Если не совпадают р контрольных разрядов веточной четности и один С -и разряд групповой четности, то эта ситуация индицируется схемой сравнения 21 как. пачка ошибок в 8-й группе разряаов, длина которых р. По сигналу Ошибка с выхода 22 схемы сравнения 21 и сигналу с блока управления 5 происходит 1швертирование кодового слова с записью в накопитель , 1 и последующее считывание.; Кодовое слово, считанное с цакопителя 1, и ко- довое слове которое было записано на регистре слова 18, поступают на схему сравнения 25. В случае сравнения некоторых разрядов прямого (с регистра 18) и обратного (с регистра 12) кодов, что свидетельствуют об ошибках в этих регистрах, 1 на вьисбде схемы сравнения 25появляются в соответствующих разрядах единичные сигналы. Эти сигналы с выхода схемы 25 через элементы И 26и элементы ИЛИ 17 поступают на входы регистра 18, Соответствующие разряды регистра 18 перебрасьшаются в противоположное состояние, .что приводит к исправлению части ошибок. По сигналу с блока, управления 5 происходит перезапись кодового слова с регистра 18 на регистр 12. Новые контрольные разряды групповой четности и контрольные разряды веточной четности формируются аналогично, как и при записи информации, но запись их на регистр 12 блокируется блоком управления 5. Затем происходит сравнение вновь образованных контрольных разрядов четноети и контрольных разрядов веточной чет ности с контрольными разрядами регистр слова 12 в схеме сравнения 21. Схема сравнения 21 выдает сигнал Ошибка в группе Ошибка Г и ошибка в ветке Ошибка В на выходах 23 и 24, которые вместе с сигналами схемы сравнения 25 подаются на элементы И 26. При совпадении этих сигналов на некоторых выходах элементов И 26 появляется единичный сигнал, который перебросит соответствующие разряды регистра слова 18 в обратное состояние. Полученное кодовое слово переписьтается на регистр слова 12. Информационные разряды кодового слова с регистра слова 12 подаю ся на выходную шину 15. Описанное запоминающее устройство позволяет обнаруживать и исправлять ошибки большей кратности, чем устройство 2, и приводит к сокращению, затрат оборудования. Формула изо.бретения Запоминающее устройство с обнаружением и исправлением ошибок, содержащее накопитель, подключенный к адресному блоку, блоку управления и блоку записи-чзчитьтания, входы и выходы которого соединены соответственно с выходами основного регистра слова и первыми входами элементов ИЛИ пер- вой группы, основные сумматоры на модуль два, подключенные к основному регистру слова, и основную схему сравнения, отличающееся тем, что, с целью повышения надежности уст ройства, оно содержит вторую группу элементов ИЛИ, элементы И и дополнительные регистр слова, схему сравнения и сумматоры по модулю два, причем одни из выходов основного регистра слова и вьосоды сумматоров по модулю два подк- лючены ко вторым входам элементов ИЛИ первой группы, выходы сумматоров по модулю два соединены со входами дополнительной схемы сравнения, выходы которой соединены с одним из входов элементов И, другие входы которых подключены к; выходам основной схемы сравнения, выходы основного регистра слова соединены с одними из входов элементов ИЛИ второй группы, другие входы которых подключены к вь1ходам элементов И, а выходы - ко входам дополнительного регистра слова, выходы которого соединены со вторыми входа- ми элементов ИЛИ первой группы и одними из входов основной схемы сравнения, другие входы которой подключены к выходам основного регистра слова, входы дополнительных сумматоров по модулю два соединены с выходами основного регистра слова. Источники информации, принятые во внимание при экспертизе, 1. Патент США NJ 3694819, кл. Gll С 29/ОО, 1974. 2. Патент США №3629824, кл. q 11 С 29/00, 1972 (прототип).

r...((rrr

18

17

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1976 |

|

SU639023A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1061176A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1092570A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Оперативное запоминающее устройство с коррекцией информации | 1983 |

|

SU1111206A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Устройство для сдвига информации | 1983 |

|

SU1188783A2 |

101

//

«P

5 3 7.g

Фиг.

W

/

у/

у

У

Ж

У

чУоУ

У

.2g

Л2ГЛ

У2Д

2//

го

Фиг.г

Авторы

Даты

1980-09-15—Публикация

1978-02-13—Подача