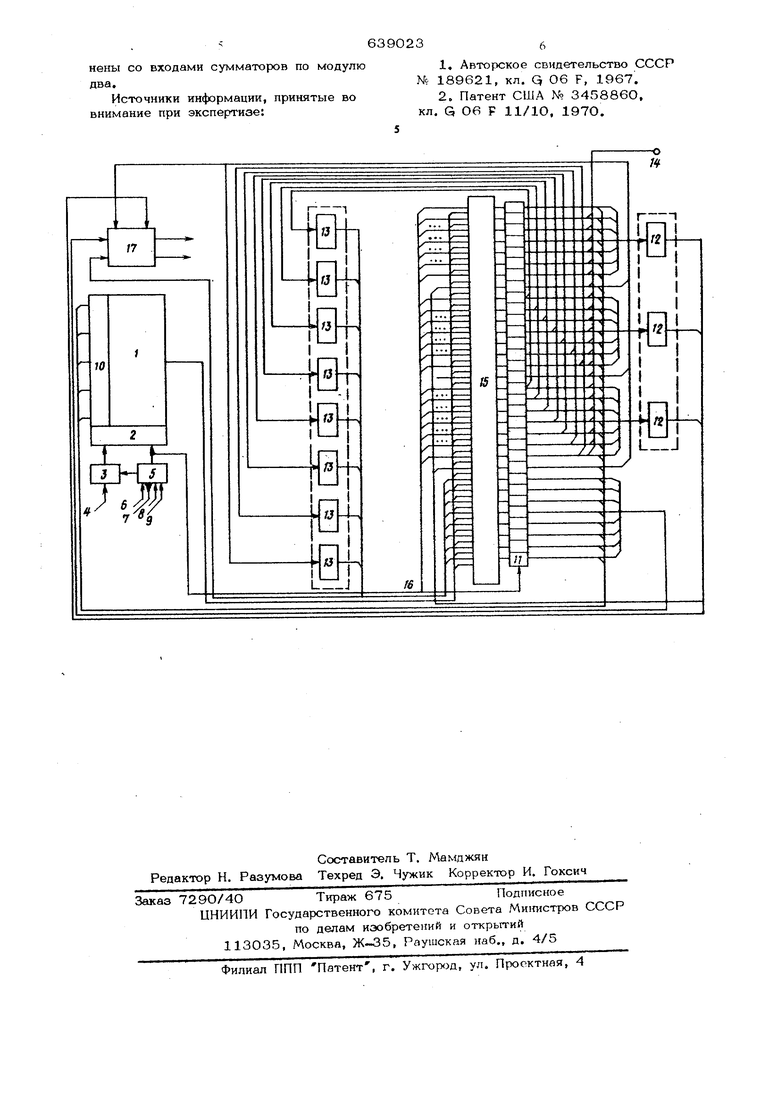

(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО вызванных отказами накопителя и разрядными цепями. Это достигается тем, что в устрюйств введены сумматоры по модулю два и элементы ИЛИ, первые входы которых соеди нены с входными информационными шинам вторые входы - с выходами сумматоров по модулю два и входами блока сравнения контрольных разрядов, а выходы подключены ко входам регистра слова, выходы которого соединены со входами сумматоров по модулю два. На чертеже дана структурная схема запоминающего устройства. Оно содержит адресный накопитель (Н) 1, к которому подключен через адрес ные цепи (АЦ) 2 блок 3 адресных цепей (БАЦ) с информационным входом (Л) 4 и блок 5 местного управления {БМУ} со входами 6 начало операции (НО) и выходом 7/конец операции (КО), 8 запись (3), 9 чтение (Ч). Кроме этого, накопитель 1 через разрядные цепи (РЦ) 1О соединен с регистром И слова (РС) который связан с сумматорами notnod Zll 12 И С сумматорами (Е2) 13. Выходы регистра 11 подключены к шине 14 выход информационного слова , а входы - к элементам ИЛИ 15, на который через шину 16 вход информационного слова подается информация. В регистре слова 11 есть контрольные разряды групповой четности (КРГЧ) и контрольные разряды веточной четности (КРВЧ). Выходы КРВЧ,КРГЧ Ш 12 и 312 13 соединены с блоком 17 сравне ния контрольных разрядов (БСКР). Запоминающее устройство работает следующим образом.В режиме записи на вход 16 поступает информационное слово,которое проходит через элементЬ ИЛИ 15 и записывается в информационных разрядах регистра слова 11. Информационные разряды регистра условно разделены на груп пы. Значения каждой из групп поступают на соответствующий сумматор по Kriod 12, где формируются значения контрольны разрядов Р групповой части четности (КРГЧ 1, КРГЧ2, КРГЧЗ). Значения четноети для каждой из групп разрядов через элеме ты ИЛИ 15 поступают в регистр 11. Одновременно значения j - х разрядов каж дой группы - поступают на соответствую щий -ый сумматор по ( 13. Значение бита четности для каждой j -ей ветви подается через элеменггы ИЛИ 15 в j -и разряд (KPBMj ) веточной четности. 23.; По сигналу с блока 5 местного управле- mtH осуществляется запись закодированного слова (кодового слова} через разрядные цепи Ю в ячейку 1 накопителя, номер которой задан кодом адреса на входе блока 3 адресных цепей. При считывании информации образование всех контрольных разрядов групповой четности и контрольные разряды веточной четности происходит аналогично, как и при записи, однако блок 5 управления блокирует запись этих разрядов с сумматоров 12 и 13 на регистр 11. Вновь образованные контрольные разряды групповой четности и веточной четности подаются в блок 17 сравнения, где осуществляется сравнение образованных контрольных разрядов, групповой четности и веточной четности с первоначальными значениями, которые были записаны в соответствующих разрядах регистра 11 при чтении из накопителя 1. При несовпадении считанных и вновь образованных контрольных разрядов групповой и веточной четности блок 17 выдает сигнал ошибка. Если не совпадают Р-контрольных разрядов веточной четности и один оС- разряд групповой четности ,то эта ситуация индицируется блоком 17 как пачка ошибок в ot -и группе разрядов, длина которых р. Таким образом, предложенное устройство позволяет обнаружить все одиночные ошибки, двойные, тройные и т.д. При семи информационных разрядах в группе и 3-х информационных группах одиночные двойные и тройные ошибки обнаруживаются с вероятностью 100%, а четырехкратные - с вероятностью 99,07%. Формула изобретения Запоминаиошее устройство, содержащее накопитель,информационные выходы которого соединены с информационными выходами регистра слова,а контрольные выходы последнего подключены к блоку сравнения контрольных разрядов, и входные информационные шины, отличающееся тем, что, с целью повышения надежности работы устройства, оно содержит сумматоры по юдулю два и элементы ИЛИ, первые входы которых соединены с входными информационными шинами, вторые входы с выходами сумматоров по модулю два и входами блока сравнения контрольных разрядов, а выходы подключены ко входам регистра слова, выходы которого соеди-

йены со входами сумматоров по модулю два.

Источники информации, принятые во внимание при экспертизе:

1,Авторское свидетельство СССР № 189621, кл. Q Об F, 1967.

2.Патент США N° 345886О, кл. (3 Об F 11/1О, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением и исправлением ошибок | 1978 |

|

SU763975A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1061176A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1092570A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Запоминающее устройство с обнаружением ошибок | 1985 |

|

SU1277215A1 |

13

13

п г

I

1г

т

f3

10

f3

7

15

1

4/3-4-IJ

а

Л

Авторы

Даты

1978-12-25—Публикация

1976-04-05—Подача